Mentor Graphics宣布其新的Mentor EZ-VIP PCI Express验证IP的即时可用性。这一新的验证IP (VIP)可将ASIC(应用程序特定集成电路)和FPGA(现场可编程门阵列)设计验证的测试平台构建时间减少多达10倍。

验证IP旨在通过为常见协议和架构提供可复用构建模块来帮助工程师减少构建测试平台所花费的时间。然而,即使是标准协议和常见架构,其配置和实施也可能会因设计而异。因此,传统的VIP元件可能需要数天甚至数周来准备模拟或仿真测试平台。

“在移动、网络及服务器SoC中使用ARMv8-A架构和ARM CoreLink高速缓存一致性互连进行设计时,我们的合作伙伴可以选择使用PCIe根联合体解决方案,”ARM系统和软件组总监Jim Wallace说,“ARM一直使用在Questa和Veloce上运行的Mentor PCIe VIP库来帮助验证PCIe与ARM AMBA接口域之间的关键交互,以实现快速部署和准确的协议检查。”

与传统的验证IP不同,Mentor的新PCIe EZ-VIP是“设计感知型”产品,可消除测试平台装配过程中的多个耗时步骤。这使验证工程师能够更快地配置和实施过去繁琐的设置任务,以直接产生高价值场景,从而将曾经需要数天或数周的过程减少到几个小时。

“我们很高兴与Mentor合作,为验证PCIe EZ-VIP提供支持,”PLDA的CTO Stephane Hauradou说,“成为第一批快速为ASIC和验证工程师开发并引进PCIe 3.0和PCIe 4.0控制器的提供商之一后,PLDA很高兴将通过硅验证的XpressRICH3和XpressRICH4 IP与PCIe EZ-VIP相结合,为ASIC项目团队提供一种可靠、可高度配置且易用的完整解决方案。”

“拥有易用且通过预先验证的PCIe验证IP对于我们的客户来说非常重要。我们一直与Mentor合作,帮助客户通过我们的Expresso 3.0核心验证其PCIe EZ-VIP,”Northwest Logic的董事长Brian Daellenbach说,“因此,客户可以将Mentor PCIe VIP与我们通过硅验证的PCI Express核心结合使用,来创建并验证其具有高可信度的设计。”

Mentor的PCIe EZ-VIP包含适用于PCIe 1.0、2.0、3.0、4.0和mPCIe的串行和并行接口的预封装且易用的验证环境,可用于验证PHY、Root Complex和Endpoint设计。测试计划、符合性测试、测试序列和协议覆盖范围都作为SV和XML源代码包含在内,从而允许简单复用、扩展和调试。Mentor VIP元件还包含一整套协议检查、错误注入和调试功能。

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

asic

+关注

关注

34文章

1199浏览量

120434 -

Mentor

+关注

关注

5文章

109浏览量

113836

发布评论请先 登录

相关推荐

KeyStone设备的PCI Express (PCle)常见问题

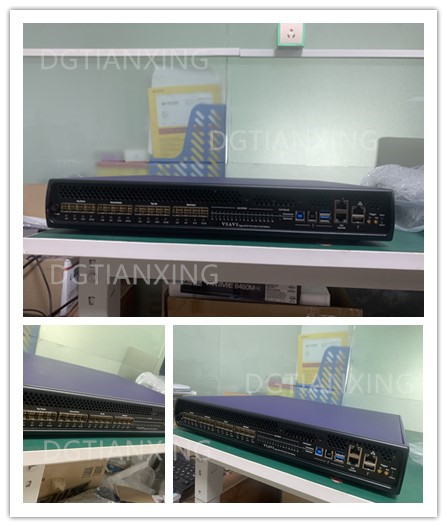

VIAVI Xgig 4K16 PCI Express 4.0 协议分析仪平台介绍

LMK6H和LMKDB1xxx PCI Express合规性报告

新思科技PCIe 7.0验证IP(VIP)的特性

DS50PCI401 2.5 Gbps/5.0 Gbps 4通道PCI Express中继器数据表

DS50PCI402 2.5 Gbps/5.0 Gbps 4通道PCI Express中继器数据表

XIO2001 PCI Express至PCI总线转换桥接器数据表

Mentor Graphics推出新的Mentor EZ-VIP PCI Express验证IP

Mentor Graphics推出新的Mentor EZ-VIP PCI Express验证IP

评论