Efinity目前不支持联合仿真,只能通过调用源文件仿真。

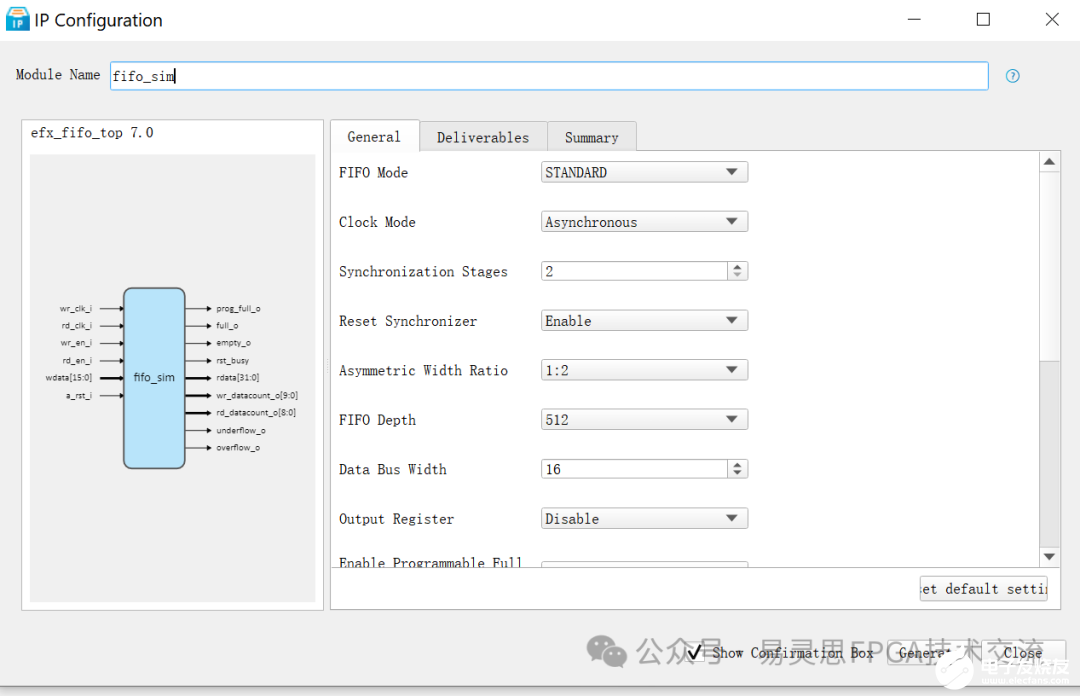

我们生成一个fifo IP命名为fifo_sim

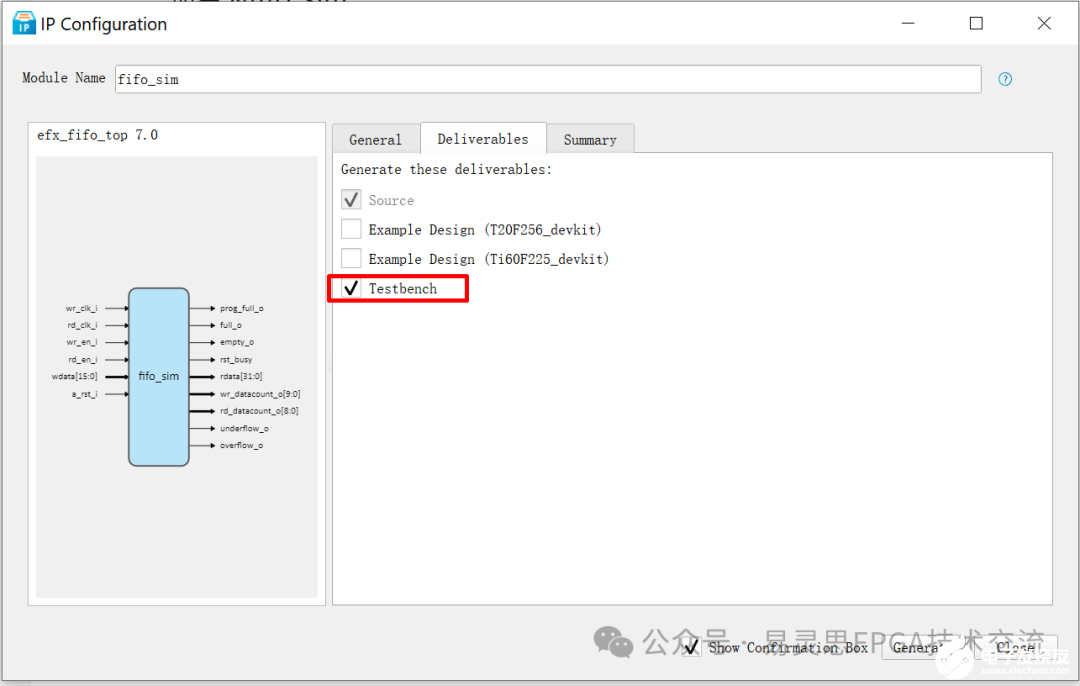

在Deliverables中保留Testbench的选项。

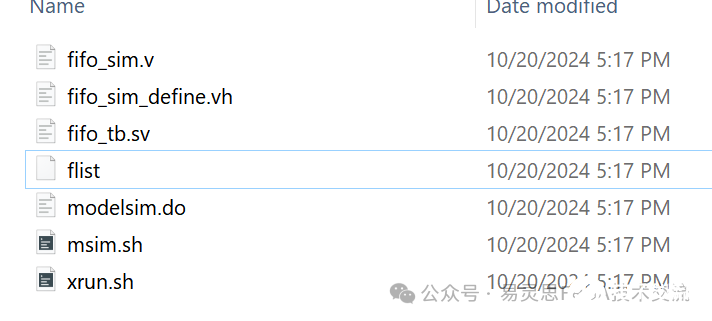

在IP的生成目录下会有以下几个文件

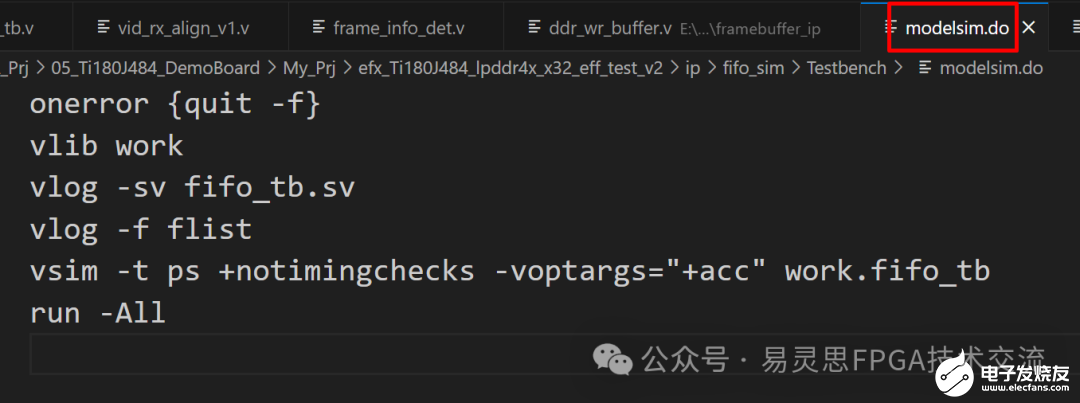

我们来看下modelsim.do文件,里面vlog了fifo_tb.sv文件,另外还调用了flist文件里的文件,flist只有一个文件那就是fifo_sim.v。所以这个仿真只使用了两个文件。

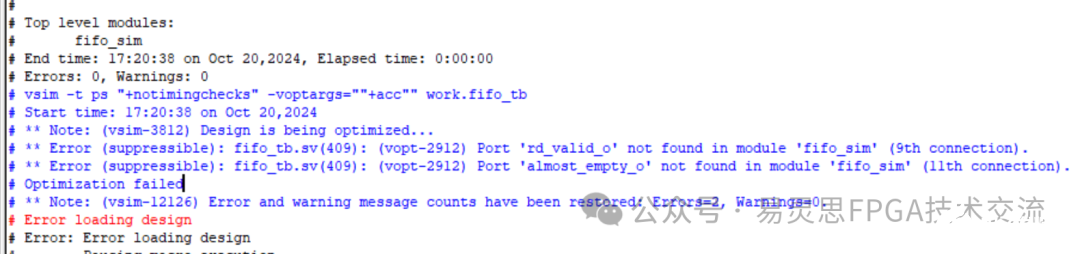

如果生成默认的IP或者自己的IP,目前FIFO的IP仿真可能会有一个错误 。提示在fifo_tb.sv的409行没有rd_valid_o和almost_empty_o

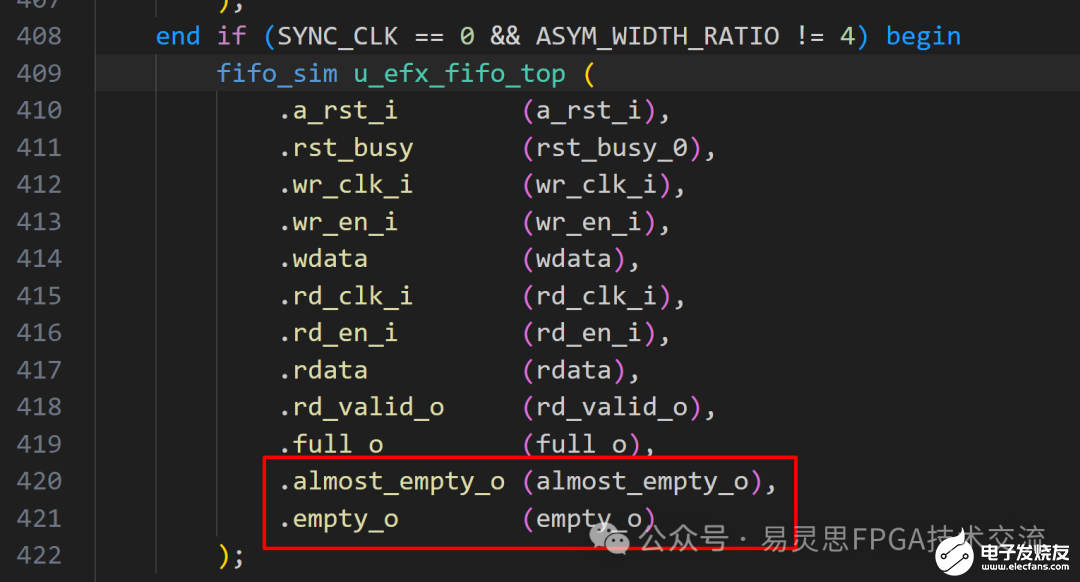

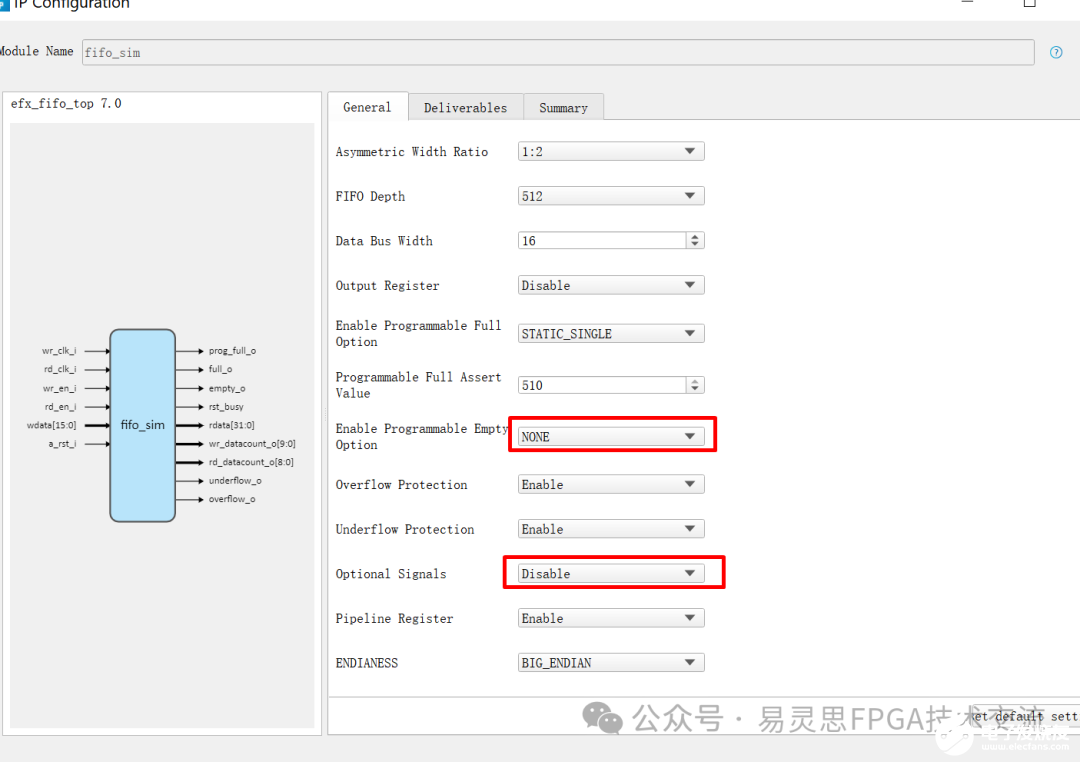

这是因为仿真文件只能仿真特定配置的IP,或者自带的仿真文件只适用于某些参数的设置。上面的问题是因为IP生成是没有打开Enable Programmbel Empty Option和Optional Signals两个选项。

我们需要打开这两个选项重新生成IP,注意重新生成IP时要关闭modeslim.

这里在把modelsim的路径转向文件所在的路径,比如我的路径如下:

cd E:/FPGA_Prj//ip/fifo_sim/Testbench/

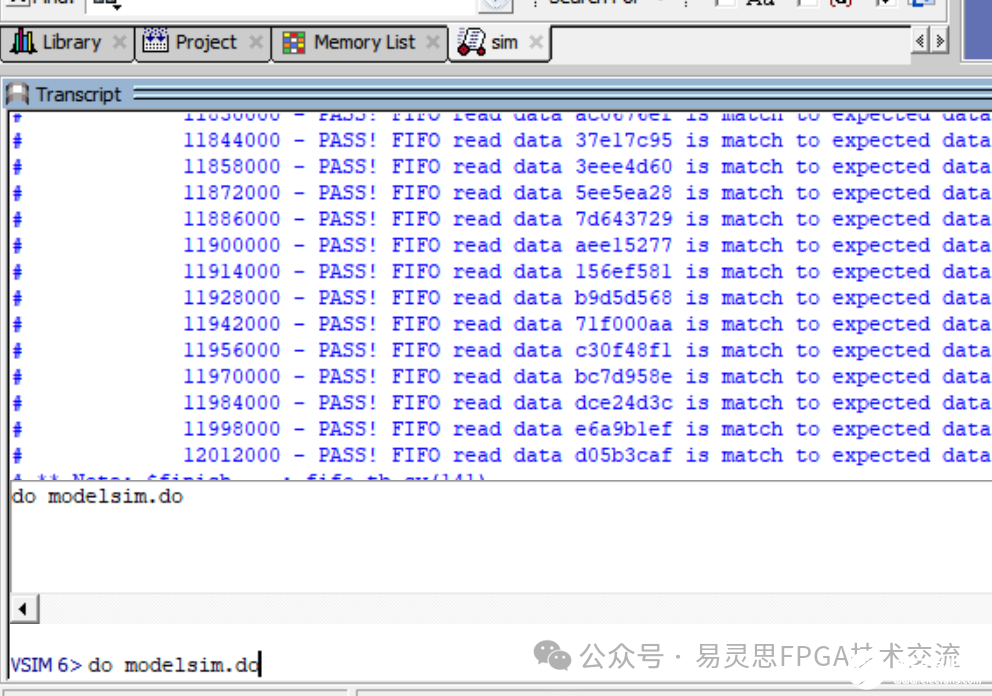

然后执行do modelsim.do即可以仿真。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

IP

+关注

关注

5文章

1893浏览量

156964 -

仿真

+关注

关注

55文章

4561浏览量

138801 -

fifo

+关注

关注

3文章

407浏览量

45953

发布评论请先 登录

相关推荐

热点推荐

Freescale V1 ColdFire处理器

Freescale V1 ColdFire处理器,在Cyclone III FPGA上通过FPGA结构来实现V1 ColdFire内核,拓展了ColdFire在新领域的应用优势

发表于 11-30 16:39

•4253次阅读

Arm Neoverse V1 PMU指南

本文档描述了不同性能监视器单元(PMU)事件的行为在Neoverse V1。

Neoverse V1有六个可编程的32位计数器(计数器0-5),每个计数器计数器可以编程为在本文档中描述的PMU

发表于 08-09 07:30

XILINX FPGA IP之FIFO Generator例化仿真

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该

Efinity Interface Designer报错案例-v1

to efx_pnr... 原因:(1)有些客户使用Win7版本,目前Efinity对Win7的支持不好。建议升级成win10。 (2)杀毒软件删除了文件,实际interface生成约束是没有问题的,客户pnr的时候

Efinity debugeri常见问题总结-v1

(1)UUID mismatch Efinity在Debug时会出现UUID mismatch错误。很多刚开始使用的人经常遇到。下面我们做一个总结。欢迎遇到案例时共同分享。 一般有以下几种原因 (1

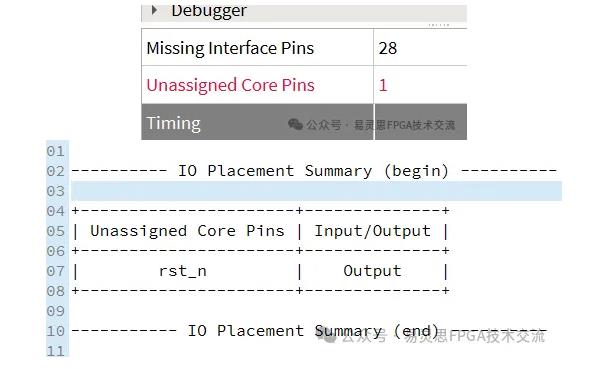

Efinity编译生成文件使用指导-v1

接上篇: (6)查看Unassigned Core Pins。 在placement下面的palce.rpt文件中搜索 Unassigned C ore Pins就可以看到。它说明这些管脚没有用于内部连接。 大家可以点击这个链接查看上文 Efinity编译生成文件使用指导

Efinity FIFO IP仿真问题 -v1

Efinity FIFO IP仿真问题 -v1

评论