RS触发器(Reset-Set触发器)是一种基本的数字逻辑电路,用于存储一位二进制信息。它由两个输入端(R和S)和一个输出端(Q)组成,其中R代表复位(Reset),S代表置位(Set)。RS触发器的逻辑功能和触发方式如下:

逻辑功能

RS触发器的逻辑功能可以通过真值表来描述。真值表如下:

| R | S | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | X | Q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | X | 0 |

- Q(t) 表示当前状态,Q(t+1) 表示下一个状态。

- X 表示不稳定状态,即触发器在这种输入下不能保持稳定。

从真值表可以看出:

- 当R=0且S=0时,触发器保持当前状态(Q)不变。

- 当R=0且S=1时,触发器置位,即Q变为1。

- 当R=1且S=0时,触发器复位,即Q变为0。

- 当R=1且S=1时,触发器处于不稳定状态,输出Q将被强制为0。

触发方式

RS触发器的触发方式主要有两种:同步触发和异步触发。

1. 同步触发(Synchronous Triggering)

在同步触发方式下,触发器的输出状态变化仅在时钟信号(CLK)的上升沿或下降沿发生。这种触发方式可以减少由于输入信号的毛刺或噪声引起的误触发。

同步RS触发器的逻辑电路通常包括一个时钟输入端,以及一些额外的逻辑门来确保只有在时钟信号的边沿时才更新输出状态。同步触发器的真值表如下:

| R | S | CLK | Q(t) | Q(t+1) |

|---|---|---|---|---|

| 0 | 0 | X | X | Q |

| 0 | 1 | X | 0 | 1 |

| 1 | 0 | X | 1 | 0 |

| 1 | 1 | X | X | 0 |

2. 异步触发(Asynchronous Triggering)

在异步触发方式下,触发器的输出状态可以在任何时候由输入信号R和S的变化来改变,而不需要等待时钟信号。这种触发方式可能会导致由于输入信号的毛刺或噪声引起的误触发。

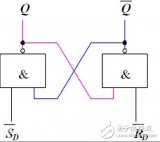

异步RS触发器的逻辑电路比较简单,通常只包括基本的与非门或或非门来实现逻辑功能。异步触发器的真值表与上述逻辑功能相同。

应用

RS触发器在数字电路中有广泛的应用,包括但不限于:

设计考虑

在设计RS触发器时,需要考虑以下因素:

- 稳定性 :确保触发器在所有输入条件下都能稳定工作。

- 抗干扰能力 :设计时钟信号和输入信号的去毛刺电路,以减少误触发。

- 功耗 :在低功耗设计中,需要考虑触发器的功耗。

- 速度 :在高速电路中,需要考虑触发器的响应时间。

-

二进制

+关注

关注

2文章

796浏览量

41746 -

RS触发器

+关注

关注

3文章

101浏览量

18031 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15866 -

逻辑功能

+关注

关注

0文章

14浏览量

3127

发布评论请先 登录

相关推荐

RS触发器工作原理_RS触发器逻辑功能_RS触发器和SR触发器的区别

rs触发器的逻辑功能和触发方式

rs触发器的逻辑功能和触发方式

评论