Hi,我是小杜。PCIe作为高速传输总线,使用差分信号线传输数据,支持多通道链路。但由于设计需求和布局限制,可能需要在设备之间或主板上调整PCIe通道走向,因此可能会产生信号极性和通道顺序的问题,如处理不当会造成数据解析错误、损害信号质量等后果。PCIe规范考虑到这一点,提出了通道极性翻转和通道顺序翻转的解决方案,小杜来讲一下此过程。小杜经验尚浅,如有错误,还请批评指正。

信号极性翻转

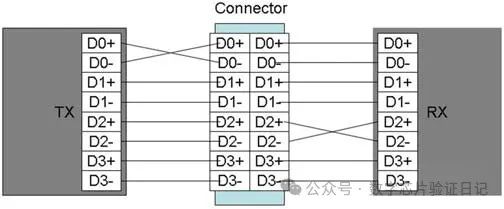

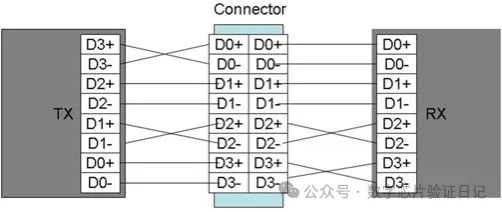

PCIe使用差分信号对来传输数据,即通过两根电气线传输,每根线携带相同的信号,但电压极性相反,称为正极(D+)和负极(D-)。通常发射端的D+直接连接到接收器的D+,D-同理。如下图所示,发射端Tx,中间连接器Connector和接收端Rx的D+、D-一一对应。

但由于布局布线等原因,Tx的D+可能和接受端的D-连接。对于Rx来说,它们并不知道和对端的电气线具体是如何连接的,正负极接反会导致Rx解析出相反的数据,比如1010解析为0101(所有bit都相反)。

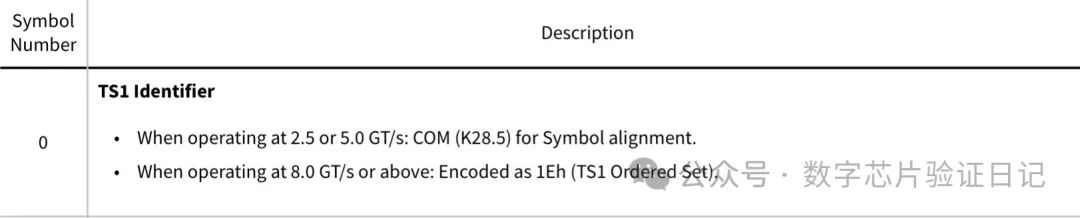

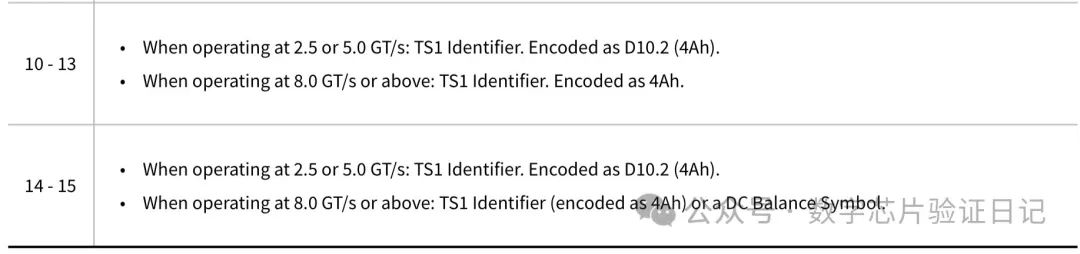

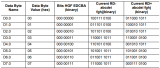

PCIe协议考虑到了这一点,提供了在训练阶段各通道Rx自动识别并调整其极性的方法。当链路训练进入到Polling阶段时,Rx可以通过识别TS1 OS的TS1 OS Identifier Symbol(TS1 OS识别符)来判断通道当前极性,以Symbol 10到15为例,当识别到4Ah(0100_1010)时表示通道极性正常,当识别到B5h(1011_0101)时则表明D+接到了D-上,此时Rx需要自动按相反极性解析收到的数据。只有当链路所有的通道都正确地受到4Ah后才会进一步解析训练序列中携带的信息。

通道位置翻转

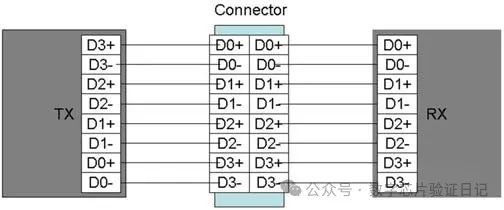

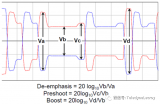

考虑另一种情况,如果Tx端从上到下是Lane3 ~ Lane0,而Rx端是Lane0~Lane3,这种情况称为通道位置反转,此时#Lane0的引脚会接到#Lane3的引脚上。由于TLP和DLLP的传输对通道顺序有要求,比如STP和SDP必须放置在Lane0,因此链路训练时一侧需要根据各Lane受到的训练序列来翻转其通道顺序,以实现Tx和Rx的通道顺序匹配,当通道顺序翻转时需要翻转所有通道。

一些PCIe金手指有防呆口设计,可以避免通道顺序翻转的情况,但对于焊在主板上的PCIe芯片,可能会出现两端通道顺序相反的情况。如果不进行通道位置翻转,就需要使用PCB导孔换层来解决,这会降低高速信号质量,所以推荐PCIe设备支持通道位置翻转功能。

当然,信号极性翻转和通道顺序翻转可能会同时出现,如下图所示,Tx/Connector/Rx之间通道顺序相反,4条Lane的极性也相反。

通过上述说明可以看出即使出现了通道极性和顺序的问题,PCIe链路训练也可以自动完成通道间的匹配,这通常对用户来说是无感的。只有确保各通道连接正确,才能正常解析数据,继续后续的链路训练步骤。感谢你耐心地看到这里。

-

信号

+关注

关注

11文章

2789浏览量

76730 -

总线

+关注

关注

10文章

2878浏览量

88051 -

PCIe

+关注

关注

15文章

1234浏览量

82577 -

负极

+关注

关注

0文章

66浏览量

9460

原文标题:【PCIe】链路训练 - 通道极性和顺序翻转

文章出处:【微信号:小杜的芯片验证日记,微信公众号:小杜的芯片验证日记】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用于 PCIe Gen-3 卡的高速前端参考设计

基于 PCIE 总线的 4 路 10G 双缓冲光纤通道适配器

可提高信号完整性和系统稳健性PCIe Gen-3高速前端卡设计包括BOM,PCB文件及光绘文件

AC701能否通过Artix 7的PCIe链路与PC通信?

PCIe 3.0/4.0的链路均衡的工作原理

PCIe Gen-3高速前端卡参考设计

体验紫光PCIE之使用WinDriver驱动紫光PCIE

[PCIe] [电源管理] 面向硬件的ASPM链路状态和L1子状态

![[<b class='flag-5'>PCIe</b>] [电源管理] 面向硬件的ASPM<b class='flag-5'>链</b><b class='flag-5'>路</b>状态和L1子状态](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

[PCIe] [电源管理] 面向硬件的ASPM链路状态和L1子状态

![[<b class='flag-5'>PCIe</b>] [电源管理] 面向硬件的ASPM<b class='flag-5'>链</b><b class='flag-5'>路</b>状态和L1子状态](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

PCIe链路训练之通道极性和顺序翻转

PCIe链路训练之通道极性和顺序翻转

评论