一、概述

芯片压降的管理是确保集成电路(IC)稳定运行的关键,涉及单板(PCB)、封装、芯片内部等多个层面。具体的推荐指标数据因应用领域、工艺节点、芯片类型等不同而有所差异,但以下是一些通用的指导原则和参考指标:

1.单板(PCB)层面

•电源层和地层的电阻: 目标通常是小于1mΩ/square(平方英寸),具体数值根据电流密度和应用要求而定。

•去耦电容布置: 通常推荐每1平方英寸的逻辑区域至少配置10uF的去耦电容,高频应用中还需增加陶瓷电容(如0.1uF或1nF)来处理高频瞬态电流。

•电压波动: 动态电压波动(ΔV)目标应小于电源电压的5%,例如在3.3V电源下,ΔV应小于0.165V。

2.封装(Package)层面

•封装引脚电阻: 封装引脚的电阻(或封装阻抗)应控制在几毫欧姆(mΩ)范围内,具体数值依据封装类型和设计要求。

•封装电感: 封装内和封装到PCB的电感应尽量低,理想情况下封装内电感小于1nH,以减少高频时的电压尖峰。

•热阻: 封装的热阻(θjc)影响芯片的散热,对于高性能应用,热阻应低于10°C/W。

3.芯片内部

•电源网格电阻: 芯片内部电源网格的电阻应保持在纳欧姆级别(nΩ),以确保在整个芯片上电压降保持在最低。

•最大允许压降: 一般认为芯片内部的最大允许压降不应超过电源电压的5%,一般 建议控制再3%以内,确保逻辑门的阈值电压不会受到影响,维持电路的稳定工作。

•电迁移限制: 为了防止电迁移现象,局部电流密度通常不应超过几百万安培/平方厘米(A/cm²),具体数值根据工艺节点和材料属性而定。

综合策略

•仿真验证: 在设计过程中,使用如Sigrity、Ansys等仿真软件对全链路进行IR Drop仿真,确保在最坏情况下也能满足上述指标。

•动态测试: 实际产品在完成设计后,进行动态测试,验证在各种工作条件下的电压稳定性,确保设计符合预期。

请注意,这些数据是基于一般性建议,具体项目应依据实际设计需求、工艺能力、以及性能目标进行详细评估和调整。

二、die内IR drop分析

芯片die内IR drop(电压降)分析是半导体设计中的一个重要环节,它直接关系到芯片的性能和可靠性。在集成电路(IC)内部,电流通过电源网络(power grid)时,由于网络的电阻(R)和电流(I)的乘积效应,会导致电压下降。以下是对芯片die内IR drop分析的几个关键步骤和考虑因素:

1.模型建立

•物理模型构建:首先,需要建立芯片die的物理模型,包括电源线、地线、晶体管、电容等元素的布局和尺寸,以及它们之间的电气连接关系。

•电阻网络模型:将电源网络简化为一个电阻网络模型,通过计算不同金属层、通孔和连线的电阻值来评估整个网络的电阻分布。

2.电流分布分析

•静态电流分析:计算芯片在无活动时的静态电流分布,这通常基于设计的静态功耗。

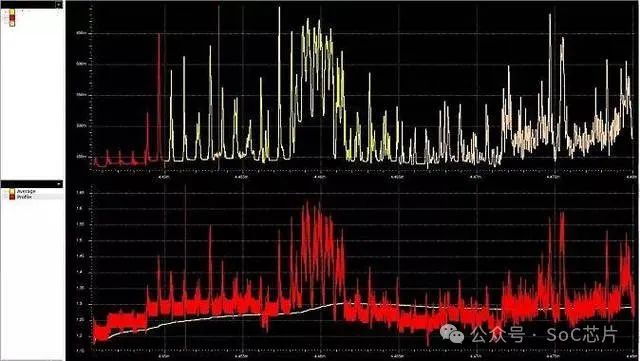

•动态电流分析:采用仿真工具(如SPICE)模拟芯片在不同操作状态下的动态电流行为,考虑信号翻转、时钟活动等因素对电流分布的影响。

3.电压降仿真

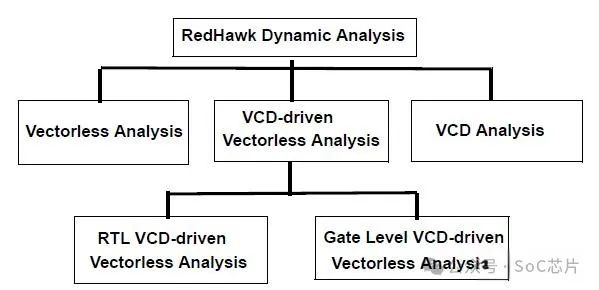

•静态IR drop仿真:基于静态电流分布计算电源网络的电压降,评估在无时序约束下的电压稳定性。

•动态IR drop仿真:考虑瞬时电流变化对电压的影响,仿真在各种工作模式下,特别是高负载时的电压波动情况。

4.关键区域识别

•热点分析:通过仿真结果识别电压降最大的区域,这些通常是电流密度高或电源网络电阻较大的地方。

•时序分析:评估电压降对电路时序路径的影响,包括setup和hold时间,确保时序收敛。

5.优化策略

•电源网格改进:优化电源和地网的布局,增加金属层,使用更大截面的金属线以降低电阻。

•去耦电容优化:在关键区域布局去耦电容,吸收瞬间电流尖峰,减少电压波动。

•电流均衡:调整电路设计,尽可能平衡电流分布,避免局部过热和电压突降。

6.验证与签核

•IR drop签核:确保在所有预期工作条件下,电压降满足设计规范,不会导致电路功能错误。

•EMC/热分析:同时考虑电磁兼容性和热管理,确保芯片在高功率操作下的稳定性和可靠性。

7.迭代优化

•设计迭代:基于仿真和分析结果,对设计进行调整,再次进行仿真验证,直至所有指标满足要求。

总之,芯片die内IR drop分析是一个迭代、复杂的过程,需要综合考虑设计、仿真、优化和验证的各个方面,以确保芯片在实际应用中能够稳定、高效地工作。随着半导体工艺的进步和设计复杂性的增加,这一过程变得越来越重要,同时也是提升芯片性能和降低功耗的关键步骤。

三、封装IR drop分析

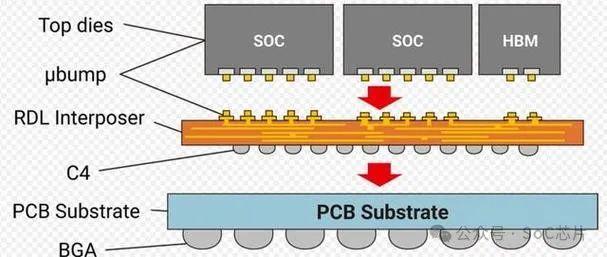

芯片封装中的IR drop(电压降)分析是一个复杂而重要的过程,它涉及评估封装内部的电压损耗,确保芯片在封装后能够正常工作,不受电源波动的影响。封装级的IR drop分析主要关注于从外部电源到芯片内部的电源传输路径中的电压损耗。以下是进行封装IR drop分析的关键步骤和考虑因素:

1.封装模型构建

•物理模型:首先,需要构建一个精确的封装模型,包括封装材料(如基板、引线框架)、封装内电源线和地线、焊点(如Flip Chip下的凸点或Wire Bond的线)的电阻值和电感值。

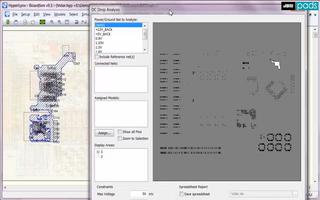

•电气模型:使用三维电磁场仿真软件(如ANSYS HFSS,Cadence Sigrity等)建立封装的电气模型,模拟不同频率下的电流流动和电场分布。

2.电流分布分析

•提取电流波形:根据芯片的功耗分布和工作模式,提取不同工况下的电流波形,包括峰值电流、平均电流和瞬态电流变化。

•封装内电流路径:分析电流如何通过封装的各个部分,包括引脚、衬底、封装内互连等,以识别潜在的高电阻或高电感区域。

3.IR drop仿真

•静态分析:进行静态IR drop仿真,评估在固定电流条件下的电压降,确保在整个封装上电压分布均匀。

•动态分析:执行动态仿真,考虑瞬态电流效应,评估在开关操作和高负载状态下电压波动的程度,这对于高速信号和敏感电路尤为重要。

4.热效应考虑

•热分析:封装的温度上升会导致电阻增加,进而影响IR drop。因此,进行热分析,将温度影响纳入IR drop仿真,确保分析结果的准确性。

5.优化与改进

•设计优化:基于仿真结果,优化封装设计,如增加或优化去耦电容布局、改善电源线和地线结构、选用低电阻材料等,以减少IR drop。

•电源分配策略:考虑使用多电源引脚、优化电源分配网络(PDN)设计,确保电源稳定供给。

6.验证与签核

•签核标准:根据行业标准和具体应用要求,设定IR drop的允许范围,确保芯片在封装后的性能和可靠性。

•后封装测试:在实际封装样品上进行测试,验证仿真结果,必要时进行调整。

7.系统级考虑

•与PCB协同优化:封装的IR drop分析不能孤立进行,需要与PCB的电源分配网络设计协同考虑,确保整个系统层面的电源完整性。

通过上述步骤,可以有效地分析和管理芯片封装中的IR drop,保证芯片在封装后的性能表现,减少因电源波动导致的功能故障和可靠性问题。

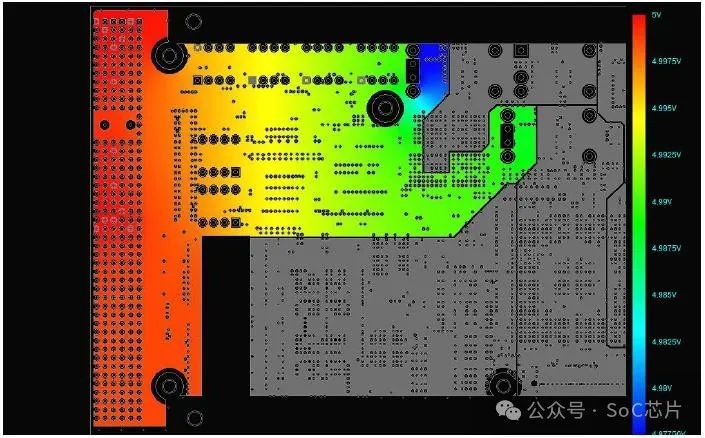

四、PCB单板IR drop分析

PCB(Printed CircuitBoard,印刷电路板)单板上的IR drop(电压降)分析是确保电子设备稳定运行的关键环节,它评估了电流通过PCB电源网络时因电阻效应引起的电压损失。以下是进行PCB单板IR drop分析的主要步骤和考虑因素:

1.建模与准备

•电源网络建模:使用EDA(Electronic Design Automation)工具如CadenceAllegro、Mentor Graphics HyperLynx或Altium Designer等,建立PCB的电源网络模型。这包括电源平面、地平面、电源轨、去耦电容和连接这些部件的走线。

•电流需求分析:根据电路设计,估算不同工作模式下各个部分的电流消耗。这可能涉及静态电流分析(DC)和动态电流分析(AC),考虑时钟速度、信号翻转率等因素。

2.仿真设置

•设置仿真参数:在仿真软件中输入电源电压、电流波形、环境温度等参数,确保仿真条件贴近实际工作环境。

•确定仿真范围:选择仿真时间窗口和感兴趣的频率范围,以捕捉瞬态和稳态行为。

3.IR drop仿真

•静态IR drop分析:在无信号变化的情况下,计算电源网络的电压降,确保在静态条件下的电压稳定。

•动态IR drop分析:模拟电路在不同操作模式下的瞬态电流变化,评估电压波动,特别是对于高速信号和高功耗元件。

4.结果分析

•热点识别:分析仿真结果,识别电压降最大的区域,这些通常是电流密度高或电阻较大的区域。

•时序分析:评估电压降对信号完整性的影响,包括是否导致时序违例(如setup和hold时间)。

5.优化与调整

•电源平面优化:通过增加电源平面的铜厚度、优化平面布局、减少分割,降低电源网络的总电阻。

•去耦电容优化:合理布局去耦电容,特别是靠近高功耗元件,以快速响应瞬态电流需求,减少电压波动。

•走线和过孔优化:优化电源和信号走线的宽度、长度,减少过孔数量,以降低电阻和感抗。

6.验证与迭代

•设计迭代:根据仿真和分析结果,对PCB设计进行必要的修改,然后重复仿真和分析过程,直到所有关键区域的IR drop满足设计规范。

•物理测试:在最终设计阶段,可能还需要进行实际的测试验证,确保仿真结果与实际情况相符。

通过上述步骤,可以有效管理和降低PCB单板上的IR drop,提高电子产品的稳定性和可靠性,确保其在各种工作条件下的性能表现。

-

芯片

+关注

关注

463文章

54601浏览量

470678 -

集成电路

+关注

关注

5469文章

12732浏览量

376166 -

封装

+关注

关注

128文章

9374浏览量

149182 -

去耦电容

+关注

关注

12文章

326浏览量

23630

原文标题:SoC芯片设计系列---芯片工作全链路压降分析

文章出处:【微信号:gh_9d9a609c9302,微信公众号:SoC芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片工作全链路压降分析

芯片工作全链路压降分析

评论