INNOVUS/ICC2吐出的netlist经过Formal/LEC验证后,Star-RC/QRC抽取RC寄生参数文件并读入到Tempus/PT分别做func/mbist/scan时序sign-off,写出SDF3.0用以后仿真,搭建后仿真的验证环境,添加sc/io/macro的verilog model,仿真输出VCD给Redhawk/Voltus做功耗/IR Drop分析。本文简要叙述下后仿真要点:

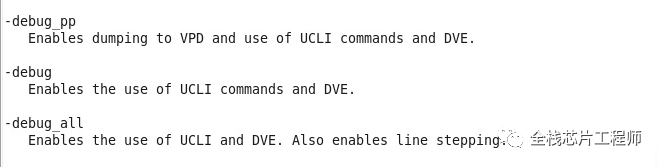

-debug选项,为了导出VPD通常选择-debug_pp;

-R表示编译之后立即运行仿真;

-gui表示在仿真0时刻打开DVE界面;

-l表示记录编译过程日志,后跟日志文件名;

+incdir+表示文件搜索路径;

+v2k表示支持verilog 2001标准;

-top设置编译顶层模块,后跟顶层module名,不是文件名;

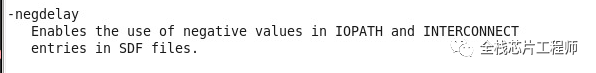

-negdelay

SDF文件中有负延迟时,若不加-negdelay会出现SDF Error: SDF Error: NegativeDELAY ignored and replaced by 0.

即VCS将负延时忽略,用0取代负值。加参数-negdelay 可消除负延迟导致的error,变成warning,但最终都不影响设计。

SDF Warning:Negative IOPATH DELAY A to Y ignored.

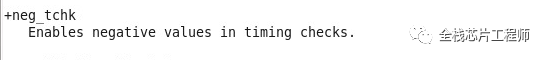

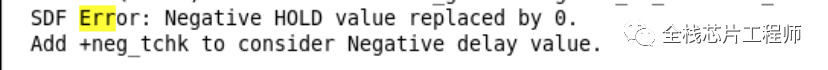

+neg_tchk支持负延迟检查,主要是检查holdtime,否则反标中会把负值忽略为0

标准单元库文件有两种,譬如tsmc18_neg和tsmc18,前者支持neg_tchk负延时检查,后者不支持。因为hold time check的值是负的,所以要进行negative timingcheck,否则默认将会使负值的hold time check改为0。为了满足对hold time负值的检查,在vcs仿真时需加上+neg_tchk这个option。

如果不加的话会产生下面的问题:

+maxdelays用SDF文件中的延迟,取代仿真库中的延时(仿真库中通常是建立时间1ns,保持时间0.5ns),取SDF文件中的最大延迟;

+mindelays用SDF文件中的延迟,取代仿真库中的延时,取SDF文件中的最小延迟(保持时间检查);

实际上,我们会出ss、ff、tt等数个sdf,每个sdf里面都只有类似{max::max}形式,因此,每个sdf只对应一种ss或ff形式的延时反标。

+sdfverbose显示所有的sdf反标错误

+no_notifier关闭时序检查函数中的不定态生成传播,即通过这个参数,如果有时序违规,控制台会报告,但不会影响逻辑功能的正确输出。

+nospecify 消除所有延迟,只做网表的功能仿真可以用;

+notimingchecks只是消除延迟违规断言,避免输出不定态,但延迟还在。因此+nospecify的作用包括了+notimingchecks;

注意:+nospecify,加上该选项之后,所有的线延迟以及标准单元verilog文件中的固有延迟都没有了,如果只是单纯的不加sdf文件的话,标准单元verilog文件中的specify延迟还是有的。

+delay_mode_zero: Change all the delay specifications on all gates,switches, and continuous assignments to zero and change all module path delays to zero.

-

芯片

+关注

关注

456文章

51157浏览量

427072 -

仿真

+关注

关注

50文章

4124浏览量

133957 -

函数

+关注

关注

3文章

4345浏览量

62953 -

编译

+关注

关注

0文章

661浏览量

33034

原文标题:芯片后仿(一)

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文掌握集成电路封装热仿真要点

STM32F4系列有对PI/SI仿真要求的文件吗?

proteus 7可以仿真msp430f249吗?哪位大神可以帮我解释一下,msp430f249仿真要用哪个版本?感谢

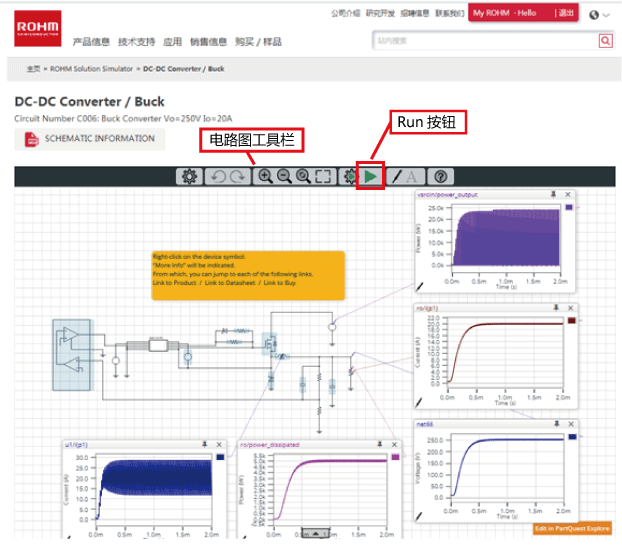

仿真-ROHM Solution Simulator 仿真的执行

芯片后仿真要点

芯片后仿真要点

评论