以下文章来源于慧智微电子,作者小慧

01

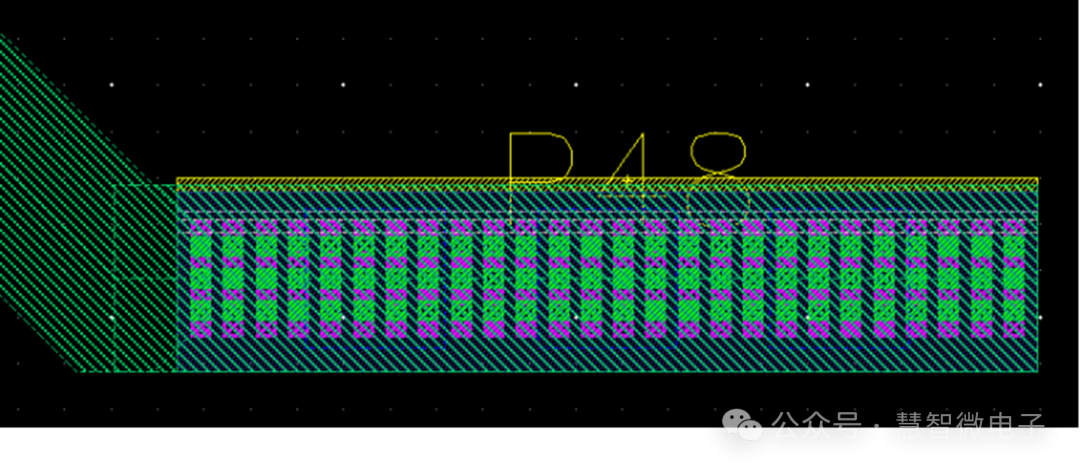

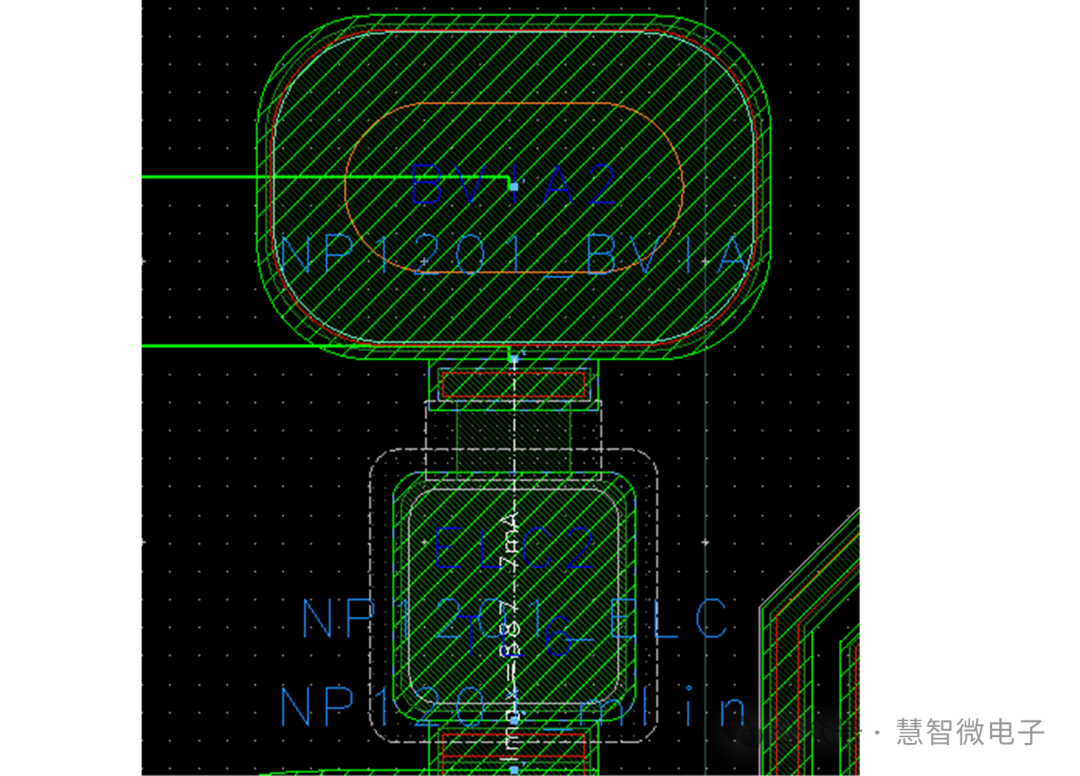

Q:请问在Cadence的EMX仿真里,如果需要在一个较长的边打PORT,需要怎么设置会仿真比较精准?像这样子直接吸附一个上去可以吗?

A:你这不是label吗?

Q:对,就是打label然后跑EMX。

A:是不是搞个传输线跑一下看看行不行就知道了。

A:可以,最好打到边沿,没达到边沿会自动选个最近的边沿。

Q:好的,谢谢大佬。

A:不过你可以估一下这个边沿的长度和波长的关系。

Q:好的(•̤̀ᵕ•̤́๑)ᵒᵏᵎᵎᵎᵎ,不过这个频率下对应波长有5mm,应该不太会影响。

A:嗯嗯,这种2.5D的电磁好像要注意一下如果有长边注入信号可能会不准,和算法的一些假设近似有关。

02

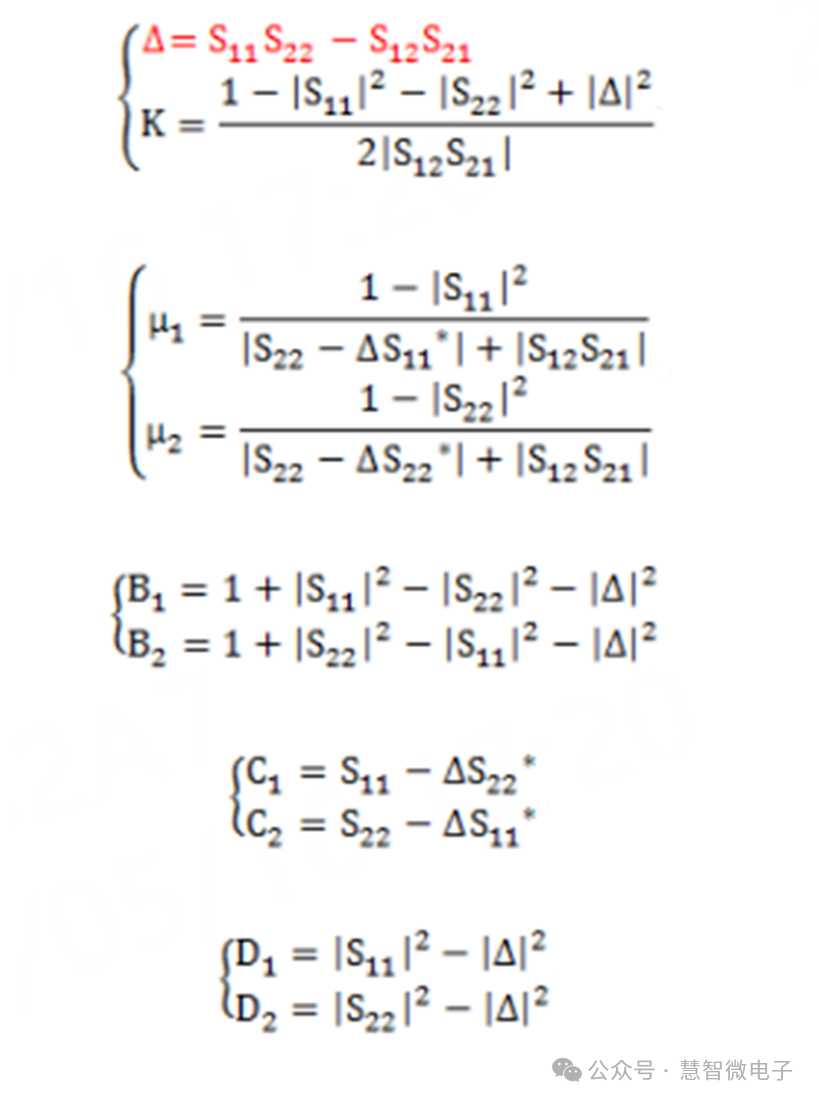

请问s参数可以计算稳定性μ吗?

Q:请问s参数可以计算稳定性μ吗?我测试得到S参数dB值。

A:可以,测试时导出为复数形式,然后放入maltab里面用矩阵计算。

就按照这个计算就可以。

Q:我测试数据只有dB,是不是就没用了。

A:你看下保存数据格式,是不是有幅度与相位,有的话应该可以,都是从网分导出数据,大不了再导出一次。

Q:好的,多谢大侠。

03

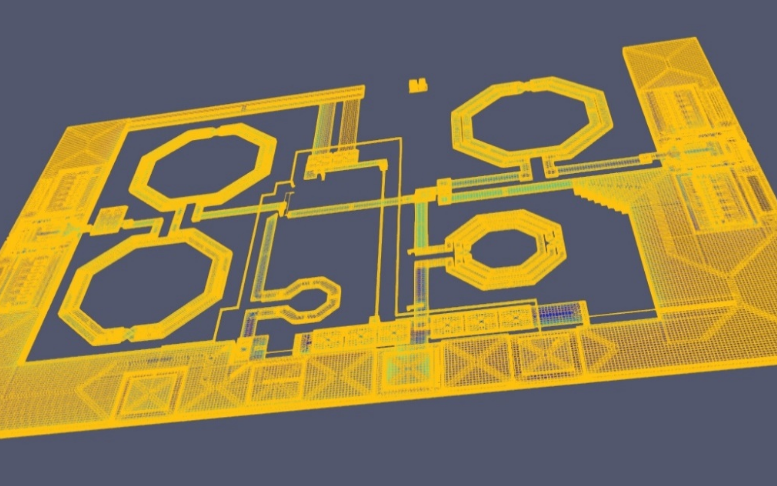

有关Virtuoso中变压器EMX仿真snp文件导出与多圈仿真问题的讨论

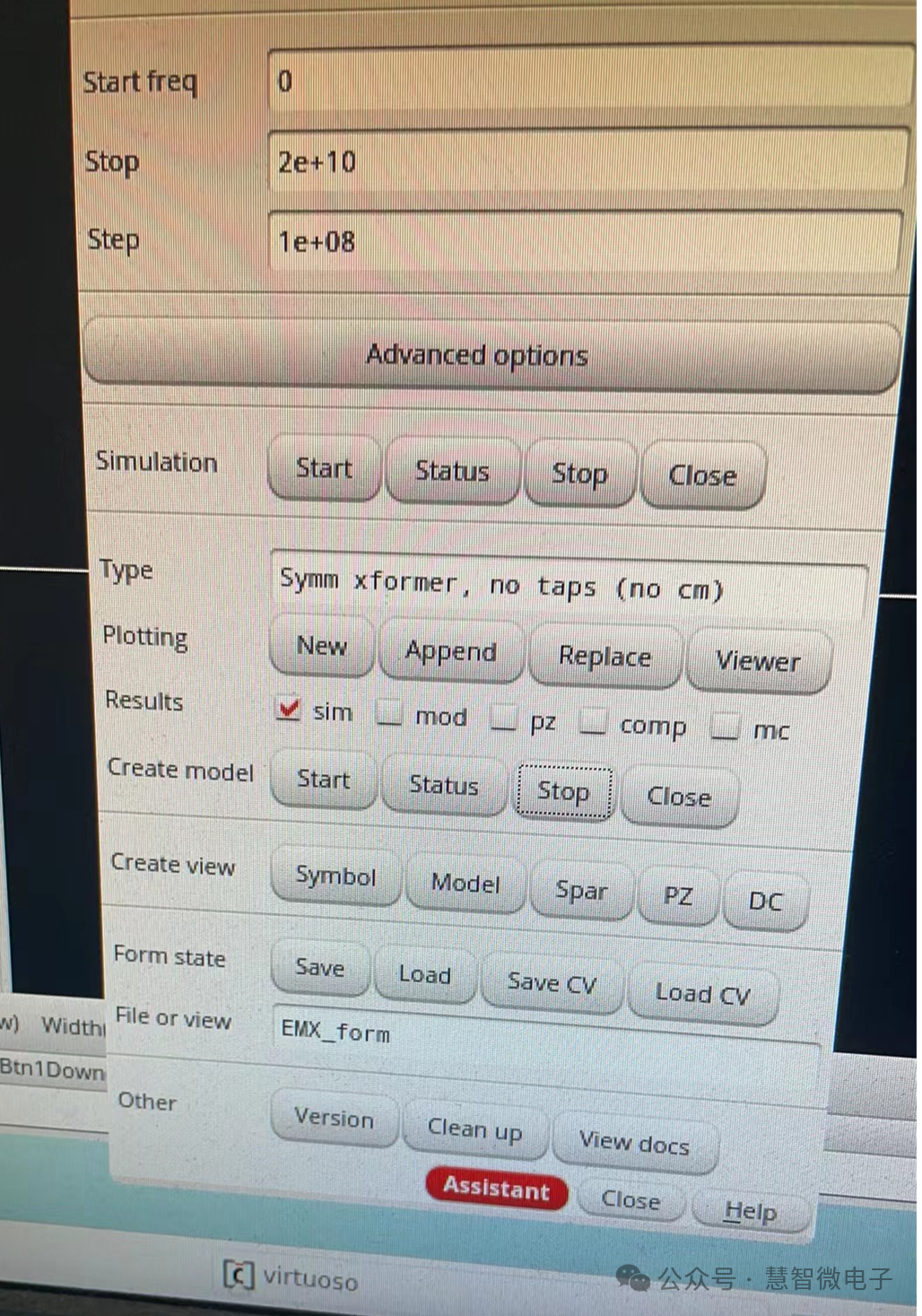

Q:请问在layout中画好了变压器,经过了emx仿真,怎么导出snp文件,重新放进原理图仿真呢?在virtuoso里面。

A:下面不是有CREATE吗,下面create点Spar生成s参数的nport,再打包成symbol就好。

Q:谢谢,再请教一下,如果变压器是两个主圈和一个次圈绕在一起的,但是emx每次只能仿真其中一个主圈和次圈的耦合结果,不能同时看两个主圈和一个次圈的结果。这样生成的snp文件应该是不准确的吧?忽略了另一个主圈。

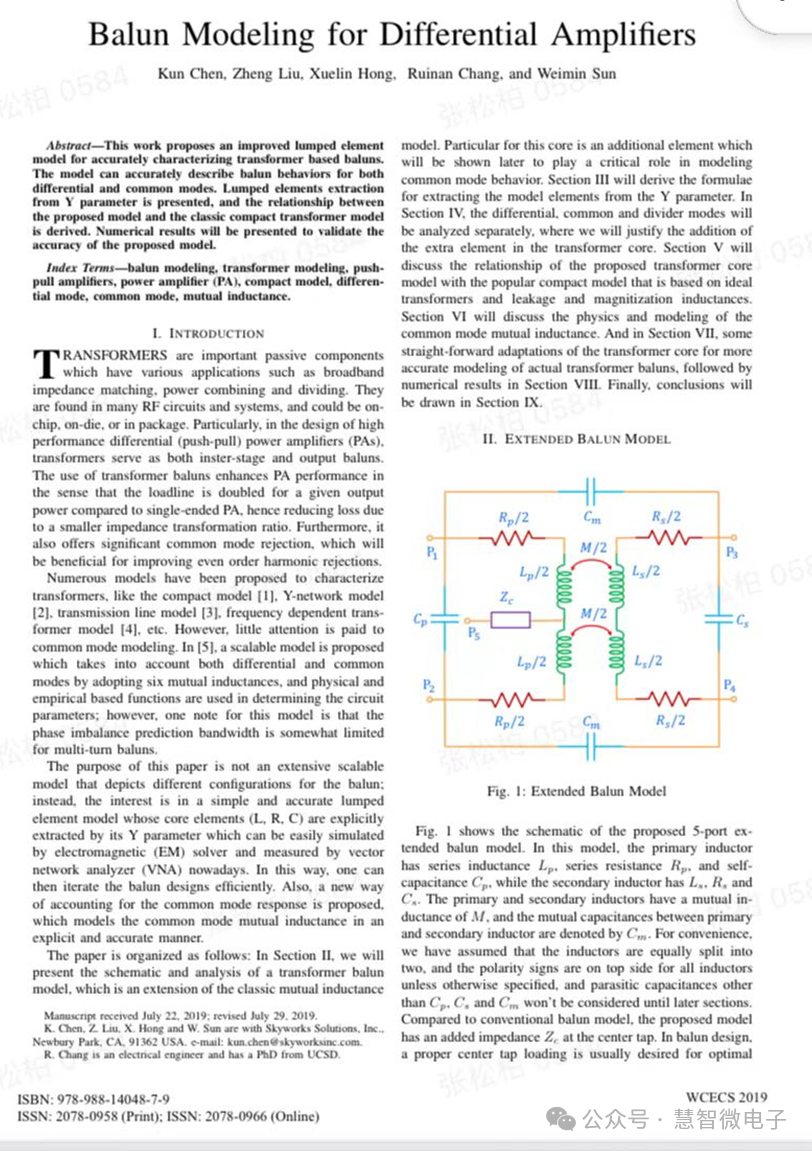

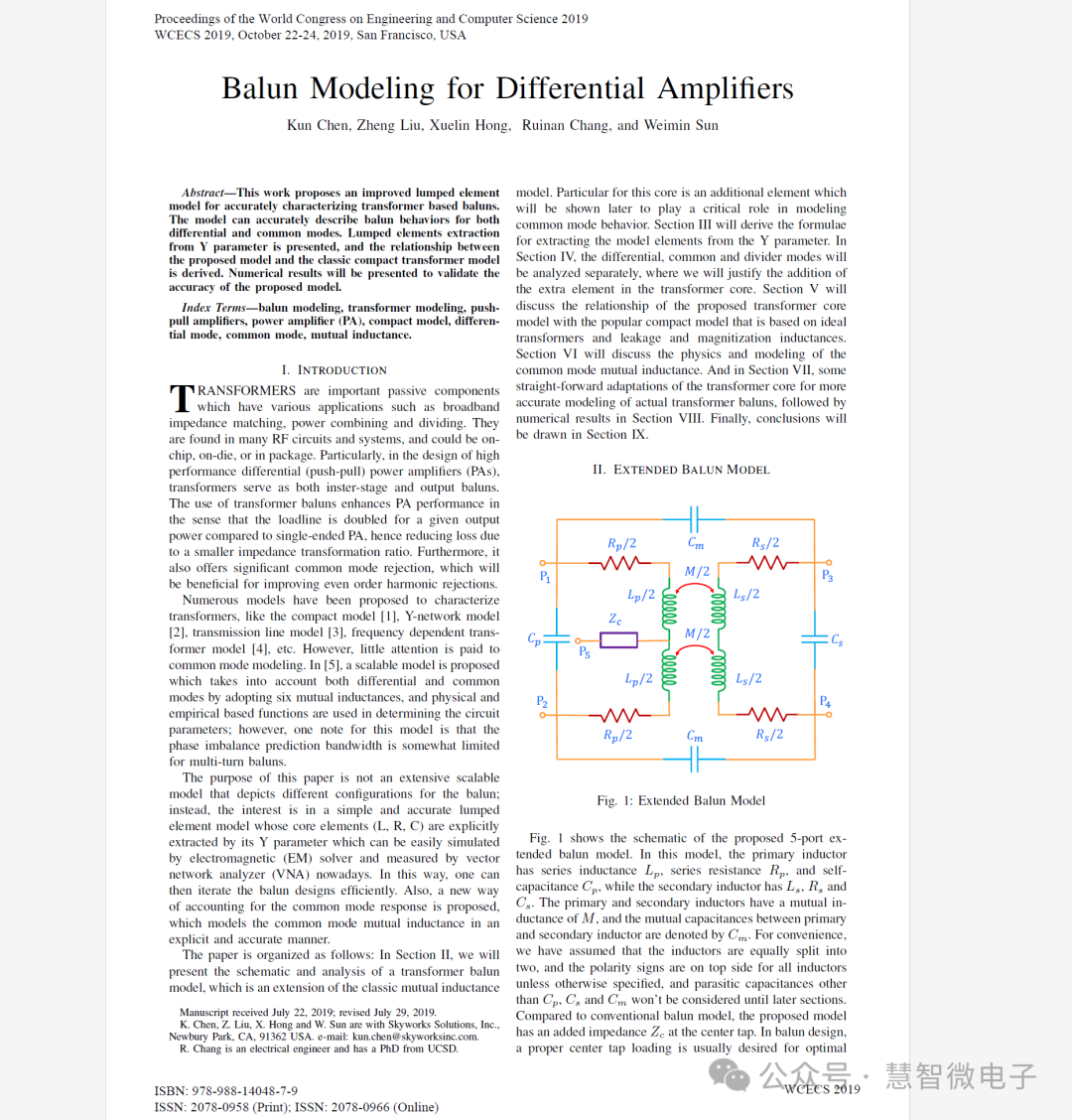

A:可以参考这篇论文。

Q:好像不一样,我这个是两个主圈耦合到同一个次圈上。

A:还有参考是Gang Liu 的博士毕业论文。该是常见的参考。

Q:多谢您!!!

04

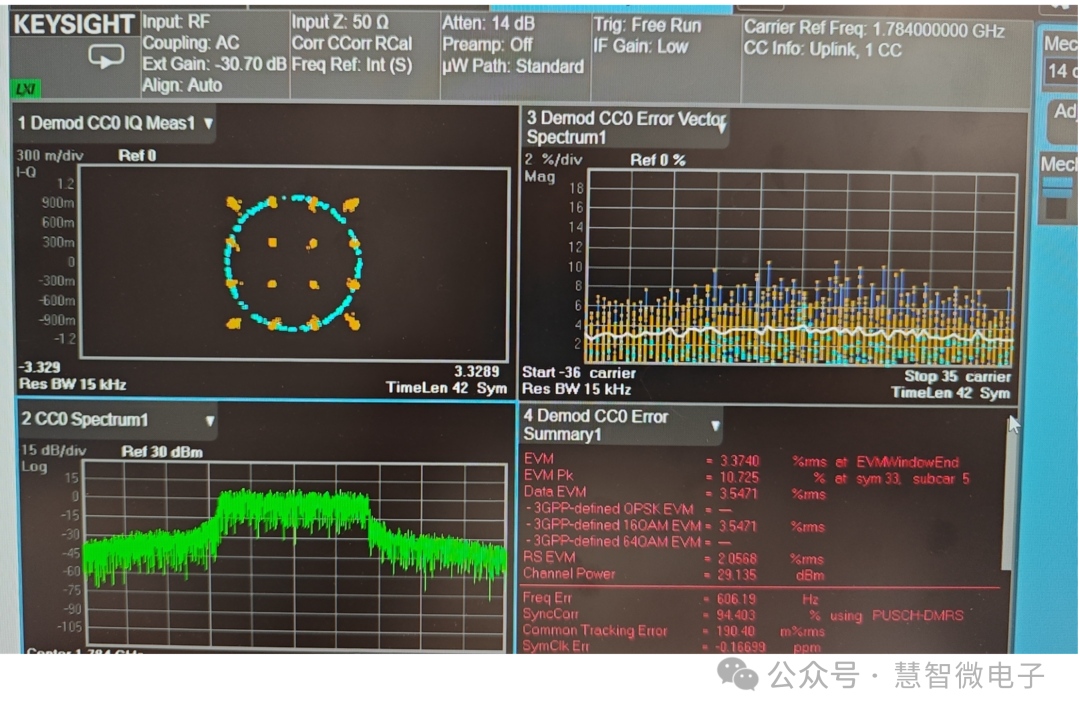

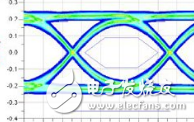

PA输入信号EVM和ACLR良好,但EVM为何恶化?

Q:请教个问题:PA输入信号EVM和ACLR都挺好,PA的增益和线性功率也很大,但是就是EVM恶化非常大,是啥原因呢?

A:线性功率很大,有数据吗?输入输出,PA的线性,都没数据,怎么分析呢?

A:输出的ACLR怎样?器件里面只有PA吗?有没有集成开关之类的?

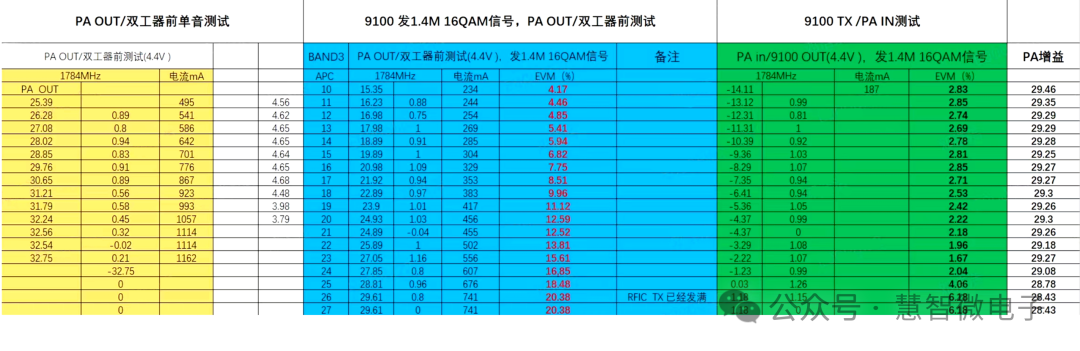

Q:左面黄色是单音测的,不知道输入。左面是PA 输入,中间是PA 输出信号。只有PA,集成的PA,内部有一个SP3T开关,把PA输出引到三个不同PAD。 EVM和ACLR全部恶化很多。

A:线性度的数据除了P1dB还要OIP3呢?

Q:OIP3没测,别的厂家的PA,其他低频段900M左右,EVM几乎没有恶化。

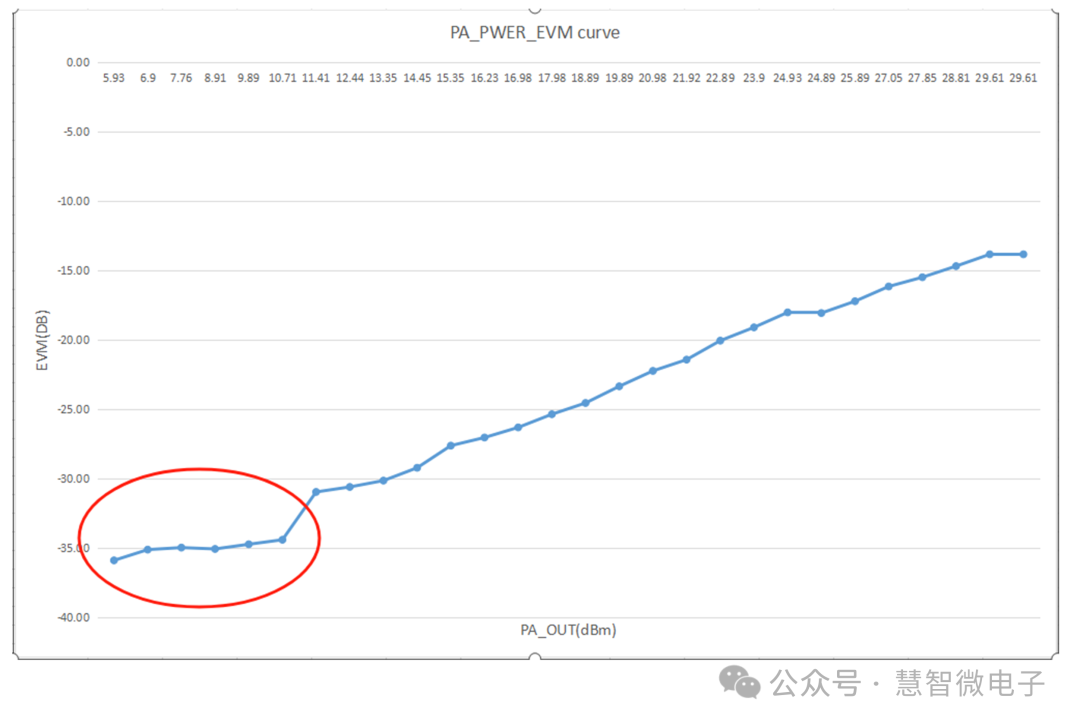

A:输入evm是-30dB,输出最开始是-27dB,感觉已经有非线性出来了。可以先讲输入信号调低,从PA输入从小到大,将PA的浴盆曲线扫描出来才能够判断了。

Q:找到最好的EVM?

A:一下怼非线性区不好办。

A:1是不是输入太大了?可以将输入打小点吗?

Q:输入可以打小,-14dBm,其实很小了。可以继续发更小功率,EVM可以和输入差不多。

浴盆曲线后,是要干什么?

A:最好evm才-30dB?

粗略判断链路的线性区间。

A:输入匹配是一样的吗?

Q:稍有不同,方便焊接调制信号把PA的匹配去掉了,直接接到频谱仪,原来有几个匹配,PA.输出匹配不是50欧姆。

A:不是应该拿信号源先测试外部PA么?直接上链路了?

Q:明天准备,信号源单独灌PA信号,因为之前除了1.4M带宽EVM ACLR也能达标,就没太关注。测了1.4M的16QAM信号,EVM超标了,把问题爆扣出来了。

A:工作时就TX不切对吧?“ 集成的PA,内部有一个SP3T开关,把PA输出引到三个不同PAD”

Q:工作时是固定的,不切换。

A:这个1.4m是容易出问题。

Q:猜测1.4M窄带OIP3异常。这个现象单独测试PA不一定有问题,毕竟PA的供应商肯定内部有测试过。

A:除了1.4M带宽信号,其他的带宽信号是多少的?

Q:3M/5M/10M/15M/20M带宽。

A:猜测1.4M窄带OIP3异常。这个现象单独测试PA不一定有问题,毕竟PA的供应商肯定内部有测试过。

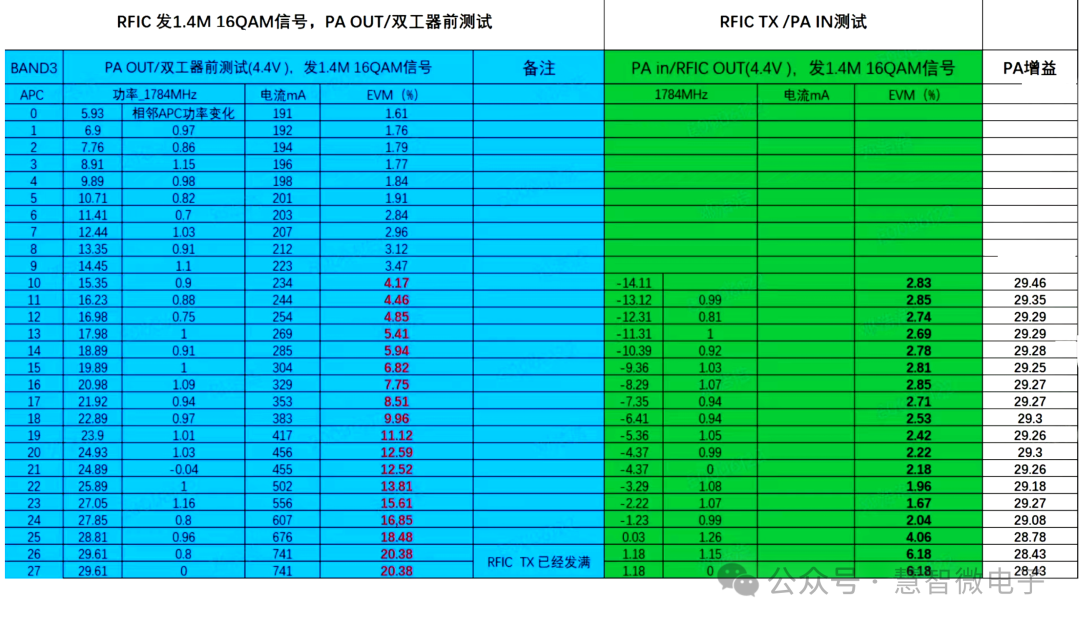

Q:补充了下小功率的EVM。

A:需要跟你用信号源输入信号,测量PA的输出进行对比;16QAM信号的峰均比是多少的?我忘记了;可以用频谱仪测量信号源输出16QAM信号时,峰值功率和平均功率的比值,那个就是峰均比了;不习惯用百分比来表示EVM,习惯用dB,线性区间只有这么点?

Q:单独PA输入,测试PA输出,EVM达到28dbm,EVM只从输入0.4恶化到2.2。PA输出29dbm,EVM也只到3.37。

A:那说明PA自身没问题,还是需要回到链路上面查问题了。需要排除1.4M窄带下OIP3。和排除PA对芯片输出的pulling之类的可能。

Q:PA的OIP3吗?PA对芯片pulling,这个怎么能够测试确认呢?

A:可以分开两个板子,一个是PA only,一个是主芯片only,PA only接信号源OK,是不是接主芯片那边就异常了。这样也方便接入功分器监测PA only接主芯片时,主芯片的输出指标。

Q:好的,谢谢。1.4M 的OIP3指的是PA本身吗?

A:链路的。

Q:多谢大佬。

A:一般像类似慧智微的PA出厂时都是经过严格测试过的,通常不会出问题,除非硬件上有环路自激。所以还要排除环路自激的可能。

A:感觉有点像环路自激,换个频点试试。

Q:这倒确实是有这种可能。多谢多谢。

05

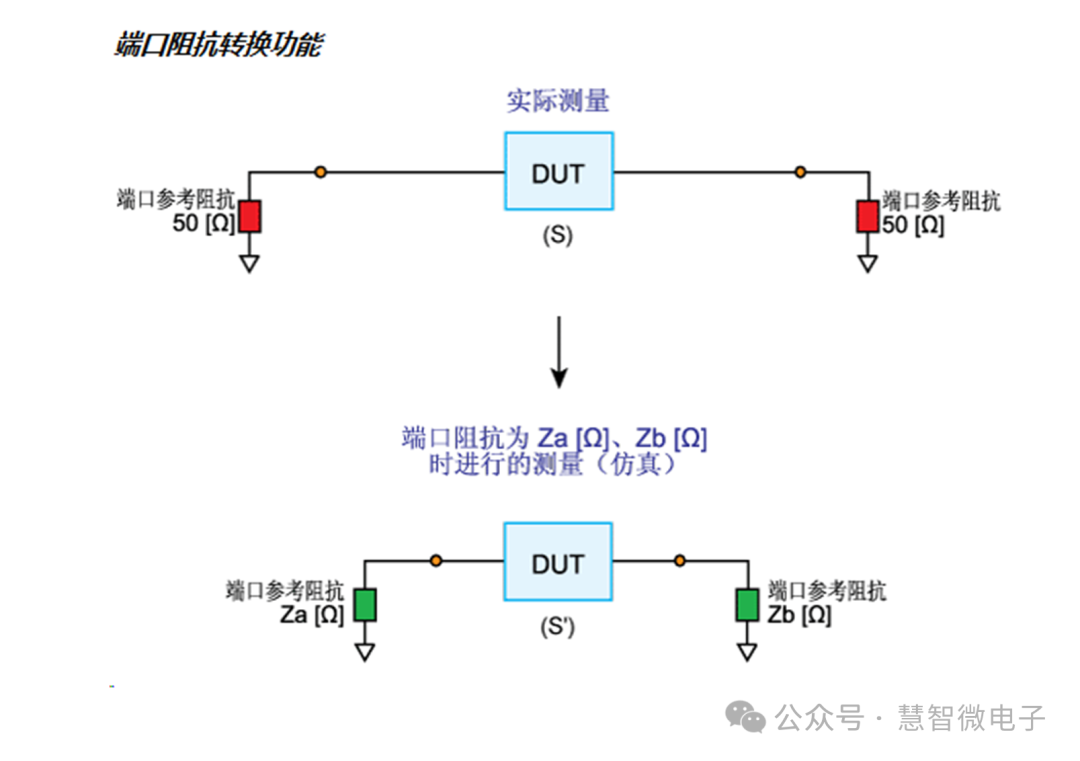

如何通过网分测试PA的输出功率?

Q:各位大佬,请问一下,网分测试pa。我的网分输入功率给了-40dBm,网分测试出来的增益是电压的状态下的值么(20log的结果)?比如15dB,那我想得到输出功率,是不是需要需要把这个15dB转化成10log的结果我这么理解对么?

A:你是想通过矢网测PA的输出功率?输入-40dBm,增益15dB,测量输出功率-40dBm + 15=-25dBm (要准确值的话,矢网端口要做功率校准)。

Q:是的,矢网测出来的是不是应该是电压表征的S参数?

A:这个是和你设置相关的;如果阻抗都设置为50Ω,就无所谓电压和功率;如果阻抗设置的不一样,那么就需要注意了;

Q:因为我想得到输出功率,如果矢网得到的是电压表征的S参数,那我是不是应该换算成功率表征的S参数后再加上输入功率,现在端口都是做了50Ω的匹配的。

A:那应该没问题吧。

Q:谢谢大佬的解答。

06

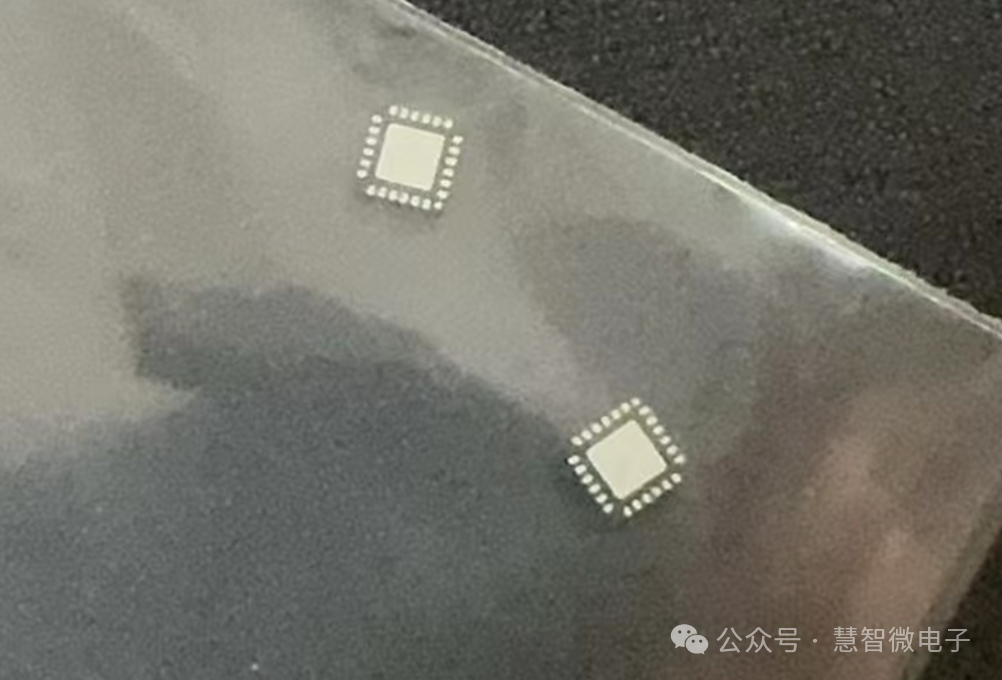

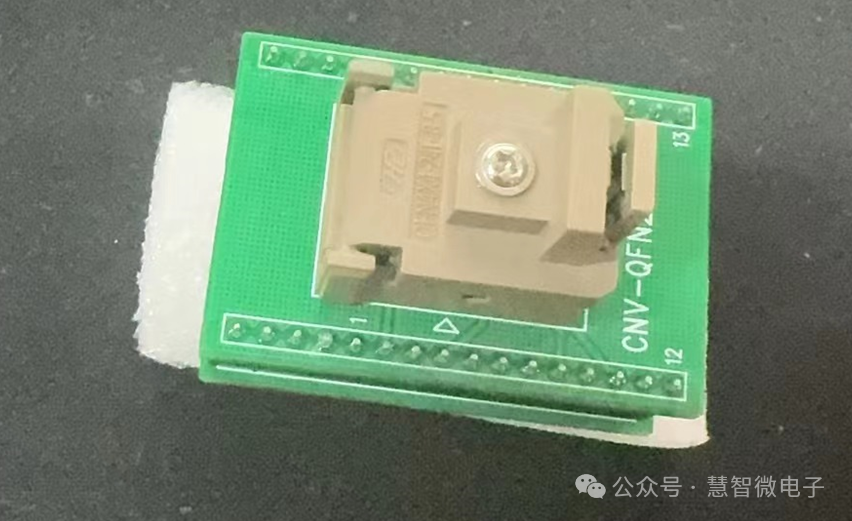

如何用网分测量芯片的S参数和驻波比?

Q:有大佬知道这种芯片如何用网分测量s参数,驻波比等参数吗?

A:要么焊接做成evb,要么做dutboard放socket里面。

Q:okok感谢感谢

A:不做测试板也可以,网分里边有一个功能叫测试端口延伸。

Q:好的好的我也去了解下谢谢。

Q:他好像有这么个东西。

有个公司找我们组代测试,他们工程师也不会我们的博士最近也很忙,没人管这个,所以来问问大佬们见过没。

A:这种的射频线接到哪里呢?

A:记不大清楚了,找根线,对线进行开路,和短路校准。

Q:图片里这好像就是个测试座,但是不知道怎么连。

A:我见过的和你说的这种测试座类似,但是芯片引脚通过测试版会引出来个sma接口,用于连接射频线缆进行测试。

Q:按道理我也觉得是这样子的,可是这个测试座,也没有引出来的用于射频连接的口。

A:网分可以校准到sma接头,再接上这个测试板,不放芯片,利用网分的端口延伸到socket里面的针脚上,也可以制作trl校准板,这样更准确一点。

Q:收到收到。我看看去。

07

芯片经历过HTOL实验后能保证正常工作多少年?

Q:请教各位大佬,有谁知道芯片经历过125摄氏度1000h的HTOL实验,能保证芯片正常工作多少年吗?

A:国军标里好像有模型,按照温度降低10℃,寿命增加一倍来算,假设正常工作温度在55℃,使用寿命是1000h*2^7,大概14.6年。

Q:好的谢谢。请问下是国军标的哪个标准啊?

A:我以前看到他们演示的是离线版本,很专业,只可惜没有拿到。估计应该是大同小异。

Q:好的,谢谢。我对比了两种模型的仿真结果,S参数仿真结果区别不大。这两种文件的区别,应该厂家在测试方法上的区别。

A:看你的频率了。

A:根據Arrhenius方程在使用溫度不同的情況下,加速因子還有活化能Ea也會有所不同,假設使用溫度55度活化能0.7eV,125攝氏度1000小時,相當於9年左右。您可以参考JESD47 和JEP122 。

A:器件物理那本书应该有。

Q:收到,感谢各位大佬。

08

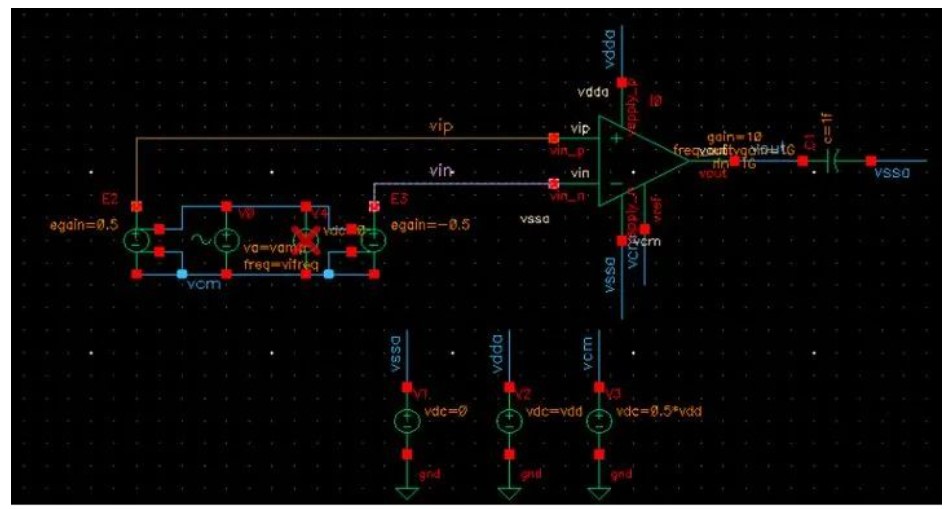

电容接地,版图上怎么连接的呢?这里需要加微带线吗?

Q:问下电容接地,版图上怎么连接的呢?这里需要加微带线吗?

A:上下两层金属都连到bvia就行了吧,图里看起来只连了met1。

Q:懂了,谢谢。

-

变压器

+关注

关注

160文章

7596浏览量

137012 -

Cadence

+关注

关注

65文章

935浏览量

142864 -

仿真

+关注

关注

50文章

4155浏览量

134478 -

EVM

+关注

关注

3文章

897浏览量

41387

原文标题:PA输入信号EVM和ACLR良好,但EVM为何恶化?

文章出处:【微信号:射频学堂,微信公众号:射频学堂】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

X-FAB宣布采用Cadence EMX Solver电磁仿真技术,加速创新通信和车用射频设计

分享PSpice AA仿真中的高级参数设置

Cadence仿真

如何在Cadence中搭建仿真电路去仿真摆率?

请问怎么理解cadence里面的port?

XILINX SERDES SI仿真中抖动的设置

如何在在Vivado中使用Cadence IES模拟进行仿真

Cadence推出EMX Designer,在片上无源元件综合上提供超过10倍的性能提升

Cadence EMX 3D Planar Solver 通过 Samsung Foundry 8nm LPP 工艺技术认证

如何在Cadence的EMX仿真中精准设置长边PORT

如何在Cadence的EMX仿真中精准设置长边PORT

评论