在传统的概念中,芯片工艺的改进将会带来性能的提高,成本的降低。同时,由于芯片内核电压的降低,其所消耗的功耗也随之降低,这一点到0.13um时代也是正确的。

但是在工艺进入90nm时代,甚至于以后的40nm或更小的工艺,出现了一点反常,芯片功耗将显著提高。

由于40nm工艺的内核电压进一步降低,电压降低的一个负面影响是晶体管中的沟道(channel)内的电场减弱,于是电子移动速度降低,实际上也就是晶体管的传播延时(tpd)增加了。为了达到非常高的性能,芯片设计厂商通常降低晶体管的门槛电压(Vth),使得晶体管快速开关,用来达到较小传播延时的目的。这个Vth就是使得晶体管的沟道(channel)开始导通时的最小电压值。

而Vth的降低,带来一个严重影响,就是晶体管漏电流随着Vth的降低呈指数增加,这样就会使得芯片的静态功耗大大增加,因此40nm的芯片制造商就是需要在芯片性能和其能承受的漏电流之间做一个权衡。

总的来说,芯片进入40nm时代后,门槛电压的降低以及晶体管尺寸的减小,都将会导致芯片漏电流增加,而这个漏电流就成为芯片静态功耗的主要来源,有的甚至高于芯片工作的动态功耗。

新工艺的使用反而带来功耗的大幅度增加,这是目前半导体业界所需要面临的一个普遍的问题。而功耗增加所带来的问题主要是芯片在工作中将产生更多的热量,如果这些热量不及时散播出去,芯片的温度将会升高,严重的时候有可能会导致芯片工作异常,甚至失效。

FPGA的功耗

FPGA器件的一个比较特别的现象是其上电瞬间的电流比较大,有的时候甚至大于芯片正常工作的电流,这是因为FPGA内部的逻辑和互连线资源(SRAM工艺)在上电的瞬间处于不确定状态,发生电流冲突的结果。

如果用户在设计的时候没有考虑到这个上电瞬间的打电流,电源模块不能够提供这么大的电流,芯片在上电过程中就会出现上电曲线不单调的问题,导致器件上电失败,以至于芯片无法正常工作。一般在器件手册中会给出这个上电电流值。

FPGA在正常工作中,其消耗的总功耗由器件的静态功耗、动态功耗和IO功耗构成。静态功耗也叫待机功耗(standby power),是芯片处于上电状态,但是内部电路没有工作(也就是内部电路没有翻转)时消耗的功耗;而所谓动态功耗是指由于内部电路翻转所消耗的功耗;IO功耗是IO翻转时,对外部负载电容进行充放电所消耗的功耗。

如下式:

总功耗=静态功耗+动态功耗+IO功耗

芯片的静态功耗是芯片处于待机状态下所消耗的功耗,它主要由芯片内部的漏电流产生。在高速的40nm器件中(如stratic IV),芯片的漏电流相对来说较大,因此静态功耗成为主要的电源功耗,也叫漏电功耗(leakage power)。

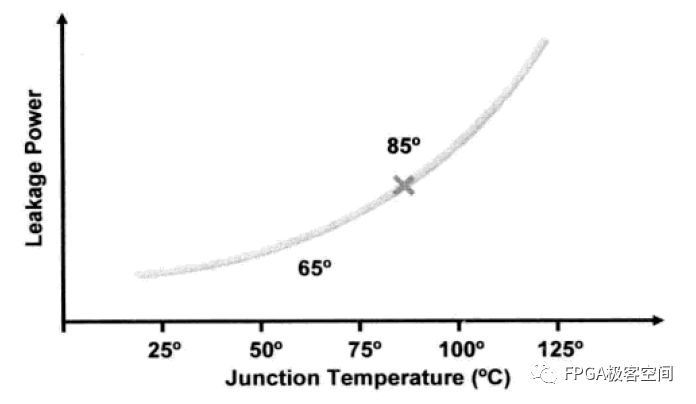

静态功耗有一个显著的特点,就是它随着器件结温(junction temperature,TJ)的变化而变化较大。TJ越大,功耗越大;TJ越小,功耗越小,如下图所示。因此,控制芯片的结温可以有效的控制芯片的静态功耗。

漏电功耗与器件结温的关系

相比以前的器件工艺(如0.13um),40nm器件由于内核电压的降低,芯片在工作时所消耗的动态功耗也相应降低。

至于IO功耗,因为其电源是与内核分开的,所以它消耗的功耗改变不大。

不同工艺器件的功耗组成如下图:

不同工艺器件功耗比较

功耗增加是40nm高速芯片的结果。如果芯片设计者降低器件的性能规格,那么其功耗也将随之显著降低。ALTERA 65nm的低成本器件CYCLONE III 就是一个很好的例子。

ALTERA为了使用户能够准确地评估其芯片在工作时候的实际功耗,提供了一种功耗计算的方法。

功耗计算器:用户需要估算FPGA中的各种资源使用情况,包括LE,RAM,PLL,DPS块和IO口等,以及它们工作的时钟频率。同时,用户也需要估计各种资源工作过程中的翻转率,这对芯片的动态功耗影响非常大。表格中同样给出了静态功耗值。在40nm的Stratix IV器件中,由于静态功耗受结温影响较大,因此计算表格中还需要用户输入环境温度、表面风速和散热片类型等参数,用来估计芯片的实际待机功耗。如果用户的设计已经完成,用户可以在quartusii中输出一个功耗估计文件,将其载入到估计表格中,就可以自动载入精确的器件资源使用情况。

基于仿真的功耗估计(powergauge):quartus ii提供了一种功耗估计工具。在使用之前,用户必须首先编译设计,然后根据设计的实际情况,给设计加一些激励,再在quartusii中对这个设计进行时序仿真。Powergauge可以在仿真过程中估算出芯片实际工作时的功耗,这种方法通常是在设计的后期用来精确估计芯片功耗时采用。和计算表格相比,它准确,但耗时。

-

FPGA

+关注

关注

1631文章

21810浏览量

606818 -

芯片

+关注

关注

458文章

51391浏览量

428445 -

功耗

+关注

关注

1文章

828浏览量

32135

原文标题:功耗的挑战

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA做深度学习能走多远?

Zstack中串口操作的深度解析(一)

浅析FPGA的功耗问题

java经典面试题深度解析

功能安全---AUTOSAR架构深度解析 精选资料分享

AUTOSAR架构深度解析 精选资料分享

什么是深度学习?使用FPGA进行深度学习的好处?

FPGA架构的功耗及影响功耗的用户选择方案

深度解析FPGA的功耗

深度解析FPGA的功耗

评论