电气系统的直流母线电压在400伏特或更高,由单相或三相电网电源或能量存储系统(ESS)供电,可以通过固态电路保护提高其可靠性和韧性。在设计高压固态电池断开开关时,需要考虑多个基本设计决策。关键因素包括半导体技术、器件类型、热包装、器件的稳健性,以及在电路中断时管理感应能量。本文将讨论在选择高压高电流电池断开开关的功率半导体技术和定义半导体封装时的设计考虑,以及对系统寄生电感和过流保护极限进行特征化的重要性。

宽禁带半导体技术的优势

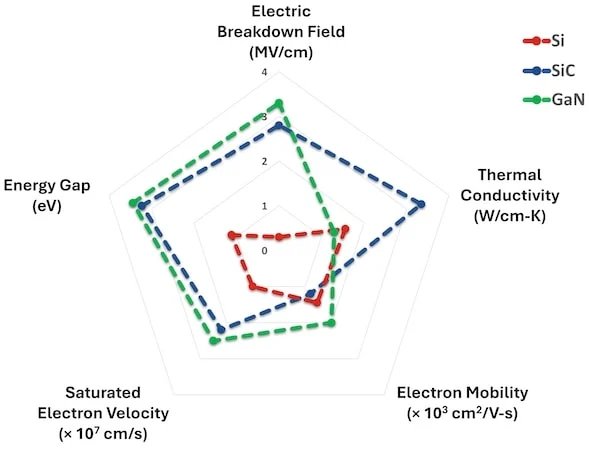

选择最佳半导体材料以实现具有最低导通电阻、最低关断漏电流、高电压阻挡能力和高功率能力的开关非常重要。图1显示了硅(Si)、碳化硅(SiC)和氮化镓(GaN)的半导体材料特性。SiC和GaN的电击穿场强约为硅的十倍。这使得可以设计具有漂移区厚度为等效额定硅器件十分之一的器件,因为其厚度与电击穿场强成反比。此外,漂移区的电阻与电击穿场强的立方成反比。这使得漂移区电阻降低近1000倍。在固态开关应用中,所有损耗都是导通损耗,高电击穿场强是一个显著的优势。这种降低的电阻也消除了动态锁存问题的担忧,在高dV/dt瞬态下,可能会触发硅功率MOSFET和IGBT中的寄生NPN晶体管或晶闸管。

图1

图1碳化硅的热导率是硅和氮化镓的三倍,这显著提高了从芯片中散热的能力,使其能够更冷运行并简化热设计。或者,对于等效目标结温,它允许更高的电流操作。更高的热导率,加上高电击穿场强,导致低导通电阻,进一步简化了热设计。

碳化硅作为一种宽禁带(WBG)半导体材料,其能隙几乎是硅的三倍,这使得其能够在更高温度下工作。当温度升高时,半导体的功能会丧失。更宽的能隙使碳化硅能够在比硅高数百摄氏度的温度下工作,因为自由电荷载流子的浓度较低。然而,基于当前技术的其他因素(例如,封装、栅氧化物漏电)限制了器件的最大连续结温为175°C。WBG技术的另一个优势是提供更低的关断漏电流。

考虑到这些特性,碳化硅是此应用的最佳半导体材料。

IGBT、MOSFET和JFET之间的差异

晶体管类型是下一个关键因素。在大多数情况下,导通损耗是最大的设计挑战。应尽量减小导通损耗,以满足系统的热要求。一些系统中提供液体冷却,而其他系统可能使用强制空气或依赖自然对流。除了最小的导通损耗外,电压降也必须保持在最低,以最大化所有工作点(包括轻负载条件下)的效率。这在电池供电系统中特别重要。在许多系统(包括直流系统)中,双向电流流动也是一个重要因素。通常希望选择具有低导通损耗、低电压降和反向导电能力的晶体管。常被考虑的晶体管包括IGBT、MOSFET和JFET。

虽然IGBT在峰值负载电流下提供与MOSFET相当的导通损耗,但一旦负载电流降低,基于IGBT的解决方案的效率就会下降。这是因为电压降由两个部分组成:一个与集电极电流无关的近恒定电压降和一个与集电极电流成比例的电压降。MOSFET的电压降与源电流成正比。它没有IGBT的额外开销,因此能够在所有工作点(包括轻负载条件下)实现高效率。MOSFET允许在第一和第三象限进行通道导电,这意味着电流可以在设备中正向和反向流动。MOSFET在第三象限操作的附加好处是其通常具有比第一象限稍低的导通电阻。而IGBT仅在第一象限导电,需借助反并联二极管进行反向电流导电。

JFET是一个较老的技术,但正在复兴,能在正向和反向导电中工作,并且与MOSFET类似,其电压降与漏电流成比例。JFET不同于MOSFET的是它是一种耗尽模式设备。也就是说,JFET通常是导通的,需施加栅极偏压以抑制电流流动。当考虑系统故障条件时,这给设计人员带来了实际挑战。作为解决方案,可以使用级联配置,包括一系列低电压硅MOSFET,以实现通常关闭的设备。添加系列硅器件增加了复杂性,降低了JFET在高电流应用中的一些优势。SiC MOSFET作为一种通常关闭的设备,提供了许多系统所需的低电阻和可控性。

热包装

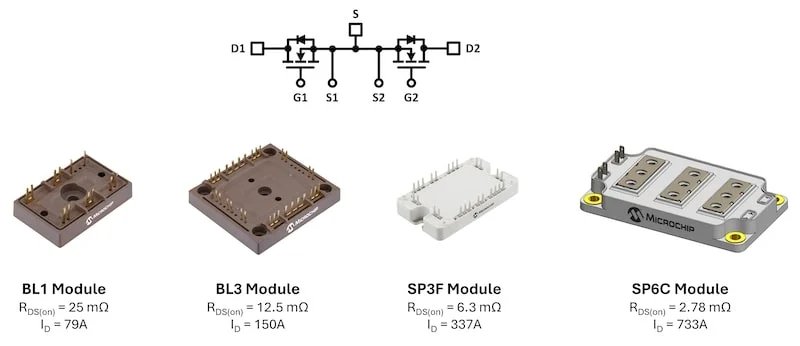

SiC功率模块能够实现高水平的系统优化,这在并联离散MOSFET时是难以实现的。Microchip的mSiC模块提供多种配置和电压、电流等级。其中包括常源配置,连接两个SiC MOSFET,以反串联配置实现双向电压和电流阻挡。每个MOSFET由多个并联连接的芯片组成,以达到额定电流和低导通电阻。对于单向电池断开开关,两个MOSFET在功率模块外部并联连接。

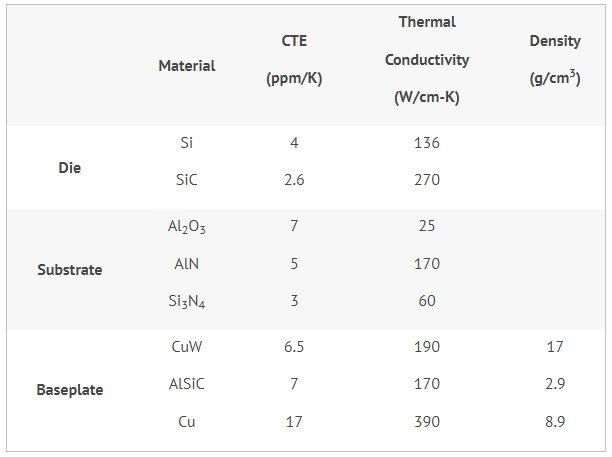

需要低导通电阻和低热阻以保持芯片冷却。模块内使用的材料是决定从结到壳体的热阻以及其可靠性的关键元素。具体而言,芯片连接、基板和基座材料特性是模块热阻的主要贡献者。选择具有高热导率的材料有助于最小化热阻和结温。除了热性能外,选择具有相似热膨胀系数(CTE)的材料可以通过减少材料界面和内部的热应力来延长模块的使用寿命。表1总结了这些热特性。氮化铝(AlN)基板和铜(Cu)基座是mSiC功率模块的标准配置。使用氮化硅(Si3N4)基板和铝硅化合物(AlSiC)基座的选项提供更高的可靠性。图2展示了在标准SP3F和SP6C封装中的常源功率模块及经过DO-160认证的高可靠性无基座BL1和BL3封装。

表1

表1器件的稳健性和系统电感

除了模块的热性能和长期可靠性外,电路中断设备的另一个设计考虑是高感应能量。继电器和接触器的循环次数有限。通常,它们在无负载机械切换周期下规定,而电气负载切换周期显著更少。系统中的电感导致接触器断开时发生电弧,造成接触器的退化。因此,电气循环额定值的操作条件是专门定义的,并对其使用寿命有很大影响。即便如此,在使用接触器或继电器的系统中仍需上游熔断器,因为在高短路电流下,接触器可能会焊接在一起。固态电池断开开关不受此种退化影响,从而提高了系统的可靠性。尽管如此,了解系统的寄生电感和负载电感及电容也至关重要,以管理在中断高电流时存在的感应能量。

图2

图2感应能量与电感和中断时系统中的电流平方成正比。开关输出端短路会导致电流快速增加,以电池电压与源电感之比的速率上升。例如,800伏特母线电压和5微亨的源电感会导致电流以每微秒160 A的速率增加。5微秒的响应时间来检测和响应,将导致电路中额外增加800 A电流。由于不建议在雪崩模式下运行SiC功率模块,因此需要使用阻尼器或夹紧电路来保护模块,通过吸收这个感应能量。然而,当正确设计以满足爬电和间隙要求时,添加到阻尼电路的寄生效应进一步限制了其有效性。因此,开关应在足够缓慢的情况下关闭,以限制模块内部电感和电流突降带来的电压过应力。设计低电感的模块有助于进一步最小化这种电压应力。

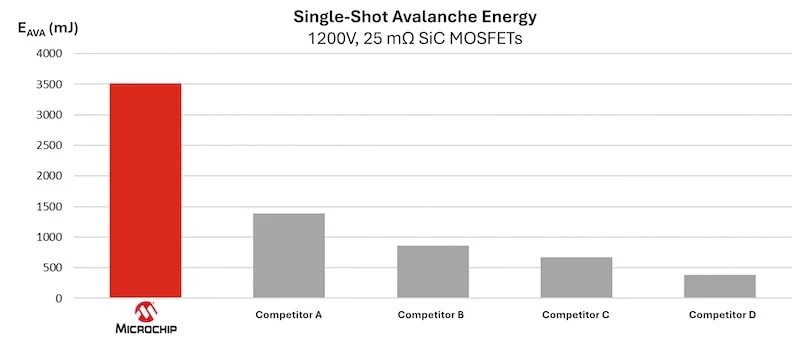

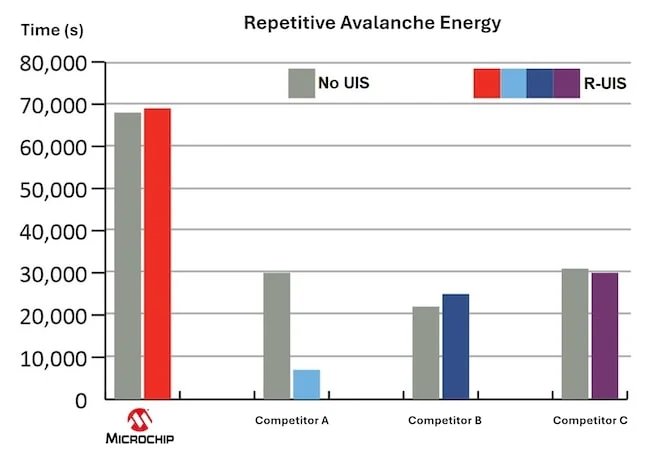

在硅功率器件中,快速中断高电流会引发寄生NPN晶体管或晶闸管的触发,导致无法控制的锁存和最终故障。在SiC器件上,快速关断可能导致每个芯片在关断过程中发生低能量雪崩击穿,直到阻尼器或夹紧装置吸收高能量。Microchip的mSiC MOSFET经过设计和测试,具备无夹紧感应切换(UIS)抗压能力,提供了额外的安全边际,因为阻尼器或夹紧装置开始退化。图3展示了与市场上其他SiC器件相比的单次和重复UIS性能。

图3

图3虽然应理解器件级短路能力,且IGBT在器件级短路性能上优于MOSFET,但在实际系统中,它会遭遇不同的应力条件。由于系统电感的固有限流行为,模块不太可能达到其短路电流额定值。限制因素是阻尼器或夹紧电路的设计。为了设计一个成本效益高且紧凑的阻尼器,允许的系统级峰值短路电流将被限制在远低于模块短路电流额定值的水平。例如,在一个500 A的电池断开开关中,由九个并联芯片组成,设计以防止短路电流超过1350 A,每个芯片导电电流为150 A,假设电流分布均匀。这是远低于在设备级短路测试中电流超过几百安培的水平。优化电压钳位装置是设计稳健固态电池断开开关的关键部分。

其他设计考虑

除了功率器件之外,还有与控制电子相关的设计考虑,包括电流传感技术、过流检测与保护以及功能安全。决定是使用分流电阻还是磁性技术进行电流传感对于在低寄生电感的系统中设计至关重要,因为快速响应时间是必需的。是否使用硬件、软件或两者结合进行过流检测也是一个重要决策,特别是在设计以满足功能安全要求时。碳化硅和功率半导体封装的优势是固态断开开关相较于传统机械断开开关提供的系统级效益的关键推动力。利用碳化硅技术,现在可获得低导通电阻和热阻的器件,使其在许多系统中满足低导通损耗的需求,同时使用确保高可靠性的材料。

-

SiC

+关注

关注

30文章

2951浏览量

63222 -

电气系统

+关注

关注

1文章

369浏览量

24405 -

电池

+关注

关注

84文章

10737浏览量

131993

发布评论请先 登录

相关推荐

接触器与固态继电器为高压电气系统可靠性与效率赋能

什么是电气系统微机保护设置?

提高开关电源可靠性的技巧

SiC-SBD关于可靠性试验

SiC-MOSFET的可靠性

电气系统接入DCS实现发电厂电气监控系统的可行性

单片机应用系统的可靠性与可靠性设计

PLC软元件在电气系统可靠性设计中的应用

如何通过高压SiC电池断开开关提升电气系统的可靠性与效率

如何通过高压SiC电池断开开关提升电气系统的可靠性与效率

评论