随着通信和数据中心应用升级至更高的数据传输率以支持迅速增长的互联网流量需求,SerDes 参考时钟的性能正变得日益重要。如果参考时钟抖动太高,会导致比特误码率 (BER) 过高、流量丢失或系统通信丢失。此外,56G PAM4 PHY、100G/200G/400G 以太网和 100G/400G OTN 需要多种频率组合,进一步增加了时序的复杂性。

为此,Silicon Labs提供了全新有源时钟振荡器,其采用第四代 DSPLL 技术驱动,有效解决了 25/40/50/100/400Gbps 时序问题。本篇技术文章-“使用高性能有源时钟振荡器降低通信应用开发风险”将详细分析高速通信和数据中心的时序要求,并介绍Silicon Labs经市场验证的时钟振荡器解决方案,帮助工程人员克服日益艰钜的高速网络定时设计挑战。

高速通信和数据中心的时序要求

Silicon Labs 的最新 Si54x Ultra Series 有源时钟振荡器产品专为这些要求高的高速通信和数据中心应用而打造。这些高性能有源时钟振荡器具有任意频率合成和 80 fs RMS 超低抖动的特点,有标准尺寸和小封装尺寸有源时钟振荡器供选择。Ultra Series 具有领先的抖动容限和频率灵活性,可为硬件设计者带来设计自信,同时降低产品开发风险。

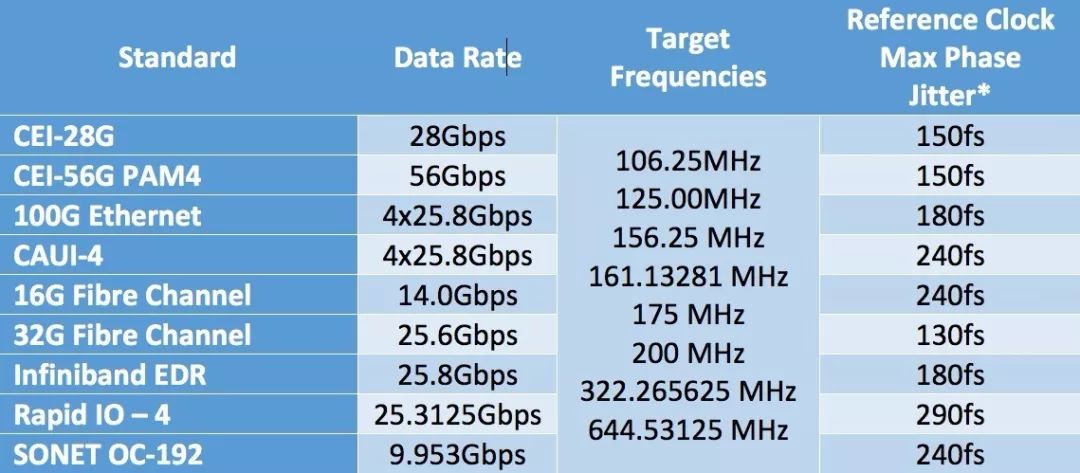

图 1. 高速通信和数据中心的时序要求

*注意:直接根据参考时钟或传输器眼闭规格计算,符合原始(未经 FEC)的 BER 要求,眼闭预算为 50/50 的确定性抖动/rms 抖动和 33%/67% 的时钟/传输器。

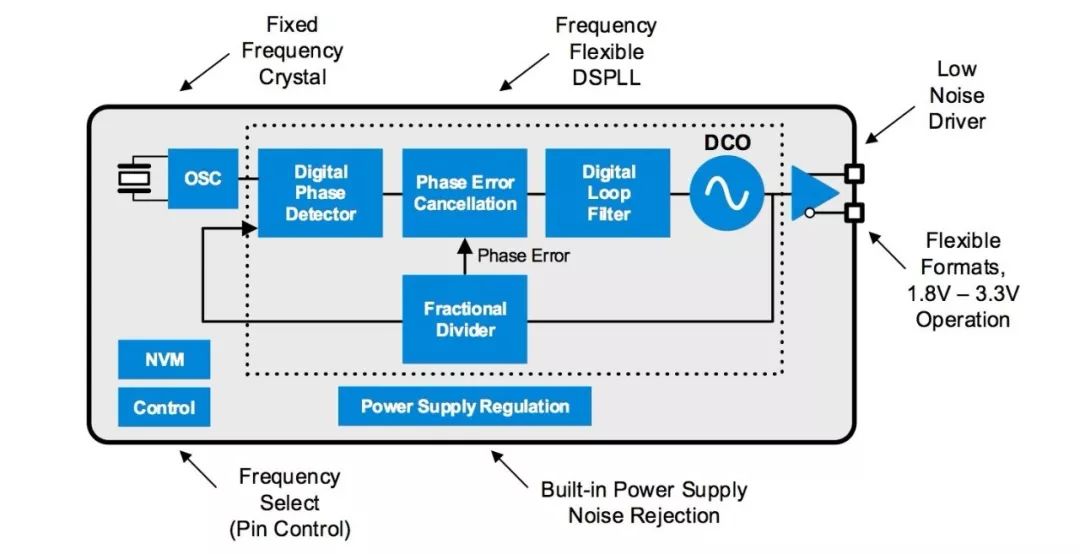

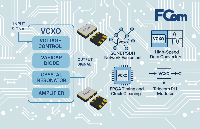

图 2 Ultra Series DSPLL 体系结构

图 2 为 Silicon Labs 全新 Ultra Series 第四代 DSPLL 的体系结构。不同于需要复杂批次制造过程、不同频率使用不同晶体的传统有源时钟振荡器技术,Si54x 体系结构结合了简单的高质量固定频率晶体和 Silicon Labs 最新一代的 DSPLL,可产生任意频率。输出测试期间,设备可设为自定义的目标频率。采用这种创新方法,可轻松对 Si54x 进行批量自定义,以满足不同客户的不同需求。Si54x Ultra Series 支持 200 kHz 至 1.5 GHz 之间的任意频率,仅通过一个产品系列便可轻松同时支持标准频率和自定义频率应用。

采用行业领先的 55 nm CMOS 技术设计,第四代 DSPLL 利用高度数字化的体系结构来实现最优的频率灵活性和抖动性能。DSPLL 相位探测器的输入会从模拟输入转换为数字输入,使 DSPLL 完全在数字域内运行。这种全面数字化方法有诸多优点。首先,可用低于 1 ppb 的步长来精确控制数字控制有源时钟振荡器 (DCO),以追踪参考时钟与反馈时钟之间的相位延迟。DCO 增益较小,因此电路出现噪声的可能性较传统模拟 PLL 更低。其次,DSPLL 支持创新型相位误差消除电路,利用高级数字信号处理器来消除延迟、非线性和温度影响导致的 PLL 噪声。这些体系结构特点确保设备在不同过程、电压和温度下有一致的性能。因此,Silicon Labs 的第四代 DSPLL 体系结构在整个运行范围都可实现超低抖动。

兼具频率灵活性和超低抖动

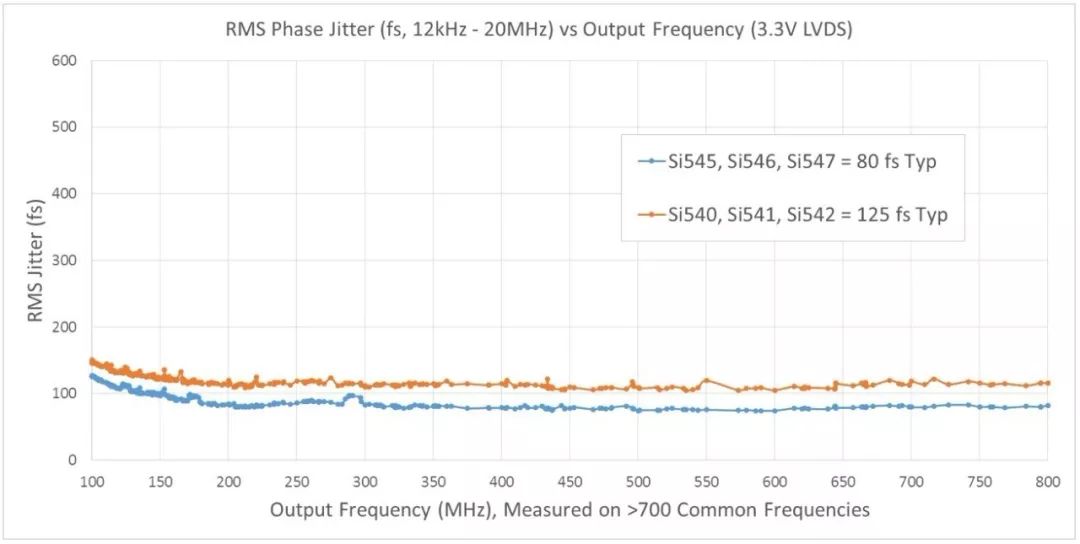

下图为 Ultra Series 抖动性能与运行频率和温度对比图。有两个可用性能等级。Si545/6/7 设备的典型相位抖动性能为 80 fs RMS(12kHz - 20MHz),而 Si540/1/2 设备的典型相位抖动性能为 125 fs RMS (12kHz - 20MHz)。由于其抖动性能,Si54x 可将抖动容限最大化,为硬件客户带来设计自信。

图 3 Si54x Ultra Series XO 抖动性能与频率

为了进一步简化设备评估,Silicon Labs 提供了 XO 相位噪声查找实用工具,可用于检索超过 1000 个常见频率范围下的 Silicon Labs 有源时钟振荡器相位噪声图。若想使用此免费实用工具,请访问:

http://www.silabs.com/tools/pages/oscillator-phase-noise-lookup-tool.aspx。

集成电源噪声控制

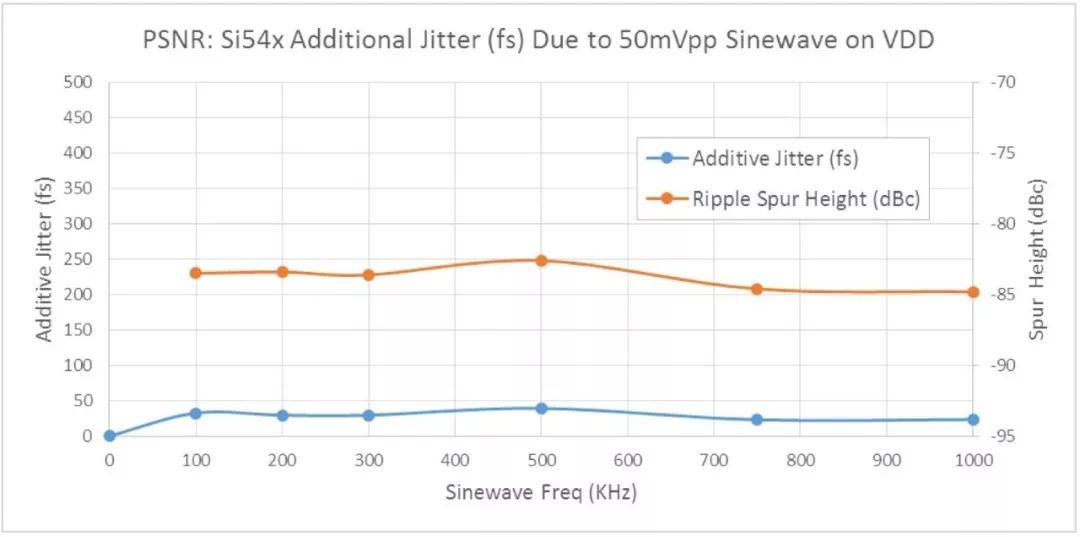

第四代 DSPLL 有广泛的集成低压差稳压器网络,具备电源噪声抑制特性功能,确保即使在有噪声的系统环境下也始终可实现低抖动运行。集成电源噪声抑制的另一个优点是可简化电源滤波、PCB设计和布局。

图 4 最小化附加抖动的集成 PSNR

多频支持

除标准单频有源时钟振荡器外,也有使用 Silicon Labs 第四代 DSPLL 体系结构的双频或四频有源时钟振荡器。这些设备可用一个 IC 替代两个或更多离散有源时钟振荡器,将 BOM 成本和复杂性降至最低。多频有源时钟振荡器有多个优点:

采用单个设备即可支持多协议SerDes

简化设置/保持时间测试

频率容限(例如:156.25 MHz + 50 ppm,156.25 MHz,156.25 MHz -50ppm)

简化原型设计。使用一个多频有源时钟振荡器用多种参考时钟测试新的 SerDes 和 ASIC。选定最终频率后,转换为固定单一频率有源时钟振荡器

单一电源

Silicon Labs 的 Ultra Series 有源时钟振荡器有一个高度灵活的输出驱动器,可以在工厂自定义,以支持任何常用信号格式:LVDS、LVPECL、HCSL、CML、CMOS 和双 CMOS。此外,输出驱动器支持的电源电压范围较宽。一个 Si54x 设备即可支持 1.8V-3.3V 的运行电压范围,仅使用单一部件编号的有源时钟振荡器即可替代 1.8V、2.5V 和 3.3V 等固定电压的多个有源时钟振荡器。

快速获得样品

Silicon Labs 提供基于网络的实用工具,可在 1 分钟内创建定制有源时钟振荡器。创建部件编号后,可通过 Silicon Labs 的授权分销商或 Silicon Labs 网站下订单。样品通常在下单后 1-2 周内发货。该过程可大大简化有源时钟振荡器采购,是为原型和 NPI 试产快速获取设备的完美选择。

-

数据中心

+关注

关注

18文章

5832浏览量

75242 -

时序

+关注

关注

5文章

411浏览量

39050 -

时钟振荡器

+关注

关注

3文章

49浏览量

56945 -

高速通信

+关注

关注

0文章

61浏览量

11202

原文标题:【技术干货】使用高性能有源时钟振荡器降低通信应用开发风险

文章出处:【微信号:SiliconLabs,微信公众号:Silicon Labs】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

优化800G数据中心:高速线缆、有源光缆和光纤跳线解决方案

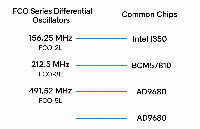

27MHz HCSL 差分晶体振荡器在数据中心网络存储系统中的应用方案

中型数据中心中的差分晶体振荡器应用与匹配方案

中型数据中心应用平台与差分晶体振荡器参数对照中型数据中心应用平台与差分晶体振荡器参数对照

DVI接口详细分析

时钟产品系统解决方案及MEMS振荡器问题答疑

数据中心布线方案:数据中心怎样选择光纤布线?

基于ispClock 5406D的高速串行接口时钟解决方案

数据中心光互联解决方案

详细分析stm32f10x.h

低抖动VCXO振荡器:SONET时钟与高速通信的核心时序方案

详细分析高速通信和数据中心的时序要求以及时钟振荡器解决方案

详细分析高速通信和数据中心的时序要求以及时钟振荡器解决方案

评论