引言

多年以来,一直存在标准泛滥的现象,而我们电子业尤其严重。您是否曾经想过,为什么我们对有些奇怪的数字或测量计的东西建立标准?关于航天飞机的固体燃料火箭推进器的直径是否真的源自于马屁股的宽度的讨论非常激烈。2相当的稀奇和有趣。但是,接受事实会更有成效:总是会有很多标准,我们必须找到使其很好配合的途径。工程师和制造商均涉及到一个共同领域,其中标准的不兼容特别麻烦:原型平台。幸运的是,有些方法可以缓解这些不兼容性。下文中我们将进一步分析讨论。

开发板扩展标准

多年来,元件制造商一直提供开发系统,帮助其客户采用其元件设计应用。对于可编程器件,例如FPGA和微控制器,始终存在与其它元件的接口,以便能够与硬件同步或者早于硬件进行软件开发。随着时间推移,涌现出了关于这些“扩展接口”的非常松散的伪标准,其中有些标准的一致性相对较好。Xilinx等FPGA厂商推动这些标准,例如FMC,使客户尽可能简单地迁移到最新平台。Xilinx也采用第三方标准,例如Digilent制定的Pmod标准,用于该接口的外围设备选择较广。微控制器制造商的标准化略慢,许多采用自身的专用接口。然而,制造商动向和Arduino平台普及等市场力量正驱使其也向伪标准靠拢。

Pmod非常适合FPGA

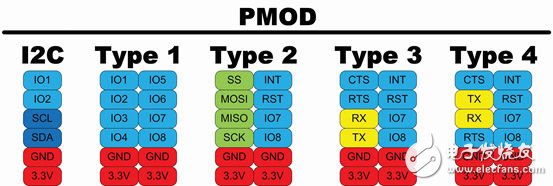

Pmod接口是将外设与FPGA开发板进行组合和匹配的很好方式,可利用方便、可手工焊接的连接器连接八个引脚以及电源和地。FPGA的灵活性允许将其八个信号引脚用于几乎所有功能。尽管这提高了其对于FPGA的实用性,但也造成该接口难以配合那些外设功能分配给特定引脚的微控制器。为解决这一问题,Digilent定义了多种不同的Pmod引脚排列类型,不同的功能分配给特定的引脚(图1)。

图1. Pmod引脚排列类型将不同的功能分配给特定引脚。

类型定义使得微控制器板较容易使用Pmod接口标准,但仍然存在挑战。利用许多微控制器有限的引脚复用能力,难以实现真正的通用接口,已被废弃的Type 3 UART接口就是很好的例子。然而,即使存在局限性,对于原型或教育目的,Pmod接口是一种非常有用的扩展端口。

Arduino伪标准

Arduino伪标准是一个完全不同的老顽固,是出于各种原因为不同群体开发的不同平台。最初的Arduino开发板仅提供简单微控制器引脚,然后增加足够的支持器件,从而使编程变得简单,并且爱好者仍然可承受。由于其简单性,原始引脚排列按照微控制器的性能定义。

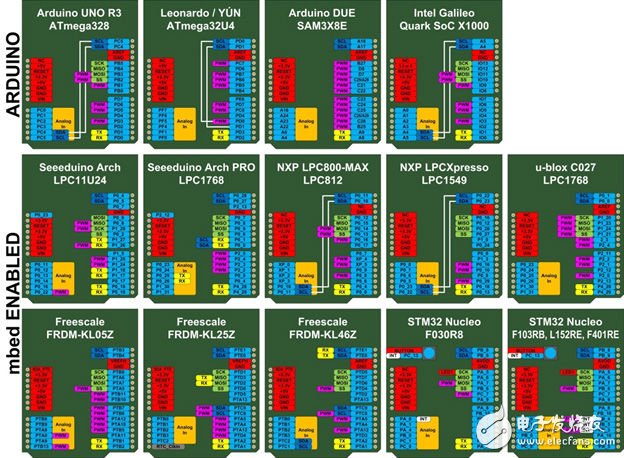

随着平台发展到支持功能更多的处理器,该伪标准逐渐碎片化,具有各种引脚复用组合,可以说是例外多于规则。有些问题,例如支持不同的I/O电压以及I2C信号的不一致性,在第3版的UNO板中得到了解决。然而,在将扩展板与Arduino开发板(或任何Arduino衍生产品)配对使用时,必须仔细检查兼容性。并且可供选择的Arduino衍生产品很多(图2),即使仅限于Arduino网站提供的官方开发板,引脚兼容性也并不简单。但是,一般而言,每个具有特殊功能的Arduino引脚也可用作通用I/O (即GPIO)。

图2 .Arduino开发板配置为多种衍生产品,以支持不同的设计和应用。

与Pmod接口中一个引脚可用作多种特殊功能不同,大多数Arduino引脚通常执行单一的特殊功能。从根源上讲,Arduino伪规范比Pmod接口更适合于微控制器。所以,这就是Arduino规格的微控制器板比Pmod连接器的微控制器板更容易找到的原因。

Pmod与Arduino接口之间的映射

我们可以采用Pmod接口和Arduino伪标准,两者各有众多来源可供使用。是否能够使某个平台的外设与另一平台的控制器进行通信呢?当然,一切皆有可能,但有时候治疗比疾病本身更糟糕。

如果将Arduino UNO第3版引脚排列与Pmod规范进行比较,您马上会发现Arduino板上有22个信号引脚,而Pmod连接器上只有8个引脚。从技术上讲,有可能将全部22个引脚串行化,使其通过Pmod提供的8个引脚,然后在另一侧对其进行解串,但我们将这一工作留给读者。将22个Arduino信号自适应映射到Pmod规范定义的不同类型(见图1),是可以做到的,但仍不轻松。以上图1所示为5种不同类型的Pmod接口。许多信号采用电平触发,可由软件通过GPIO引脚控制。然而,有些信号采用时间触发协议,利用微控制器内部的外设更容易控制。所以,困难在于将微控制器的所有专用引脚映射到Pmod规范定义的引脚。

建议方案:使用串行控制交叉点开关

解决映射问题的一种途径是在电路板上安装配置跳线阵列。这种方法尽管很简单明了,但既不美观也不人性化。适合Arduino板尺寸的说明文字字体会非常模糊难辨。许多引脚可能是双向的,所以简单的逻辑门不是信号连接的好选择。模拟开关能起作用,但没有足够的附加引脚来对其进行独立控制。利用I2C端口扩展器,可解决引脚短缺的问题。诚然,这种方法不比跳线更巧妙,但可通过软件配置。

如果没有串行控制16:2多路复用器,MAX14661,这种方法似乎毫无希望。咋一看,支持所有不同类型的Pmod好像需要四片器件,那么这种方法很难说比端口扩展器方案好多少。实际情况真的会是这样,除非...MAX14661具有特殊功能。该器件允许同时激活任意开关组合,所以可用作8:8交叉点开关。

至此为止,一切顺利。但是,不可否认,8:8交叉点配置有一个局限性:同时只能传输两路独立信号,每个COM引脚一路。但同时两路信号有什么好处?如上所述,大多数信号可由GPIO驱动,只有少数信号要求内部外设控制器。如果每个引脚分配一路GPIO,只有时间触发的串行线路需要通过复用器连接。UART和I2C为2线总线,所以不适合通过复用器的唯一串行总线是SPI。SPI只有一种接口定义,所以将SPI信号直接连接至连接器,作为这些接口的GPIO连接。当其中某个引脚需要用作时间触发功能时,只需将GPIO置于三态。

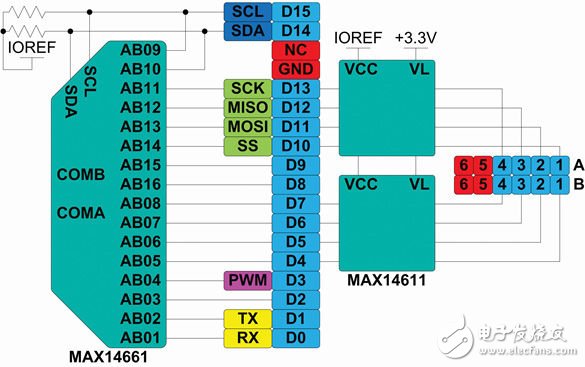

信号电平怎么样呢?最初的Arduino设计及许多后来者使用5V信号电平,但现在5V信号没有以前那么常见。为解决这一问题,后来的Arduino版增加了IOREF引脚,以表示基于较低电压微控制器的衍生品。Pmod连接器没有IOREF引脚,但其绝大多数模块支持3.3V信号。幸运的是,MAX14611等双向电平转化器解决了这一问题。只需将Arduino信号连接至由IOREF供电的电平转换器的一侧。然后将另一侧连接至由Arduino板上专用3.3V电平供电的Pmod连接器。MAX14661多路复用器采用1.8V至5V的电源供电时可承受及传输-5V至+5V的任何信号,所以可安装在电平转换器的任何一侧。由于至多路复用器的Arduino连接多于Pmod连接,所以将MAX14611安装在电平转换器的Arduino很有意义。按照这种方式,Pmod连接器处只需要两片4通道器件(图3)。

图3. 建议方案的逻辑图。

方案评估

该方案的关键是每个通道支持同时多个连接。COM引脚不连接,但在复用器内部用于选择连接。MAX14661的16个复用连接中的8个专用于Pmod连接器,也连接至4路支持SPI的信号和4路其它GPIO(图3)。其它8个复用连接绑定至2线串行总线和其它时间关键信号,例如PWM或定时器引脚。例如,为实施I2C类型,只需配置复用器,在通道A上使能SDA引脚和Pmod引脚4,在通道B上使能SCL和Pmod引脚3。通道A和B是任意选择的,可随意交换。实际上,甚至可以使能Pmod连接器上第二排的引脚3和4,以访问另外的6引脚I2C Pmod。如果I2C器件的地址不同,甚至可使两个端口保持工作状态,或者动态激活,以支持相同地址的两个器件。使用跳线方法,根本不可能在两个具有相同地址的器件之间进行动态切换。使用MAX14661,能够以编程方式配置所有指定的Pmod类型,甚至非标准类型,而只需单片尺寸仅为4mm X 4mm的有源器件。

为什么有人设计非标准Pmod?原因之一是与微控制器相同的引脚复用问题。例如,MAX14661支持I2C和SPI控制,取决于配置引脚的状态。MAX14661的外设模块的引脚排列与SPI Pmod类型相匹配,但时钟和数据引脚与Digilent Pmod规范规定的I2C引脚不匹配。适配卡上的MAX14661可将SDA和SCL信号映射到任意Pmod引脚,可用于支持非标准MAX14661外设模块、I2C引脚映射。MAX14661也有两个地址引脚,以支持4个不同的I2C器件地址。因此,可将系统设计为支持同一总线上的多个器件。

使用MAX14661复用I2C总线时,在带内发送命令。切换将与I2C总线同步生效。当然,在带外复用I2C总线具有挑战性,因为如果不小心,会在从机将SDA线拉低时断开;下次选择该总线分支时,分支可能锁死。MAX14661始终在I2C写命令结束时转换总线,此时开关另一侧的器件应为空闲。

-

FPGA

+关注

关注

1634文章

21830浏览量

607966 -

Arduino

+关注

关注

188文章

6479浏览量

188550 -

Pmod

+关注

关注

0文章

22浏览量

8183

发布评论请先 登录

相关推荐

如何使用Arduino实现CAN总线通信

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

基于Fpga的Pmod与Arduino接口映射

基于Fpga的Pmod与Arduino接口映射

评论