引言:UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可实现全双工传输和接收。UART通常用来实现与PC之间数据通信,命令和控制信息的传输等。本文我们介绍UART通信协议、传输时序及如何利用HDL编程实现FPGA与PC通信。

1.异步串行通信的理解

首先需要介绍几个概念。

通信协议:指双方实体完成通信或服务所必须遵循的规则和约定。交流什么、怎样交流及何时交流,都必须遵循某种互相都能接受的规则。这个规则就是通信协议。

串行通信:是指通信双方按位进行,遵守时序的一种通信方式。串行通信中,将数据按位依次传输,每位数据占据固定的时间长度,即可使用少数几条通信线路就可以完成系统间交换信息,特别适用于计算机与计算机、计算机与外设之间的远距离通信。

异步通信:它是对于同步通信来说的,异步通信在发送字符时,所发送的字符之间的时隙可以是任意的,当然,接收端必须时刻做好接收的准备(如果接收端主机的电源都没有加上,那么发送端发送字符就没有意义,因为接收端根本无法接收)。发送端可以在任意时刻开始发送字符,因此必须在每一个字符的开始和结束的地方加上标志,即加上开始位和停止位,以便使接收端能够正确地将每一个字符接收下来。

2.UART通信协议介绍

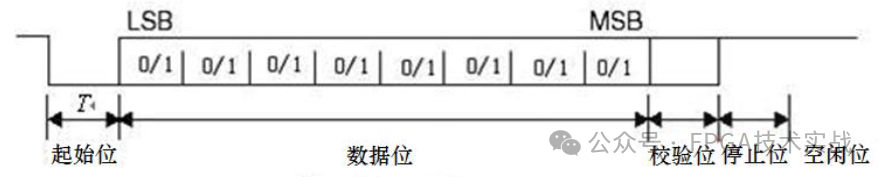

UART使用的是异步串行通信机制,其数据传输协议格式如下图所示。

图1:UART数据传输协议格式

其中各位的含义如下:

起始位:先发出一个逻辑”0”信号,表示传输字符的开始。

数据位:可以是5~8位逻辑”0”或”1”。如ASCII码(7位),扩展BCD码(8位)。

校验位:数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验);数据的奇偶校验位是可以选择的,如果不使用奇偶,那么就没有这个数据位。

停止位:它是一个数据字段的结束标志。可以是1位、1.5位、2位的高电平。

空闲位:处于逻辑“1”状态,表示当前线路上没有数据信息传输。

UART数据传输协议格式,通常需要在收发设备提前定义好,如传输数据的位数、是否需要校验位、停止位。另外还一个重要的参数就是数据传输的波特率。

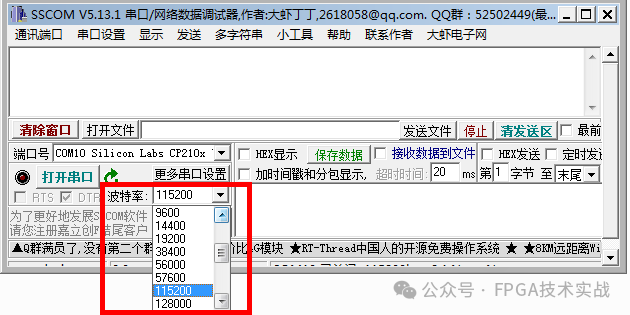

图2:常见标准波特率

UART数据传输的速度通常用波特率来衡量。在一次串口通信过程中,数据接收与发送双方没有共享时钟,因此,双方必须协商好数据传输波特率。根据双方协议好的传输速率,相邻bit的时间间隔就会固定下来,接收端即可对发送端的数据进行采样。

标准波特率:包括2400bps、4800bps、9600bps、19200bps、38400bps、57600bps、115200bps等。当然更块的速度意味着对采样的要求更高,有可能误码率会逐渐提高。

3.数据传输工作流程

本文设定传输协议为:1位起始位+8位数据位+1位结束位,无奇偶校验位,传输波特率为9600bps。

(1)发送端按照预先设定好的传输协议及波特率,发送端依次发送:

1bit数据起始位+8bit数据位+1bit停止位

其中,起始位为逻辑 0(低电平) ,结束位为逻辑 1(高电平) ,发送端在空闲状态为 1 。

(2)接收端:接收端通过检测电平“1”(空闲状态)到“0”(起始位)的跳变来确定一个数据包的开始。确定开始位接收完成之后,依次接收数据使用更高的采样时钟,完成数据采集。接收完数据位后,继续接收停止位。

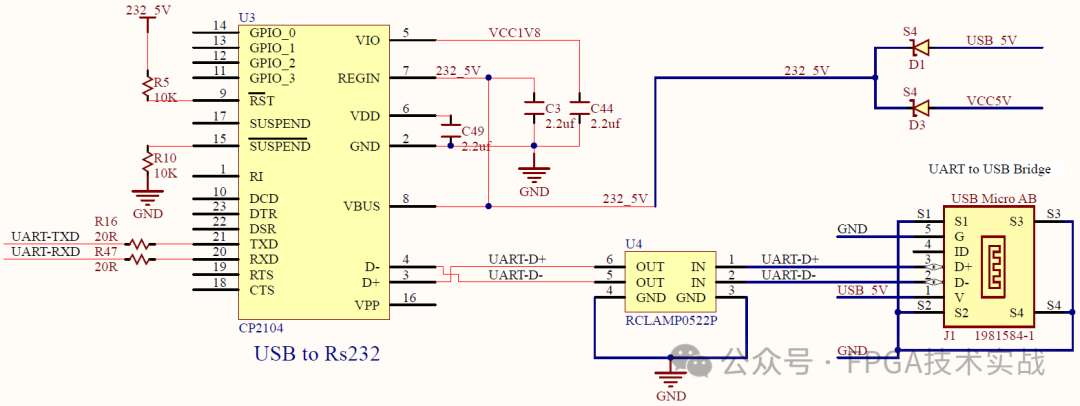

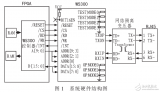

4.硬件介绍

硬件上采用USB转RS232芯片CP2104实现PC与FPGA之间通信。电路中设计了一片ESD静电防护芯片RCLAMP0522P,与转换芯片CP2104一起,可以防止静电浪涌烧毁FPGA芯片,起到隔离保护作用。

图3:USB转RS232电路图

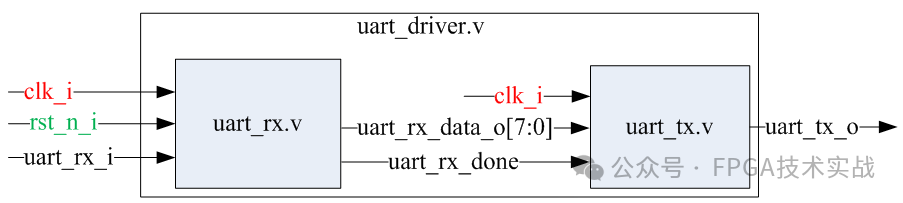

5.软件设计

软件设计划分为接收模块uart_rx.v和uart_tx.v两个模块,顶层模块uart_driver.v互联两个模块,如下图所示。

图4:软件模块划分

UART数据传输主要包括两个部分:

波特率的产生设计;

数据传输设计,包括接收与发送。

(1)波特率产生设计:

板载 FPGA 输入时钟 100Mhz,为得到常用的波特率,采用计数分频来得到。BAUD_DIV=100000000/ 波特率。其中采样中心点为发送或接收时钟的中心点,即 BAUD_DIV_CAP= 100000000/(2*波特率) 。

(2)数据传输设计

数据接收模块:在设置好传输波特率9600bps下,根据串口传输时序,进行解串(串并转换)。空闲状态时,接收数据为逻辑高电平,等待起始位逻辑低电平的到来。当起始位到达后,由低位到高位,依次采集8位数据,并进行相应的解串,存入临时寄存器。接收有效数据完成后,判断结束位,接收完毕。

数据发送模块:设置发送使能信号和待发送的数据。通过计数器,表示10 个数据发送的周期。这 10 个数据,依次为:1位起始位+8 位数据位 +1 位结束位,实现数据位的逐个发送。本设计中,采用PC机的串口调试助手,发送数据位至FPGA。FPGA 接收到数据位之后,立即回传至 PC 机。

6.软件功能仿真与测试

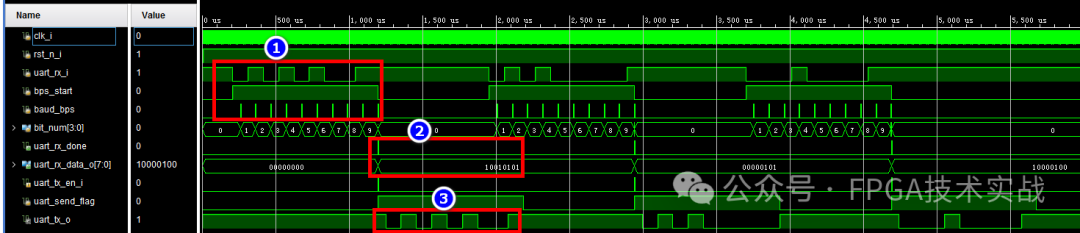

编写testbench仿真文件,利用Vivado自带仿真器对软件代码进行功能仿真,仿真结果如下图所示。

图5:UART串行通信仿真

图中①处,仿真UART接收串口信号uart_rx_i输入数据8'b10101001,baud_bps在每个bit位宽中间时刻采样,bit_num计数接收到的数据bit个数,数据按照LSB端接收;

图中②处完成8bit数据位接收后,产生接收完毕信号uart_rx_done;

来源: 本文转载自FPGA技术实战公众号

-

通信协议

+关注

关注

28文章

922浏览量

40583 -

uart

+关注

关注

22文章

1245浏览量

102149 -

串口通信

+关注

关注

34文章

1629浏览量

55983 -

异步串行通信

+关注

关注

0文章

16浏览量

8472

原文标题:FPGA入门基础之UART串口通信设计

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

UART通信协议

SPI总线工作原理/数据传输步骤/优缺点

STM32简单数据传输方法与通信协议(适合串口和一般总线)精选资料分享

以太网数据传输系统的设计与应用介绍

UART通信协议介绍和数据传输工作流程

UART通信协议介绍和数据传输工作流程

评论