引言:本文描述了一种简单高效配置FPGA的方法,该方法利用微处理器从串行外围接口(SPI)闪存配置FPGA设备。这种方法减少了硬件组件、板空间和成本。

1. 介绍

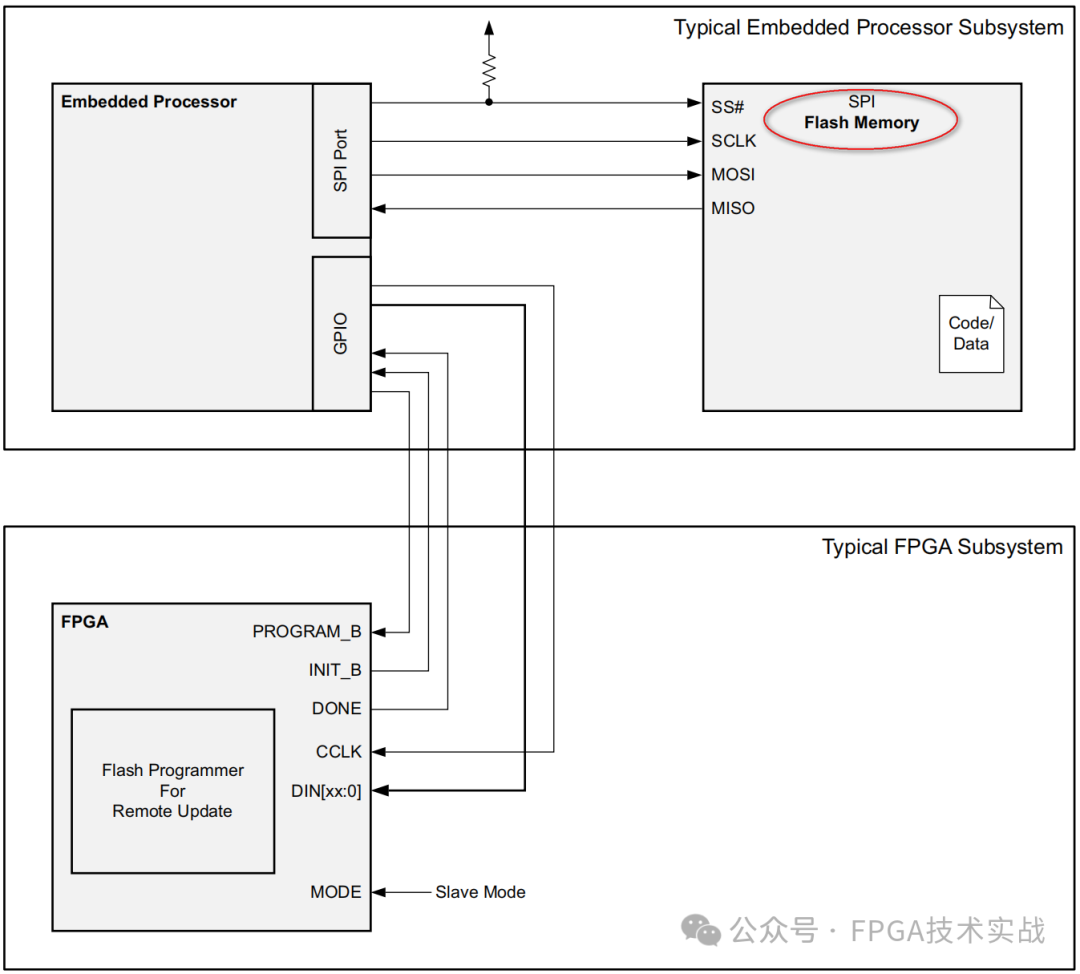

产品中包含分立的嵌入式微处理器和FPGA是常见的,带FPGA的典型嵌入式微处理器系统如图1所示。这些类型的系统包括两个典型的子系统,子系统具有独立的SPI Flash配置芯片。

图1:带FPGA的典型嵌入式微处理器系统配置方法

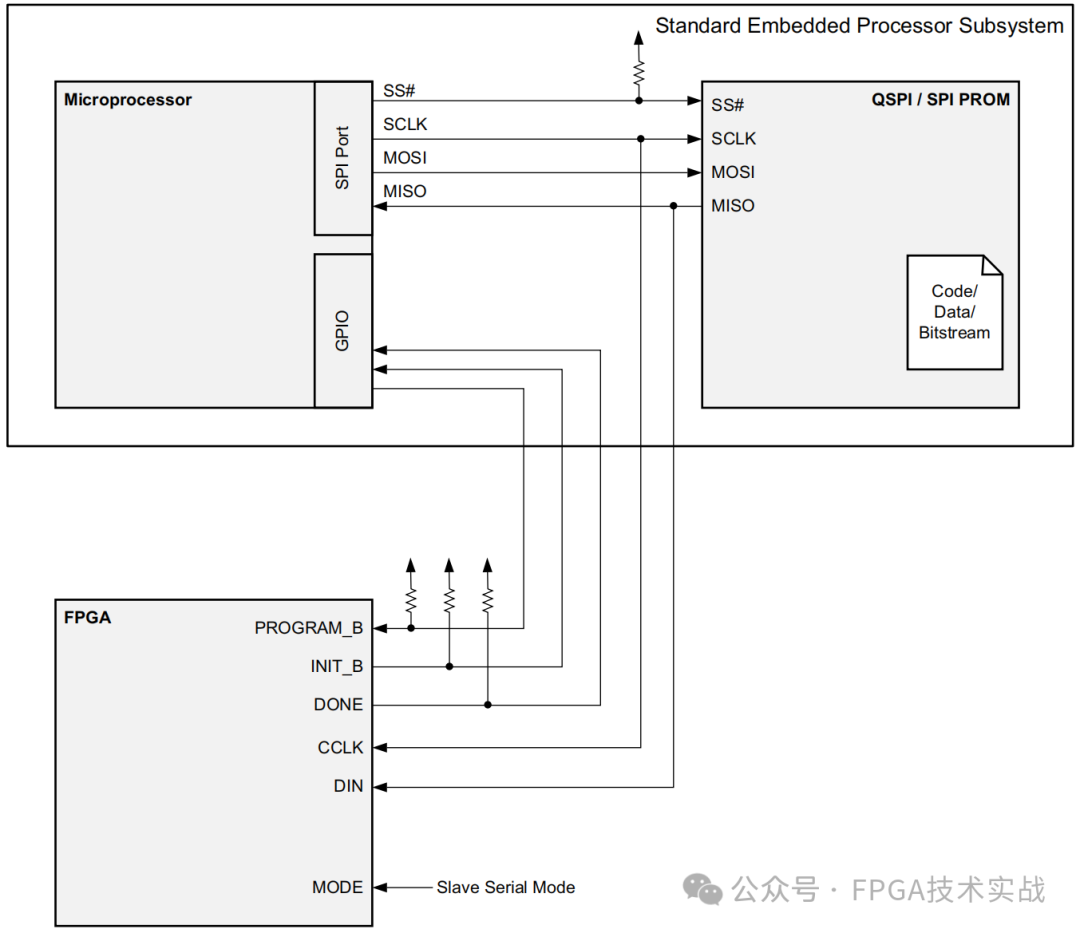

XAPP583中描述了利用微处理器配置FPGA的推荐方法。这种方法是将用户固件以及配置位文件存储在连接到微处理器的Flash设备上。微处理器通过SPI接口读取比特文件,然后通过从串行或从SelectMAP接口将比特流发送到FPGA。这消除了对FPGA配置的额外PROM的需要。框图如图2所示。

图2:XAPP583文档配置嵌入式微处理器系统方法

本文描述的方法进一步简化了配置方案。它利用了FPGA的从串行配置引脚与标准SPI总线信号之间的兼容性。图3展示了微处理器、Flash和FPGA之间的连接。

图3:本文档配置嵌入式微处理器系统方法

如图3所示,连接到微处理器的Flash存储用户固件和FPGA比特文件。然而,微处理器并不直接通过FPGA配置端口来配置FPGA。相反,FPGA从串行DIN和CCLK引脚连接到Flash和微处理器之间的SPI总线。通过这种方法进行配置是可能的,因为从串行接口和配置序列与SPI协议一致。操作和实施详细信息部分更详细地解释了兼容性。

此方法可以使用两个连接。您只需要连接以下引脚即可将配置位流传输到目标FPGA:

•FPGA CCLK引脚连接到SPI总线SCLK引脚。

•FPGA DIN引脚连接到SPI总线MISO引脚。

还可以包括用于配置控制或监控的附加信号。以下FPGA引脚应连接到微处理器GPIO引脚以启用功能:

•PROGRAM_B:重置FPGA配置序列。

•INIT_B:检查配置初始化或错误状态。

•DONE:监控配置成功。

与图1中所示的带有嵌入式微处理器和Flash的传统系统相比,此解决方案提供了多种优势:

•减少了组件数量:系统只需要一个Flash;

•更少的微处理器GPIO和更少的代码空间:与其他基于嵌入式微处理器的配置解决方案相比,可以改善配置时间。

•基于微处理器的FPGA配置控制和监控功能:超过了本地FPGA配置功能。

•系统内PROM更新:此解决方案支持在微处理器上使用标准Flash编程库来更新存储的比特流。

2. 操作和实施细节

本节介绍FPGA从串行配置接口和时序,以及使用Zynq-7000 AP SoC处理子系统配置FPGA的方法。

2.1 FPGA从串行配置模式

从串行模式(FPGA配置模式之一)由于其简单性而高效。下面列出了它的一些关键属性。本应用说明中描述的配置方法利用了这些属性。

2.2 简化配置方法

如果系统通电后只需要配置一次FPGA,那么配置方法可以很简单,只需连接以下引脚即可:

•FPGA CCLK引脚连接到SPI总线SCLK引脚。

•FPGA DIN引脚连接到SPI总线MISO引脚。

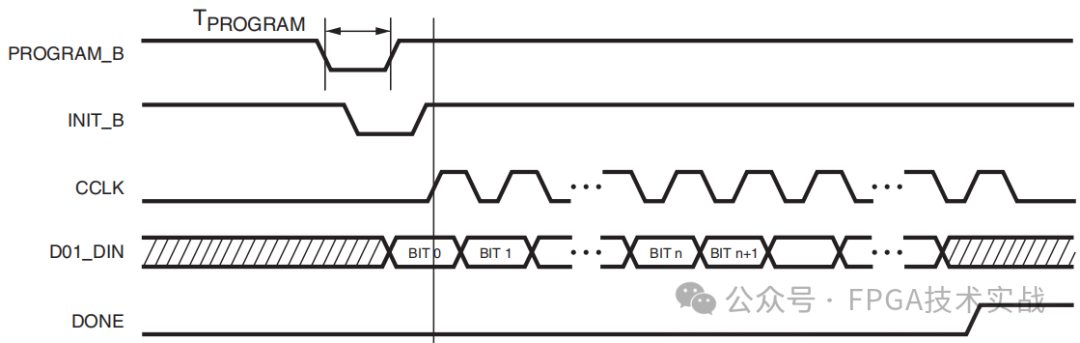

在Zynq-7000 AP SoC开始配置之前,FPGA应准备好接收配置数据。换句话说,FPGA应该已经完成了从初始通电开始的配置空间的擦除阶段。

图4:FPGA配置时序图

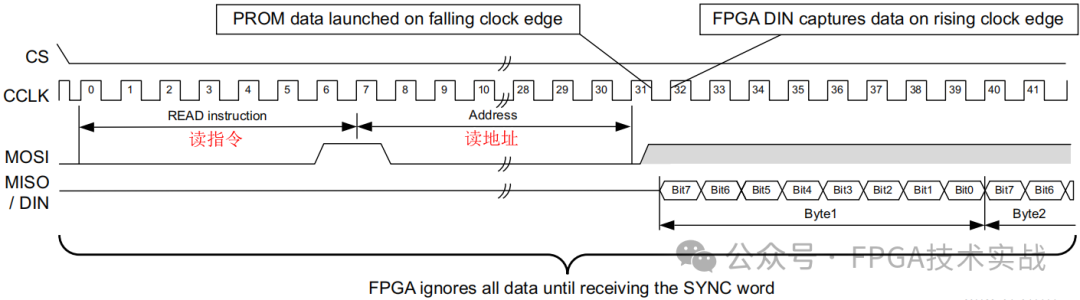

接下来,Zynq-7000 AP SoC向SPI Flash发送单个读取命令,并从SPI Flash读取整个比特流。在SPI Flash串行读取操作期间,比特流也通过SPI总线MISO信号串行传输到FPGA DIN引脚。SPI Flash在SCLK/CCLK的下降沿上输出每个串行数据位。FPGA在SCLK/CCLK的下一个上升沿捕获串行数据位。在从SPI Flash读取整个比特流时,FPGA被有效地配置。

FPGA配置接口的三个特性使FPGA DIN和CCLK引脚能够直接连接到用于FPGA配置的SPI总线:

•SPI总线串行数据(MISO)和时钟(SCLK)信号分别与FPGA从串行数据(DIN)和时钟引脚兼容。

•FPGA配置接口在比特流读取操作之前忽略所有SPI总线活动。因为FPGA丢弃所有传入数据,直到它接收到有效的32位同步字,所以有效地忽略了所有SPI总线活动。

•配置操作完成后,FPGA配置接口忽略所有SPI总线活动。由于FPGA在配置完成后停止监测其DIN输入,因此FPGA有效地忽略了位流读取操作后的所有SPI总线活动。

图5说明了SPI总线和FPGA配置事务的关系。

图5:SPI与FPGA之间时序关系

2.3 带有附加控件的配置方法

另一种增强配置操作和能力的方法是使用Zynq-7000 AP SoC来控制FPGA配置引脚。例如,Zynq-7000 AP SoC可以使用其GPIO引脚驱动FPGA PROGRAM_B引脚来清除FPGA配置Flash并重新启动配置。这允许基于系统操作条件来重新配置用户设计。它可以为某些用户设计提供巨大的优势,这些用户设计受益于操作过程中的功能变化。

此外,Zynq-7000 AP SoC可以通过将其GPIO引脚连接到FPGA DONE和INIT_B引脚来监测FPGA配置准备情况和结果。INIT_B是一个配置错误或就绪信号。DONE信号是一个配置完成指示器。这些状态信号为Zynq-7000 AP SoC提供信息,以做出有效决策,确保可靠配置。

例如,从配置故障中恢复的一种流行方案称为配置回退。如果Flash中的目标位文件损坏,则用户设计不进行配置,FPGA也不起作用。在这种情况下,固件通过检查INIT_B和DONE信号来检测情况。然后,它通过使用Flash中的已知良好(golden)位文件重新配置FPGA来缓解问题。这使FPGA达到已知的功能状态,以避免灾难性的系统故障。

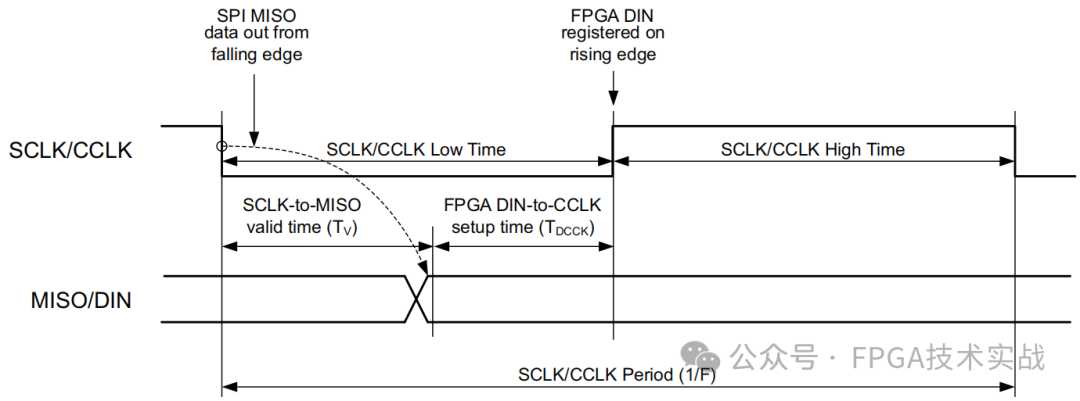

2.4 SPI总线SCLK最大频率

SPI总线上的数据在相反的时钟边沿上被启动和捕获。SCLK频率的限制因素是最小SCLK/CCLK低时间。如图5所示,它由从SCLK的下降沿到CCLK的上升沿的SPI Flash MISO输出数据有效时间和FPGA DIN输入设置时间之和决定。

图6:SPI总线到FPGA时序

以下等式估计SPI总线支持FPGA配置的最大SCLK频率:

其中:

•TV=SPI Flash SCLK到MISO数据输出有效时间。

•TDCCK=FPGA DIN输入设置到CCLK设置时间。

•SCLKLow duty cycle %, minimum=时钟周期内SCLK低的最小百分比。

为了获得更准确的估计,SCLK/CCLK和MISO/DIN信号的PCB走线路径和相应传播延迟的适用分量应纳入上述方程式。

此外,SCLK信号(FPGA CCLK引脚)的信号完整性至关重要。为了实现最大可能的时钟频率,请使用最佳实践来设计并将此时钟信号从Zynq-7000 AP SoC路由到SPI Flash和FPGA端点。

3.参考设计

本文提供了一个示范参考设计。它使用Zynq-7000全可编程SoC(AP SoC)和目标板上的FPGA实现了图2所示的解决方案。您可以从Xilinx网站下载本应用说明的参考设计文件。表1显示了参考设计矩阵。

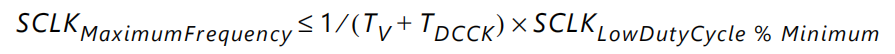

3.1 硬件设计

硬件设计基于Zynq-7000 AP SoC 7Z045 CLG484器件。AP SoC Quad SPI控制器连接到支持SPI x1、x2或x4宽度的多I/O存储器设备。尽管Zynq Quad SPI控制器也可以支持x1、x2、x4和x8宽度,但此参考设计适用于使用单比特总线宽度的传统SPI协议。下图显示了Zynq-7000 AP SoC、SPI PROM和Kintex-7 FPGA之间的硬件连接。

图7:示例硬件原理图

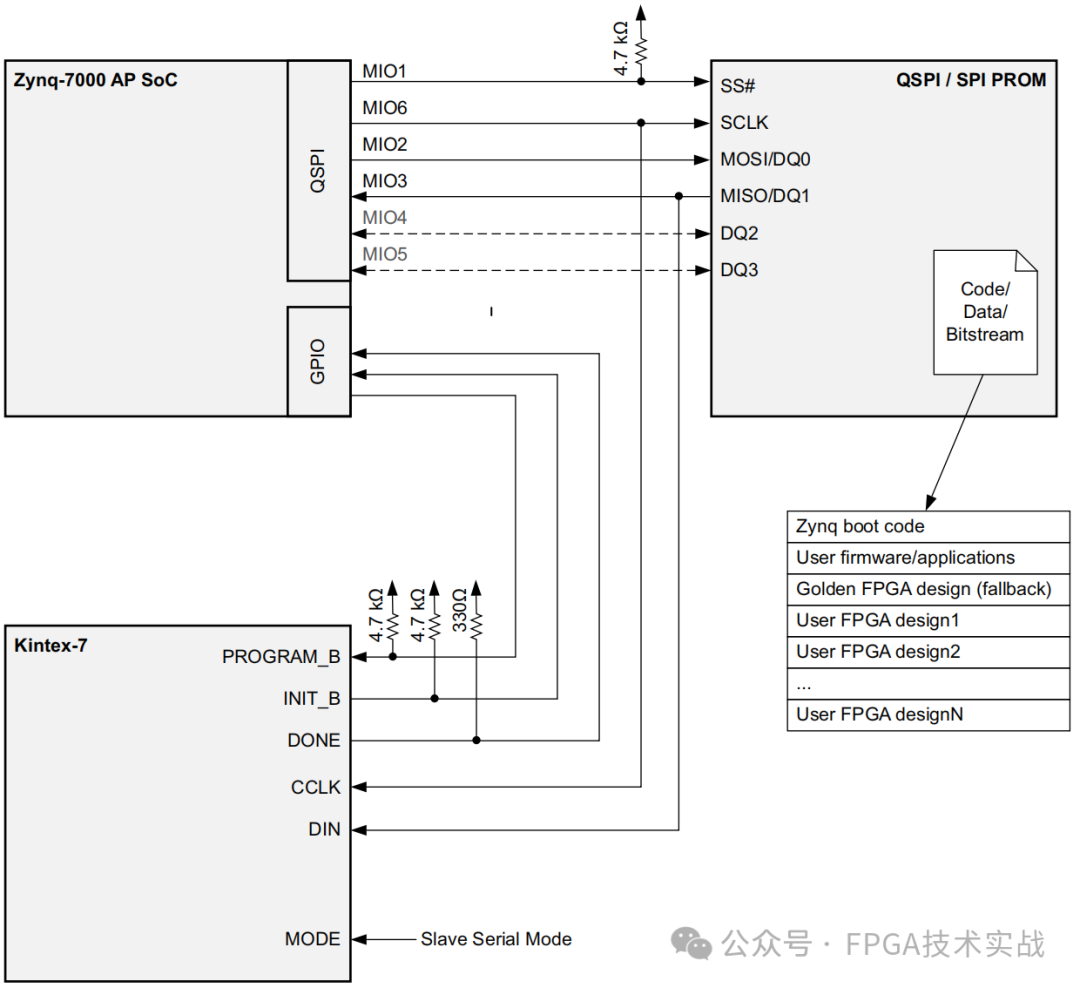

参考硬件设计在Vivadodesign Suite项目中提供。AP SoC内的系统框图如图8所示。

图8:Vivado实现框图

3.1 固件流程

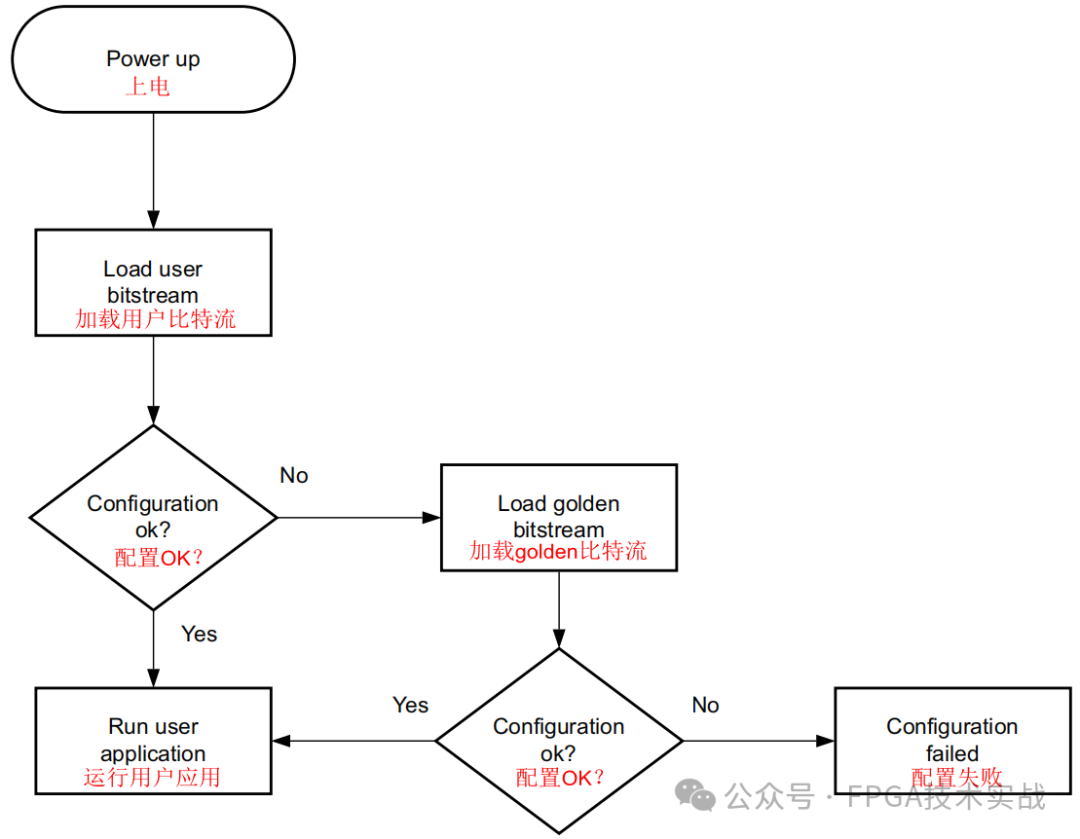

参考设计利用存储在SPI Flash中的更新的(最新设计修订版)比特流和Golden(已知良好的)比特流来实现尝试和回退配置方案。Zynq-7000 AP SoC固件首先尝试加载最新的预期比特流。然后,如果配置不成功,固件将重新启动配置并加载黄金比特流。此过程称为回退配置。固件流程图如图9所示。

图9:固件加载流程图

固件配置算法的详细信息:

(1)将Zynq-7000AP SoC Quad SPI接口配置寄存器初始化为I/O模式。

•执行诸如设置时钟分频器、芯片选择模式和启用控制器等任务。

(2)清除FPGA配置内存。

•断言PROGRAM_B的时间段至少比TPROGRAM长,然后取消断言。

(3)等待INIT_B释放。

•轮询INIT_B引脚,以确保FPGA已完成房屋清洁阶段。

(4)设置Quad SPI控制器传输功能。

•演示使用轮询数据传输函数XQspiPs_PolledTransfer()。功能原型为:int XQspiPs_PolledTransfer(XQspiPInstancePtr,u8SendBufTr,u8*RecvBufPtr,unsigned ByteCount);

•InstancePtr是指向Quad SPI实例的指针

•SendBufPtr和RecvBufPtr分别是发送和接收缓冲区指针。此功能要求发送和接收缓冲器的字节数与将重新配置FPGA的比特流的长度相同。

•ByteCount是要传输的字节数。

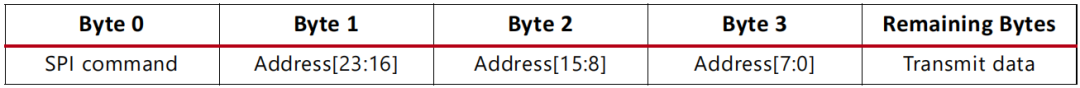

•发送缓冲区的第一个字包含命令和地址,如表2所示。第一个字节包含用于Quad SPI存储器设备的命令。在这种情况下,它将发送读取字节命令(0x03)。只需要一个命令即可完成整个操作。目标比特流的24比特起始地址被划分为三个字节。缓冲区其余部分的内容是未定义的,因为这是一个读取操作。

表2:Quad SPI写入缓冲区定义

(5)呼叫轮询传输功能

•调用该函数后,Quad SPI控制器将发送缓冲区的内容发送到Quad SPI存储器。同时,它读取的字节数与比特流的大小相同。由于FPGA的DIN和CCLK引脚连接到SPI控制器的MISO和SCK信号,当检测到SYNC字时,FPGA(设置为从串行配置模式)将开始配置。FPGA是在比特流被完全读取时配置的。

(6)检查错误

•配置FPGA后,如果INIT_B和DONE被断言,则这表示成功读取结束。

•但是,如果INIT_B和/或DONE引脚保持低位,固件将加载已知的良好配置(即Golden比特流)并重新配置FPGA。这被称为配置回退。

4.结论

本文介绍的FPGA配置解决方案降低了包含微处理器、SPI Flash和FPGA的典型系统的硬件和固件要求。它利用了FPGA串行配置模式和SPI存储器之间的兼容性。

-

FPGA

+关注

关注

1664文章

22553浏览量

640498 -

嵌入式

+关注

关注

5212文章

20746浏览量

338440 -

FlaSh

+关注

关注

10文章

1761浏览量

156064 -

微处理器

+关注

关注

11文章

2440浏览量

86256 -

SPI

+关注

关注

17文章

1904浏览量

102400

原文标题:基于微处理器实现SPI Flash配置FPGA设计

文章出处:【微信号:FPGA技术实战,微信公众号:FPGA技术实战】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一种基于FPGA的UART实现方法设计

Nexar如何为FPGA设计提供一种全新的方法?

一种基于ARM-Linux的FPGA程序加载方法

一种密钥可配置的DES加密算法的FPGA

一种基于SRAM的FPGA的加密方法

一种通用SPI接口的FPGA设计与实现

一种简单高效配置FPGA的方法

一种简单高效配置FPGA的方法

评论