电路可靠性 , 亦即电路抗电气故障的鲁棒性(robustness) , 已日益成为IC设计师的关注点。其中的很多问题多年来已为人所知,有时人们觉得可靠性风险主要是最新制程世代才会面临的问题。诚然 , 越小的器件、越细的导线、越薄的栅氧化层越容易受到过度电性应力(EOS)的影响 , 而新制程世代 , 对特定版图形状和图案也更为敏感。然而 , 如果设计师认为在成熟节点上不存在电路可靠性问题的话 , 那他今后的项目(project)很可能会面临一些潜在风险。

这是为何?

因为即使是在成熟的制程上 , 工程师们也会从上面不断榨取性能、功能、面积及其他相关指标 , 以期获得更高的投资回报(ROI)。越老的制程的不确定性可能会越少 , 但每一轮新的设计浪潮都会因为有不同的应用需求、及环境条件而引发新的可靠性问题。例如 , 汽车和医疗相关应用芯片设计目前是采用成熟制程技术的新驱动力量。这些应用和采用前沿制程的常见消费型应用相比 , 具有完全不同的设计需求及工作环境。

这样就需要有新的工具和方法 , 来确保新制程和成熟制程的电路可靠性。例如, 汽车设备上更高的电压导致了更高的EOS风险 , 因此设计师需要更努力来确保具有较薄的栅氧化层的数字晶体管不会连接到50伏的电源上。不仅如此,采用高压设计的电路也需要增大特定位置上的版图图案间间距。

针对这样设计的验证 , 我们只需要检查某些特定区域即可 , 如果将整个芯片都执行符合高压设计规则的较大间距DRC检查 , 则将导致极端保守的设计考虑 , 以及过大的裸片面积和更高的制造成本。

有限的传统方法

很多设计团队采用用户生成(user-generated)的标志层(marker layers)或文本点(text points)来检查EOS问题 , 但这是容易出错的方法 , 需要设计师人工判定电压如何在电路节点之间变化、并人工标出需要符合高压设计规则的正确区域。随着电路功能的密集改版更新 , 标志层(marker layers)是极难保持的。

在芯片设计日益复杂的今天 , 我们也面临了其他的风险:静电放电(ESD)、闩锁(latch-up)、电迁移(EM)等已知故障机制不能为标准设计做法所完全防止。

其中电迁移在很多代IC上一直是困扰设计师的问题。然而 , 结合了更高驱动强度和采用更细导线在14/16nm实现的FinFET技术 , 成为因电迁移而产生的电路故障的另一个起因。采用传统方法进行EM检查 , 将耗费巨大的运算资源 , 需要在整个芯片的每一个部分都提取寄生模型、进行电流仿真和标注最后结果。常见的16nm/14nm片上系统会有数十亿个组件 , 想当然耳 , 而进行这样的传统检查过程将非常缓慢 , 是不可接受的。

此外也因为目前所制造的晶体管栅极下的氧化层更薄 , 使得相关器件更容易受到EOS的影响。更困难的是 , 由于现代省电芯片的设计 , 大多数都采用多电源域(multi-power-domain)的策略 , 意味着一个芯片可能有着数十个不同的电源供电。这种更大的复杂性使得检查出完整的潜在EOS问题变得极度困难。实际上 , 整个芯片的EOS检查超出了以往各种工具所提供的标准电路仿真和验证方法的能力。

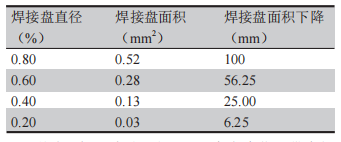

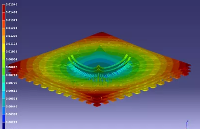

图1:电路检查包括去耦电容布局、几何尺寸匹配及电流密度检查。

解决老问题 , 需要新方法

过去 , 设计师们依赖电路仿真(circuit simulation)、设计复核(desgin review)、也使用了 标志层(marker layers)或文本点(text points)进行特定区块的设计规则检查(DRC)、当然还有其他“自创”方法来查找可能的电路可靠性问题。

但是今天,由于上述所有挑战 , 要确保一个设计能不出现潜在的可靠性问题 , 就需要一种整体的验证策略 , 这种策略要能够实现 电路架构的分类及其相关版图位置的搜寻、金属导线的寄生电阻测量、金属导线的电流密度计算 以及特定区块的DRC检查等。

人工方法即将被取代 , 转而使用可执行电路架构的分类 , 并能识别出相关的电路节点及其版图位置 , 然后对各种电路类型或问题 , 执行相对应的静态和动态分析的工具。

这些工具能快速并完整地分析每一器件以及其每个端点的可能的电压。有了这个信息 , 即可计算整个芯片 , 每一电路节点及其相对应的版图位置的所有可能电压、并能进行非常精确和高效的OVD检查 , 这也就是说可以根据两个版图图案间不同的电压差,定义出不同的最小可容许距离的设计规则并用此一工具进行验证。

这些工具还可识别易受到电迁移影响的电路节点及其相对应的版图位置、测量两点间金属导线的寄生电阻、并执行相对应设计规则验证、来检测潜在问题。

此外,由于这些问题很多都出现于大型芯片里 , 因此除了完整的功能外, 更需要高效、简洁的验证工具 , 以便快速找出电路错误的原因。随着具有这些功能的新工具出现 , 我们现在看到了有数家晶圆代工厂,已开始在提供这一领域的相关验证解决方案。

但这仅仅是EDA一个新领域的肇始,预计在很长的一段时间里, 我们将会持续使用这样的工具, 处理以前“无法检查的”电路可靠性问题的验证。

没有一家汽车厂商会接受未在严格的高温条件下进行了验证的发动机控制芯片,而医疗厂商所生产的起搏器(pacemaker)则必须在很长的寿命期内可靠地工作。

此外 , 还有一些新的电路架构在成熟的节点被首次推出时 , 还尚未被发明出来。包含更多模拟电路、更高电压(比如汽车上的50V)、更高的频率还仅仅是电路设计师所面临的、不断变化的设计要求中的一部分。

-

IC

+关注

关注

36文章

5957浏览量

175738

发布评论请先 登录

相关推荐

GND连接对系统可靠性的影响

PCB高可靠性化要求与发展——PCB高可靠性的影响因素(上)

先进IC设计中如何解决产热对可靠性的影响?

基于可靠性设计感知的EDA解决方案

汽车功能安全与可靠性的关系

请问FATFS文件系统可靠性如何?

线路板变形对电路性能和可靠性有影响吗?

如何确保IGBT的产品可靠性

IGBT的可靠性测试方案

检查IC设计的电路可靠性

检查IC设计的电路可靠性

评论