集成电路 (IC) 设计团队通常在预定最后送交制造(tapeout)期限临近时承受着巨大的压力。更糟糕的是,他们往往还面临着后期工程变更命令 (Engineering Change Order),这些可能导致额外的耗时工作,例如由于一个小的变更就需要全部重新对布局进行填充。对于45纳米及以下的情况,新的制造要求不仅大大提高了金属填充位置的复杂性,还显著增加了设计中填充组件的数量。填充的目的已经有所变化,以前是为了确保整个布局内最低的金属密度,而现在是为了达到最大的目标密度。此外,开发密度梯度检查是为了确保相邻位置内的填充密度之间能够顺利过渡。对于20纳米及以下的情况,填充要求还必须包括符合多重曝光限制以确保光罩平衡,且设计工程师不仅需要在后段制程 (BEOL) 金属和导孔层(via)上添加多层的填充并且在前段制程 (FEOL) 的各层也需要添加。

所有这些有关填充的变化要求复杂的新型填充类型和填充策略的支持,因为填充不再只影响平坦性问题,且已经拓展到多个可制造性问题。填充现在还直接影响着设计的性能。如基于单元的填充和 多重曝光 感知填充等技术已经被开发并整合到填充引擎中,为设计团队提供了一种可以从自动布局布线(P&R)工具直接调用的自动填充流程,以确保其能够便利地开展设计流程,并获得正确的设计结果。然而,为了得到准确且经过优化的填充位置,设计人员需要一个特别调整的环境以应对不断增加的新的检查和限制要求。

布线工具是用来创建数以百万计的连接,不符合复杂的跨层填充要求。新技术中填充图形的数量有可能超过十亿个新对象,这让 P&R 系统面临的挑战变得更加复杂。送交制造 (Tapeout) 过程中较晚出现的 ECO 必须得到高效准确的处理,否则替换填料和重新确认时序的复杂性可能对档案大小、运行时间和时序收敛产生不利影响,进而导致送交制造交付延迟。为了平衡时序分析 在P&R 系统运行时间,EDA 行业已经开发出一种流程,让所有填充图形都存放在磁盘的一个单独档案中,使用提取工具将它们与版图档案结合起来。这种流程在计算时序的影响时并不会减慢后端的流程。

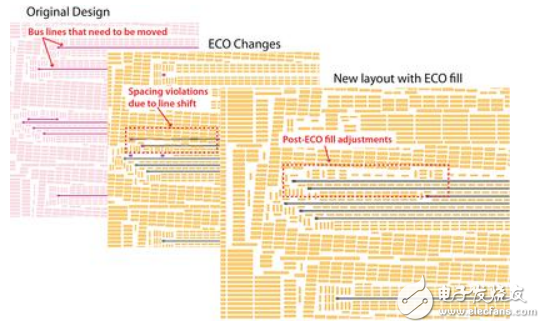

为了解决这些问题,有效的 ECO 填充策略必须是准确快速的,同时只能集中处理被 ECO 影响的设计部分。藉由删除并替换该区域内填充,并仅重新验证受影响区域内的时序,我们可以减少运行时间,管理文件大小,尽量减少时序的影响(图1)。藉由严格限制 ECO 填充操作只在实际光罩制作发生变化的地点,我们能限制必须对误差进行评估、编辑和重新填充的区域的大小。这种面积减少方法先是生成排除区域,然后将可填充数据库剪裁到仅包含设计 ECO 周围的区域。如果设计人员可以使用与晶圆代工相同的设计规则检查 (DRC) 签核工具,更准确地减少这些区域这工作就会变得更加简单。

图1、填充 ECO 策略可以调整在 ECO 变更周边的填充,不需要为整个版图全部重新生成填充,节省了送交制造最后期限的宝贵时间

还有一个问题是数据库的大小。仅删除 ECO 区域周围的填充图形需要将填充层次结构平面化,这可能导致填充数据库呈现爆炸性膨胀。为解决这个问题,智慧的 ECO 填充技术先找到包含与 ECO 设计图形冲突的需要删除的填料的单元,再将填充层次结构中最低层次上的最少数量的单元进行平层化。然后它仅重新填充发生 ECO 变更的区域,而不是重新填充整个芯片。

藉由严格限制ECO填充操作只在实际光罩制作发生变化的地点,我们能限制必须对误差进行评估、编辑和重新填充的区域的大小。这种面积减少方法先是生成排除区域,然后将可填充数据库剪裁到仅包含设计 ECO 周围的区域。显然,这里有一个平衡点,如果要被重新填充的面积过大,那么这种策略无法保证规模和精度。一般来说,ECO 填充策略只有在变更影响不足1%的设计区域时是最有效的。不止如此,实际上,ECO 填充流程的运行时间可能超过正常填充流程的时间。然而,在这种情况下,设计人员还必须考虑尽量减少时序的影响和光罩的成本能否抵消运行时间上的劣势。

多个小的变化区域比较适合选择 ECO 填充策略,例如门(gate)功能的变化,这些变化要求在有限区域内进行局部路径重绕。要变更整个区块更为有效率的方法,只需要从头重新填充设计,在这些情况下,分层做法是个不错的选择。

为了充分利用这些新的填充技术,不只是工具需要提供所需的功能,而晶圆代工厂还要提供使流程变得易于使用的支持文件也是至关重要的。随着设计人员逐渐掌握 ECO 填充技术,将来他们能够在其设计过程中使用这些技术,更好地管理后期设计变更,维护先进制程设计的送交制造进度。

-

IC设计

+关注

关注

38文章

1295浏览量

103920 -

时序

+关注

关注

5文章

387浏览量

37318 -

ECO

+关注

关注

0文章

52浏览量

14885

发布评论请先 登录

相关推荐

数据类型不一样和接口 怎么解决

为什么c语言中a和b的值不一样,c和d的值不一样?

可穿戴设备的发展会给物联网带来什么不一样的改革吗?

Linux 内核新增的异构内存管理(HMM)会带来什么不一样?资料下载

ECO填充工具带来不一样的IC设计

ECO填充工具带来不一样的IC设计

评论