2016年7月正式发布的2015年国际半导体技术路线图(ITRS)做出预测,经历了50多年的微型化,晶体管的尺寸可能将在5年后停止缩减。

该报告预测,2021年之后,对各公司来说,继续缩小微处理器中的晶体管将不再是一种经济的做法。芯片制造商们将转而采用其他方式提高晶体管密度,即将晶体管布置结构从水平变成垂直,建立层层相叠的多层电路。

一些人认为,这种变化可能再一次给摩尔定律敲响了丧钟;晶体管密度曾经遵循摩尔定律而不断翻倍,我们才有了今天这种极其强大的计算机。雪上加霜的是,这是最后一份ITRS路线图。这项协调规划于1993年始于美国,然后扩展到了世界其他地区,现在走到了终点。

半导体行业协会(Semiconductor Industry Association)是一家位于华盛顿特区,代表IBM、英特尔及其他公司利益的美国贸易团体,也是ITRS的主要赞助商。该协会表示,在行业参与度下降、企业参与其他计划的兴趣增强的情况下,它将发挥自己的作用,与另一家行业组织——半导体研究公司(SemiconductorResearch Corp.)合作,为政府和行业资助项目确定应该优先做哪些研究。预计其他ITRS参与者将在新名称下开展新的路线图工作,作为IEEE“重启计算”(RebootingComputing)计划的一部分。

这些路线图变化看似是无关紧要的管理变动,但是,“在行业里,这是一场重大破坏,或者说是地震”,市场分析公司VLSI研究公司(位于加州圣何塞)的首席执行官丹•哈奇森(Dan Hutcheson)如是说。20世纪90年代初,也就是路线图工作刚开始的时候,美国半导体企业有理由开展合作,确定共同需求,最终于1998年促成了ITRS的建立。他说,供应商们很难知道半导体企业的确切需求,因此各芯片公司集体确定优先工作,充分利用有限的研发资金,这也就说得通了。

但要维持摩尔定律的领先优势,会面临重重困难,耗费大量资金,因此导致行业出现重大整合。据哈奇森计算,2001年有19家企业在研发和制造配备先进晶体管的逻辑芯片,而今天只剩格罗方德、英特尔、三星和台积电4家。(此前,IBM也曾属于这一方阵,但其芯片制造工厂被格罗方德收购了。)

哈奇森表示,这些公司有自己的路线图,而且可以与其设备和材料供应商直接沟通。此外,它们极具竞争力。“他们并不想坐在屋子里,谈谈自己需要什么。”他说,“有点像橄榄球赛季刚开始的时候,一切都很有趣,但进入季后赛,就变得很残酷了。”

ITRS主席保罗•佳基尼(Paolo Gargini)也同意“这个行业已经变了”,而且他还强调了其他变化。不再自己制造先进芯片的半导体公司现在依靠芯片代工厂来提供先进技术。而且,他还说,芯片买方和设计方(如苹果、谷歌和高通等公司)对未来的芯片提出了越来越多的要求。佳基尼说:“曾经是由半导体公司来决定半导体应具有的功能特征。但现在,这种情况一去不复返了。”最后一份ITRS报告被称为ITRS2.0,反映出计算上的提高不再是自下而上进行,不再追求更小的开关、更密集或更快的内存。这份报告更多地采取了自上而下的方法,专注于数据中心、物联网、移动设备等推动芯片设计的应用。

新的IEEE路线图——国际设备和系统路线图(IRDS)——也将采用这种方法,但还会加入计算机架构,实现“一个包括设备、组件、系统、架构和软件在内的,全面的、端到端的计算生态系统”。

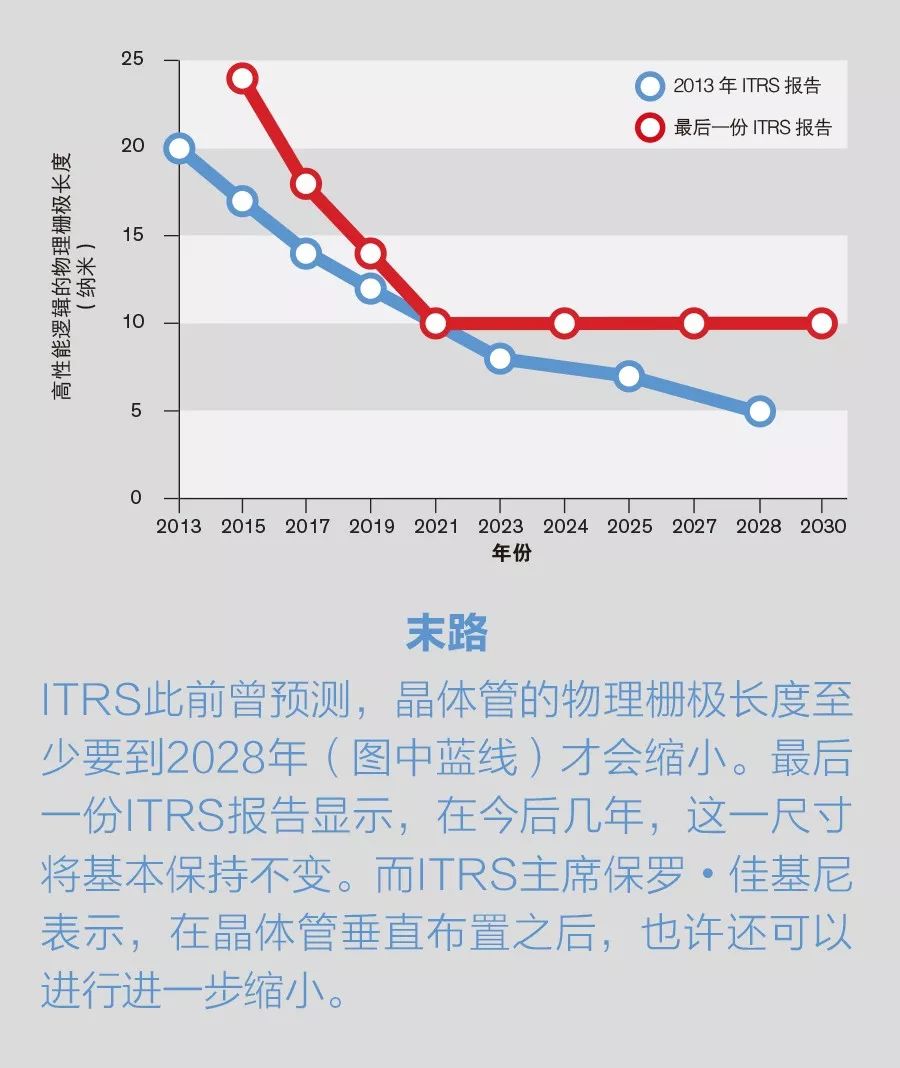

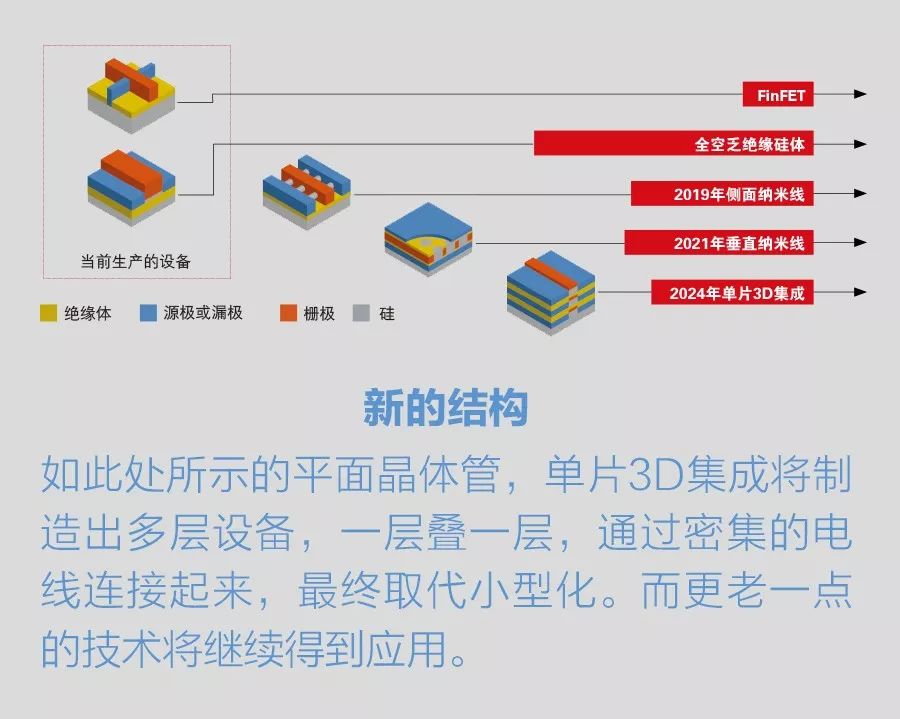

直到2014年发布2013年ITRS报告(也就是倒数第二份路线图)之时,晶体管小型化还属于长期预测内容。那份报告预测,晶体管的物理栅极长度(说明电流在设备中必须穿行多远的指标)和其他关键的逻辑芯片尺寸至少在2028年之前会继续缩小。然而自那之后,3D概念发展起来。存储行业也早已转向3D架构来缓解小型化压力,提高NAND闪存的容量。将元件一层叠一层并用许多电线连接的单片3D集成已成为越来越热门的讨论话题。

2015年报告包含了这些趋势,预测到21世纪20年代初,一直以来的缩小趋势——芯片尺寸的缩小——将结束。但佳基尼表示,认为摩尔定律即将消亡的想法“是完全错误的”。“媒体发明了多种定义摩尔定律的方法,但其实真正的定义只有一种:每两年,晶体管的数量都会翻倍。”

他强调,摩尔定律只是预测集成电路的某一区域能有多少个晶体管——无论是几十年来的单层布置还是多层堆叠。佳基尼说,如果一家公司真的想缩小晶体管尺寸,那么就能继续缩小到本世纪20年代,“但采用3D办法更为经济。这就是我们想传递的信息”。

其他变化也即将发生。今后几年里,在3D集成获得采用之前,ITRS预测,领先的芯片企业将不再使用现在高性能芯片上应用的晶体管结构:鳍式场效应晶体管(FinFET)。该设备有一个栅极围绕水平鳍形通道的3个方向,控制电流通过。根据最新路线图,芯片制造商们将放弃这种结构,转而选择一个栅极从侧面控制各个方向的元件。该元件也像FinFET那样有一个水平通道,但是栅极延伸到了通道下方,将通道环绕起来。之后,晶体管将变成垂直的,其通道像硅柱或纳米线一样竖立起来。该报告还预测,传统的硅通道将被其他材料制成的通道取代,如硅锗、锗,以及三族和五族元素构成的化合物。

有了这些变化,各公司将能在某一区域中配置更多的晶体管,从而遵守摩尔定律的内容。但遵守摩尔定律的精神——计算性能的稳步提高——就是另一回事了。

IEEE计算机学会主席兼IEEE重启计算计划的共同领导人汤姆•康特(Tom Conte)提出,有一段时间,人们并没有把晶体管密度的翻倍和计算性能的提高联系起来。

在很长一段时间里,晶体管体积的缩小就意味着速度的提升。但康特说,在20世纪90年代中期,为了把越来越多的晶体管用线连起来,需要更多的金属层,这严重耽误了时间,工程师们不得不重新设计芯片的微架构来提高性能。10年后,由于晶体管密度过大,其散发出的热量限制了时钟速度。各公司开始在芯片上加入更多核心以保持运转。

“我们一直生活在这个泡沫之中,计算机行业依靠设备方完成自己的工作,所以,计算机行业和设备行业之间有一堵非常美好的墙。”康特说,“2005年那堵墙开始真正坍塌,自那之后,我们有了越来越多的晶体管,但它们的性能真的没有提高很多。”

2015年,在IRDS启动之前,这堵坍塌的墙成为了IEEE重启计算计划开始与ITRS协作的强大动力。康特表示:“我想说我们能看到通道另一端的光,我们也知道那是一列迎面驶来的火车。”

重启计算计划之后召开的一次峰会,涵盖了所有具有未来计算潜力的技术,如新款晶体管和存储元件、神经形态计算、超导电路,以及使用近似答案而非准确答案的处理器。

康特说,IRDS将追寻“摩尔定律直到最后”。但路线图的焦点发生了变化。“并不是说这是摩尔定律的终结,”他说,“只是后退一步,谈谈此时真正重要的事情——而此时真正重要的就是计算。”

-

芯片

+关注

关注

456文章

50886浏览量

424185 -

半导体

+关注

关注

334文章

27432浏览量

219292 -

晶体管

+关注

关注

77文章

9698浏览量

138324

原文标题:到2021年,晶体管体积将停止缩小

文章出处:【微信号:IEEE_China,微信公众号:IEEE电气电子工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶体管与场效应管的区别 晶体管的封装类型及其特点

达林顿晶体管概述和作用

CMOS晶体管的尺寸规则

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

晶体管处于放大状态的条件是什么

芯片中的晶体管是怎么工作的

PNP晶体管符号和结构 晶体管测试仪电路图

苹果首款折叠屏MacBook或提前至2026年发布

晶体管的分类与作用

什么是达林顿晶体管?达林顿晶体管的基本电路

2016年发布ITRS做出预测,晶体管的尺寸可能将在5年后停止缩减

2016年发布ITRS做出预测,晶体管的尺寸可能将在5年后停止缩减

评论