本文首发于公众号 FPGA开源工坊

FIFO是FPGA/IC设计中经常使用到的模块,它经常被用在两个模块之间进行数据的缓存,以避免数据在传输过程中丢失。同时FIFO也经常被用在跨时钟域处理中。

FIFO深度的计算是FPGA和IC笔面试中经常被问到的一个问题,在这篇文章里面我们就来讨论一下FIFO的深度应该怎么计算。

FIFO的深度如果设置的小了就会有丢数的风险,设置的大了会有资源的浪费。

在讨论如何计算FIFO的深度之前,应该先明白一个概念,那就是突发传输 ,也就是burst。

突发传输

为什么要明确突发传输的概念呢?我们假设有以下几种开发场景。

场景一:读比写快

假如说一个FIFO在不间断的向里面写入数据和读出数据,并且向FIFO里面写数据的速度比从FIFO里面读数据的速度要慢,那么是不是这个FIFO永远都不会被写满了。

场景二:写比读快

假如说一个FIFO在不间断的向里面写入数据和读出数据,并且写入的速度比读出的速度快,那么是不是意味着这个FIFO的深度无论设置多少都终将会被写满。

所以不间断在对FIFO不间断的进行读写的情形中讨论FIFO深度是没有意义的。

而我们要讨论的FIFO深度其实是在突发传输中才是有意义的。

突发传输:就是说一个又一个的数据包,每一个数据包之间是有间隙的。

每一个数据包的长度叫做burst length 突发长度

FIFO的最小深度就与突发长度,读写速率有关系。

计算出来FIFO的深度关键就在于计算出来在读写突发的这段时间内,有多少数据没有被读走,这个数据的多少就是FIFO的最小深度。

计算公式

FIFO的深度可以用下面的公式计算出来

可以看到在上述公式里面的关键就是确定burst length。

下面就通过几个例子来说明burst length的计算。

例子

例一

某大厂的笔试题:

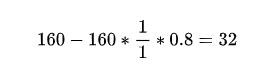

设计同步FIFO,每100个cycle可以写入80个数据,每10个cycle可以读出8个数据,FIFO的深度至少为:

A: 16

B: 32

C: 64

D: 72

首先从题目中知道同步FIFO,所以rd_clk和wr_clk是一样的。

第二每10个cycle中可以读出8个数据,那么rd_rate就是8/10也就是0.8

现在关键就是burst length的计算了。

每100个cycle可以写入80个数据,那么是不是意味着这80个数据可以在100个cycle的周期的任意时间写进FIFO里面。那么什么时候是连续写入数据最多的极端情况呢,这个极端情况就是burst length最大的时候。

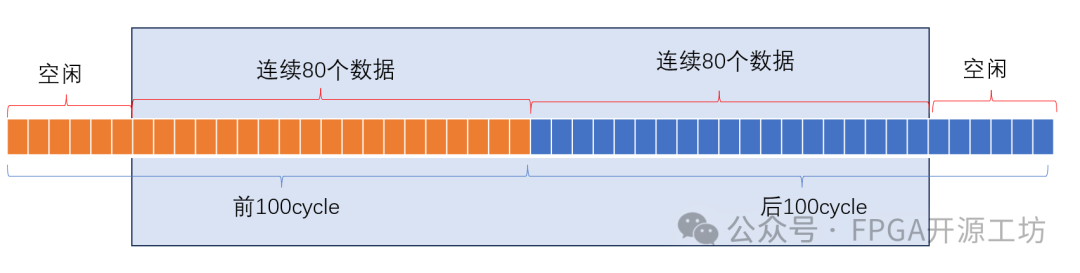

这个极端情况就是在连续的200个cycle中,是不是可以写入160个数据,那么这160个数据背靠背的连续写入就是极端情况了。

如下图所示:

在连续两百个周期内,前20个周期空闲,中间160个时钟向FIFO写入数据,最后20个时钟再次空闲。

所以burst length就是160

所以FIFO的最小深度为

例二

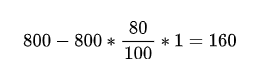

有一个FIFO设计,输入时钟100MHz,输出时钟80MHz,输入数据模式是固定的,其中1000个时钟中有800个时钟传输连续数据,另外200个空闲,请问为了避免FIFO下溢/上溢,最小深度是多少

A: 320

B: 80

C: 160

D: 200

根据题意wr_clk是100, rd_clk是800。

因为输入数据的模式是固定的,所以不用考虑背靠背的情况,所以burst length是800

题目中没有说明在输出的时候读使能是否会拉低,所以我们认为FIFO一直在输出,也就是rd_rate是1

所以FIFO的深度为:

-

FPGA

+关注

关注

1664文章

22545浏览量

640420 -

IC设计

+关注

关注

38文章

1406浏览量

108476 -

fifo

+关注

关注

3文章

407浏览量

45952 -

时钟域

+关注

关注

0文章

53浏览量

10073

原文标题:FPGA|IC笔面试--FIFO深度计算

文章出处:【微信号:FPGA开源工坊,微信公众号:FPGA开源工坊】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA学习-总结fifo设计中深度H的计算

求助,FPGA fifo深度不够怎么办?

FIFO深度怎么设计

如何计算异步FIFO深度和单独的时钟源

如何计算Async Fifo Depth

什么是fifo深度?

如何利用LabVIEW FPGA模块实现FIFO深度设定?

谈谈FIFO阈值的阈值设置及深度计算

【教程】“最恶劣”的FIFO深度计算

LabVIEW FPGA模块实现FIFO深度设定

你们知道FIFO最小深度计算吗

如何简单快速地计算FIFO的最小深度

FIFO的深度应该怎么计算

FIFO的深度应该怎么计算

评论