上海,2018年1月29日 – 三重富士通半导体股份有限公司(以下简称“三重富士通半导体”)与富士通研究所(注2)针对车载雷达及第5代移动通信系统等毫米波市场,共同研发出可实现高精度电路设计的55nm CMOS 制程设计套件(Process Design kit,简称PDK)。通过此PDK的运用,用户能够对包含放大器及变频电路等毫米波设计的大规模电路进行精确的设计。

【 背景 】

为实现低成本的第5代移动通讯系统及支持自动驾驶的车载雷达的相关技术,高性能低功耗具有毫米波(30-300GHz)功能的CMOS电路备受瞩目。但是因为毫米波信号波长较短,高精度的电子元件模型不易实现,所以需要多次的试制来达到要求的性能。因此造成了研发周期长、试制成本高等问题。

【 简介 】

针对三重富士通半导体的55nm的低功耗工艺“C55LP(Low Power)”及三重富士通半导体独自研发的超低功耗工艺“C55DDC(Deeply Depleted Channel)”,推出了适用于毫米波设计的PDK。与富士通研究所共同开发的此款PDK中,包括最适合使用于毫米波带宽的晶体管及传输电路的电子元件参数及电路构造,因此可以大幅提高100GHz以下带宽的大规模收发器电路的设计精确度。

主要特征

ž经过硅验证的110 GHz范围内的毫米波用SPICE MODEL

1.提供已最优化的电子元件及Pcell

- 毫米波晶体管

- 传输电路

- 倒装焊工艺垫(Bumping pad)设计的相关条件

3.对应技术:C55LP,C55DDC

4.对应频率:28GHz,80GHz

【 示例及效果 】

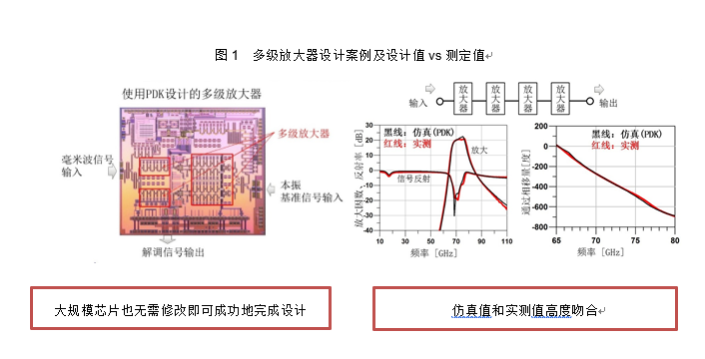

以下的示例是一个将毫米波带域信号高增益放大的“多级放大器”,以及将两个复用信号进行高精度分离/解调的“正交解调器”构成的接收电路。特别是在多级放大器级数增加的时候,设计值及测定值会有很大的差异。但通过三重富士通半导体所推出的PDK,在初期就能够得到接近实体电路的设计结果(图1)。

使用此款PDK,不仅是放大器,包括宽带正交解调器及变频器、电压控制震荡器在内的毫米波电路的设计精度也得以提高,进可实现在短期内完成大规模毫米波收发电路的研发。

【 将来计划 】

三重富士通半导体正在准备推出包含封装模组特性在内的PDK,以帮助客户提高毫米波产品的性能及缩短研发时间。并计划自2018年起,逐步推出包含模拟电路宏模型及评测毫米波元件等周边服务。

【 注释 】

(注1)三重富士通半导体股份有限公司:

总部神奈川县横滨市、总经理河野通有

(注2)富士通研究所:

总部 神奈川县川崎市、总经理 佐佐木繁

关于富士通电子元器件(上海)有限公司

富士通电子元器件(上海)有限公司是富士通在中国的半导体业务总部,于2003年8月成立,在北京、深圳、大连等地均设有分公司,负责统筹富士通在中国半导体的销售业务。

富士通电子元器件(上海)有限公司的主要销售产品包括 Custom SoCs(ASICs),代工服务,专用标准产品(ASSPs),铁电随机存储器,继电器,GaN(氮化镓),MCU和电源功率器件等,它们是以独立产品及配套解决方案的形式提供给客户,并广泛应用于高性能光通信网络设备、手持移动终端、影像设备、汽车、工业控制、家电、穿戴式设备、医疗电子、电力电表、安防等领域。

-

CMOS

+关注

关注

58文章

5712浏览量

235454 -

毫米波

+关注

关注

21文章

1923浏览量

64794

发布评论请先 登录

相关推荐

软通动力中标杭州银行股份有限公司司库项目

宁波嘉乐智能科技股份有限公司选购我司热分析仪

基本半导体完成股份改制,正式更名

三明科飞产气新材料股份有限公司购我司HS-TGA-101热重分析仪

毫米波雷达代表企业,获国家级产业基金投资!

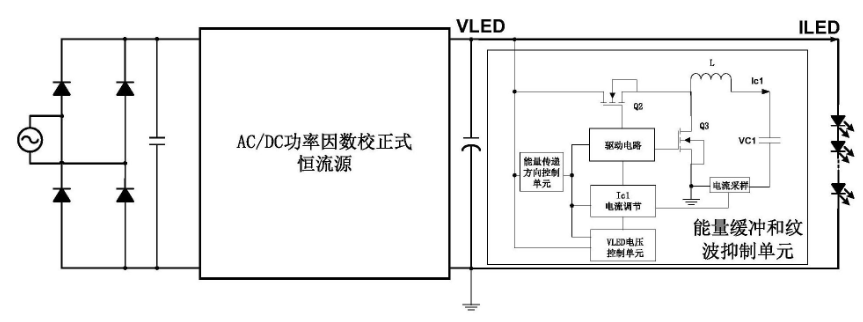

深圳必易微电子股份有限公司获低频纹波抑制电路及控制方法专利

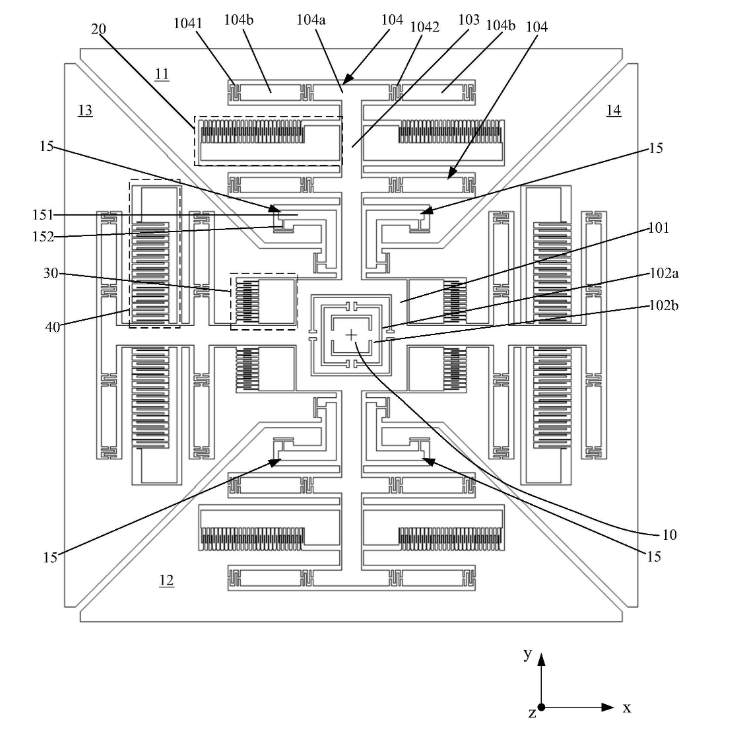

上海矽睿科技股份有限公司取得陀螺仪结构专利

奥士康被中兴通讯股份有限公司授予2023年度“倾心协同奖”

智能电动机保护器在合盛硅业股份有限公司的应用

中微半导体设备(上海)股份有限公司声明

成都芯进电子股份有限公司创立大会暨第一次股东大会成功召开

三重富士通半导体股份有限公司推出55nm CMOS毫米波制程设计套件

三重富士通半导体股份有限公司推出55nm CMOS毫米波制程设计套件

评论