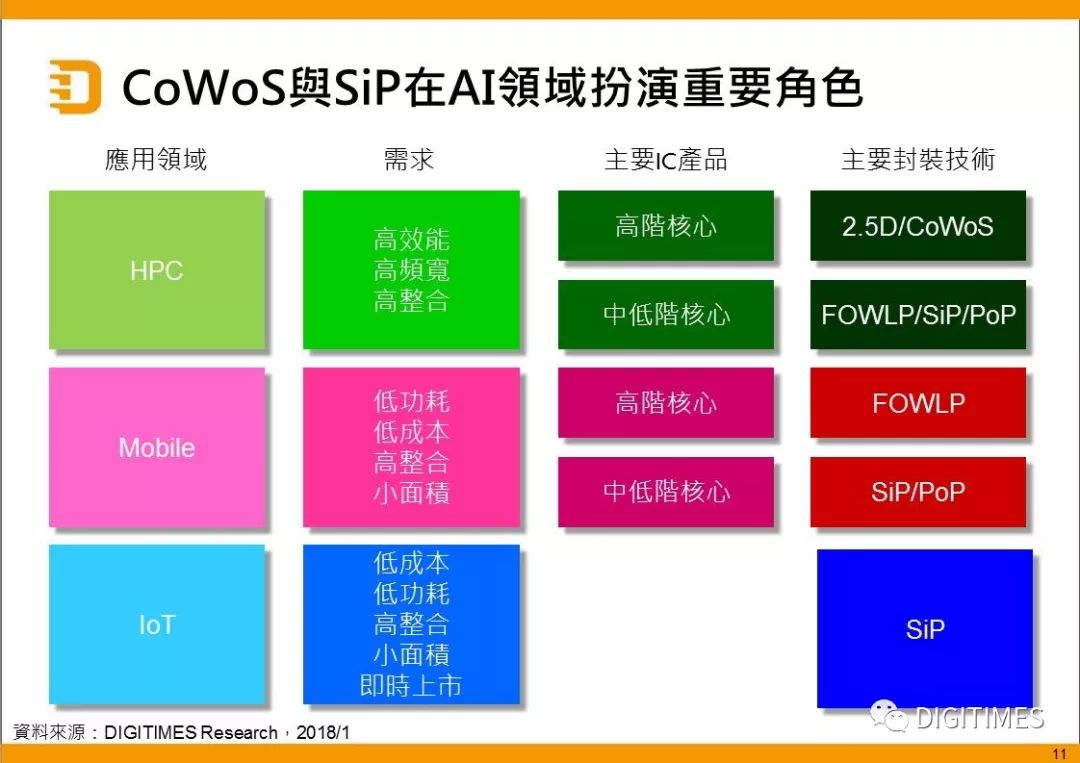

由硬件端来看人工智能架构,涵盖上游云端(cloud)运算、中游边缘运算(edge computing),及下游的装置端(device)。综合人工智能硬件上中下游所需关键芯片进一步分析,对IC制造产业而言,DIGITIMES Research认为,高效能运算(High Performance Computing;HPC)平台将成为制程技术研发的重中之重。

芯片效能的提升,除可透过微缩技术升级与晶体管结构改变等前段技术达成外,后段先进封测技术的导入,亦可以有效提升IC产品效能。其中,台积电推出2.5D CoWoS(Chip on Wafer on Substrate)制程技术就是导入矽中介层(interposer)材质,并采用矽穿孔(Through Si Via;TSV)技术,透过大幅提高I/O数的方法提升IC效能,台积电更于2017年上半年推出采CoWoS技术7纳米制程HPC平台。

除讲求效能提升的HPC平台外,IoT平台在人工智能的发展上,也扮演重要角色,物联网平台IC产品以低功耗、低成本、实时上市为主要产品诉求,因此,该平台IC产品以系统级封装(System in Package;SiP)为主要封装技术。

随人工智能市场兴起,IC制造业者整合前后段技术已成产业重要趋势外,DIGITIMES Research认为,为客户提供一站式服务,IC制造业者甚至要结合EDA、IP、IC设计服务等业者,建立完整生态系统(ecosystem),才有机会在AIoT领域取得致胜先机。(更完整分析请见DIGITIMES Research AI+,IC制造服务「因应高效能与实时上市要求CoWoS与SiP将成人工智能重要封装技术」研究报告)

-

SiP

+关注

关注

5文章

501浏览量

105312 -

AI

+关注

关注

87文章

30725浏览量

268870 -

CoWoS

+关注

关注

0文章

137浏览量

10485

原文标题:【DIGITIMES Research】CoWoS与SiP成AI芯片重要封装技术

文章出处:【微信号:gh_44592200c847,微信公众号:gh_44592200c847】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CoWoS先进封装技术介绍

微源半导体LPQ65131芯片在汽车领域的应用

工控主板在工业控制中扮演什么角色

工业电脑在智能制造控制领域的应用趋势分析

Python在AI中的应用实例

RISC-V发展迅猛,中国扮演重要角色

爱普生差分晶振在光模块中的重要角色

光电耦合器:航天航空领域的先进连接技术

推拉力测试机在各种工业应用中,扮演着至关重要的角色

新型电力系统的重要角色:超级电容混合储能系统

CoWos与SiP在AI领域扮演重要角色

CoWos与SiP在AI领域扮演重要角色

评论