一、引言

随着半导体技术的不断发展,先进封装作为后摩尔时代全球集成电路的重要发展趋势,正日益受到广泛关注。受益于AI、服务器、数据中心、汽车电子等下游强劲需求,半导体封装朝着多功能、小型化、便携式的方向发展,先进封装市场有望加速渗透。据Yole的数据,全球先进封装市场规模预计将从2023年的378亿美元增长至2029年的695亿美元,复合年增长率达到10.7%。

二、封装技术迭代

(一).从传统封装到先进封装的跨越

随着集成电路工艺制程越发先进,对技术端和成本端均提出巨大挑战,封装行业实现了从传统封装到先进封装的转变。传统封装主要功能为芯片提供机械保护、散热途径以及确保机械和电气连接稳定性等。先进封装则采用先进设计思路和集成工艺,对芯片进行封装级重构,能有效提升系统高功能密度。它可在不单纯依靠芯片制程工艺突破的情况下,通过晶圆级封装和系统级封装,提高产品集成度和功能多样化,满足终端应用对芯片轻薄、低功耗、高性能的需求,同时大幅降低芯片成本,在高端逻辑芯片、存储器、射频芯片、图像处理芯片、触控芯片等领域广泛应用。

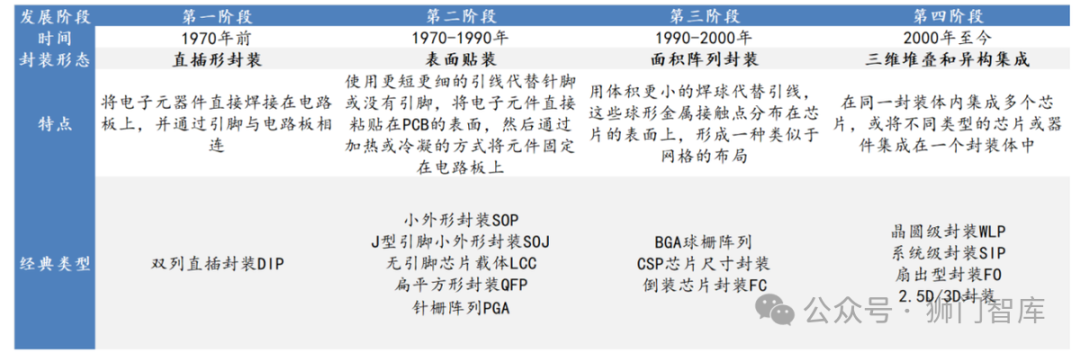

(二).先进封装发展趋势与技术迭代

随着芯片在算速与算力上需求同步提升,高速信号传输、优化散热性能、实现更小型化封装、降低成本、提高可靠性以及实现芯片堆叠等成为封装领域新追求。从制造工艺端来看,为持续提升集成度,先进封装从最初的倒装封装(FC),逐步向晶圆级封装(WLP)、2.5D/3D封装等迭代。

资料来源:《先进封装推动半导体产业新发展》,《先进封装技术的发展与机遇》,华安证券研究

三、先进封装技术

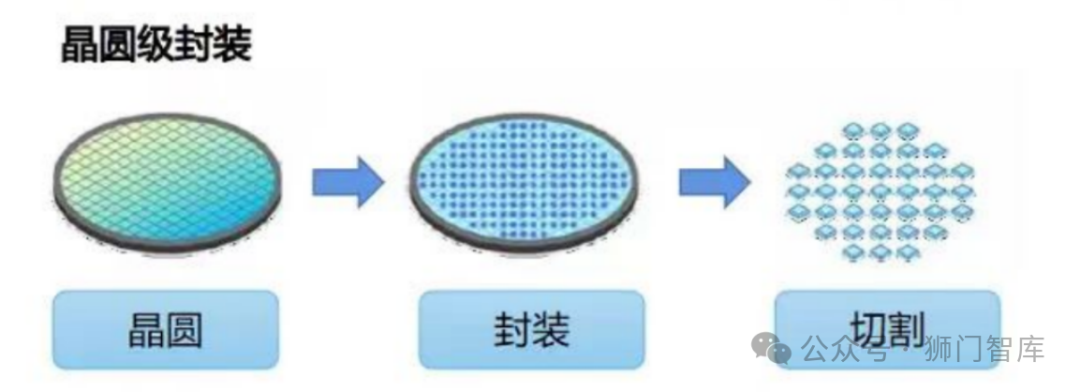

传统封装首先将晶圆切割成芯片,然后对芯片进行封装;而晶圆级封装则是先在晶圆上进行部分或全部封装,之后再将其切割成单件。

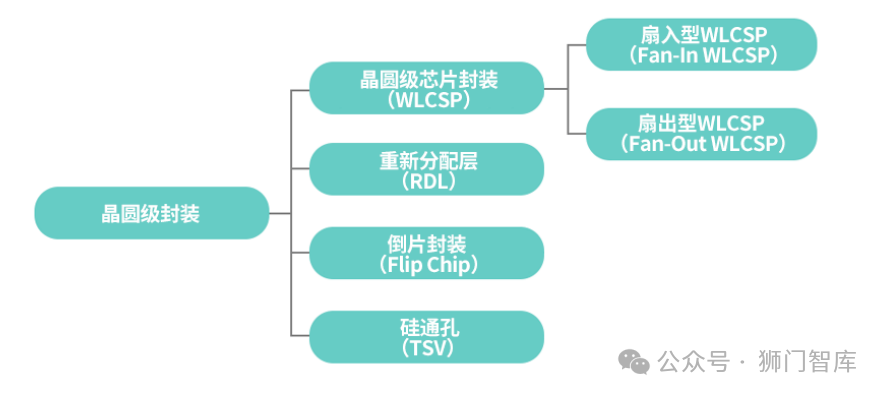

晶圆级封装方法能够进一步细分为以下四种不同类型:其一,晶圆级芯片封装(WLCSP),能够直接在晶圆的顶部形成导线和锡球(Solder Balls),且无需基板。其二,重新分配层(RDL),运用晶圆级工艺对芯片上的焊盘位置进行重新排列,焊盘与外部通过电气连接的方式相连接。其三,倒片(Flip Chip)封装,在晶圆上形成焊接凸点,以此来完成封装工艺。其四,硅通孔(TSV)封装,借助硅通孔技术,在堆叠芯片的内部实现内部连接。

(一).晶圆级封装(WLP)

晶圆级封装(Wafer Level Packaging, WLP)是一种前沿的半导体封装技术。与传统封装方法不同,WLP在晶圆制造阶段即对芯片进行封装,而非切割成单个单元后进行。这一创新方式使得晶圆上的芯片能够先进行测试和封装,随后再切割成独立个体,从而大幅度提升了生产效率和封装密度。

晶圆级封装(资料来源:屹立芯创)

WLP技术带来了诸多优势。首先,在尺寸和重量方面,由于封装过程在晶圆级别进行,无需为封装体预留额外空间,因此可以显著减小封装尺寸和减轻重量。其次,成本效率也是WLP的一大亮点,整个晶圆能够同时进行封装,这种批量处理方式有效降低了生产成本。此外,WLP还能实现更高的I/O密度和更优的电气性能,因为I/O引脚可以直接分布在芯片周围。同时,由于封装材料直接与芯片接触,有助于热量的传导,从而提升了散热性能。最后,由于减少了焊接接头的数量,WLP还显著提高了产品的可靠性。

然而,WLP技术也存在一些劣势。首先,设计复杂性增加,因为WLP要求在晶圆级别进行设计和制造,这可能会提高设计的复杂性和成本。其次,一旦芯片被封装,如果发现缺陷,修复或更换单个芯片将变得异常困难。最后,WLP需要高精度的制造工艺,对设备和技术的要求较高,这可能限制了部分小规模制造商的采用。

先进的晶圆级封装分类

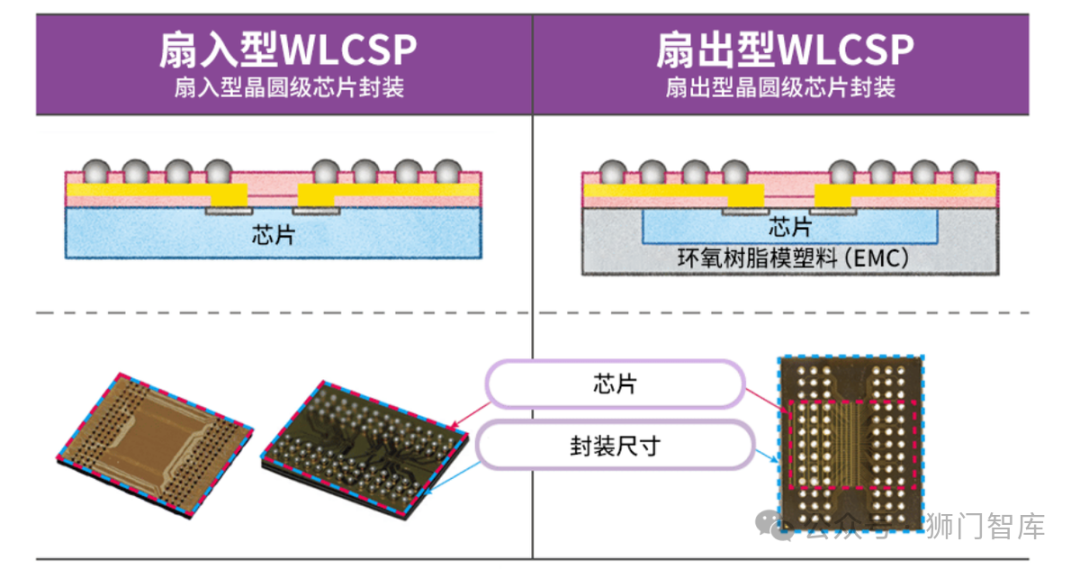

晶圆级芯片封装(WLCSP)可分为两大类型:扇入型WLCSP(Fan-In WaferLevel Chip ScalePackage, Fan-In WLCSP)和扇出型 WLCSP(Fan-Out Wafer Level Chip ScalePackage, Fan-Out WLCSP)。

1.扇入型 (Fan-In) WLCSP (Wafer Level Chip Scale Package)

晶圆级芯片封装大多制造过程在晶圆上完成,是晶圆级封装典型代表。广义上,晶圆级封装还包括在晶圆上完成部分工艺的封装,如采用重新分配层、倒片技术和硅通孔技术的封装。扇入型和扇出型 WLCSP 中的 “扇” 指芯片尺寸。扇入型 WLCSP 的封装布线、绝缘层和锡球在晶圆顶部。扇入型 WLCSP 与传统封装相比有优缺点。

扇出型封装(FO)技术

优点:封装尺寸与芯片尺寸相同,可缩至最小;锡球直接固定在芯片上,无需基板等媒介,电气传输路径短,电气特性好;无需基板和导线等封装材料,工艺成本低,在裸片数量多、生产效率高时可进一步节约成本。

缺点:采用硅芯片作封装外壳,物理和化学防护性能弱,与 PCB 基板热膨胀系数差异大,导致锡球承受应力大,焊点可靠性弱;存储器半导体推出同一容量芯片尺寸变化时,无法用现有基础设施进行封装测试;封装锡球陈列尺寸大于芯片尺寸或晶圆上芯片数量少、生产良率低时,封装成本高于传统封装。

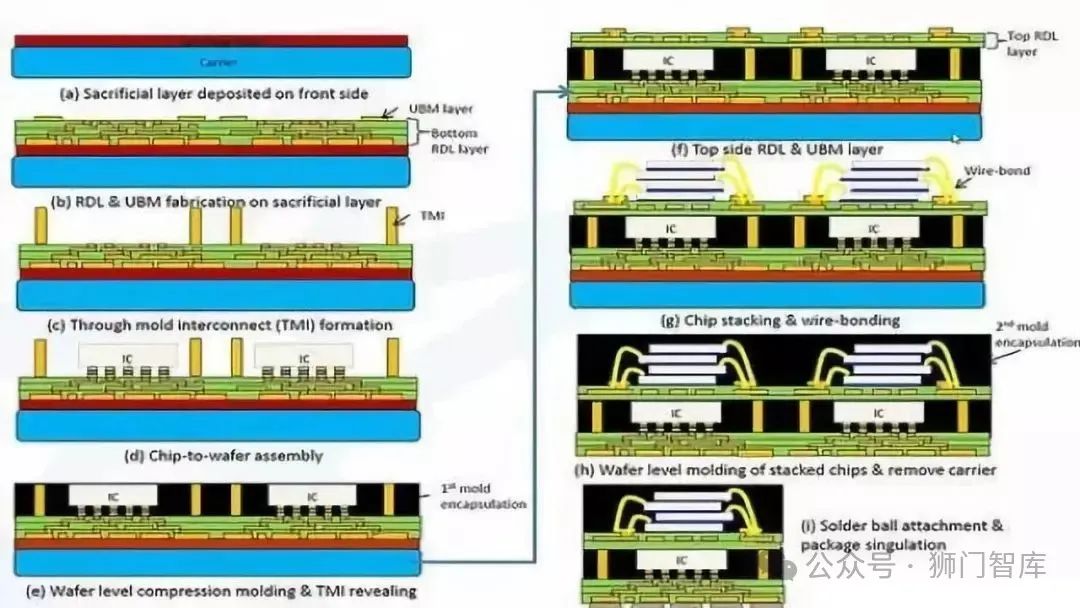

2.扇出型 (Fan-Out) WLCSP

扇出型WLCSP继承了扇入型的优点并改进了其缺陷。

扇入型封装和扇出型封装(资料来源:SK海力士)

扇入型WLCSP的锡球均位于芯片表面,而扇出型则可延伸至芯片外。扇入型需在封装后才切割晶圆,故芯片与封装尺寸需一致,锡球也必须在芯片范围内。扇出型则先切割再封装,芯片排列在载体上重塑为晶圆,其间填充环氧树脂模塑料。之后取出晶圆进行级处理并切割成单元。

扇出型不仅保持扇入型的电气特性,还解决了其问题,如无法使用现有封装测试设施、锡球阵列过大无法封装及封装不良导致的成本增加等。因此,扇出型WLCSP近年来应用日益广泛。

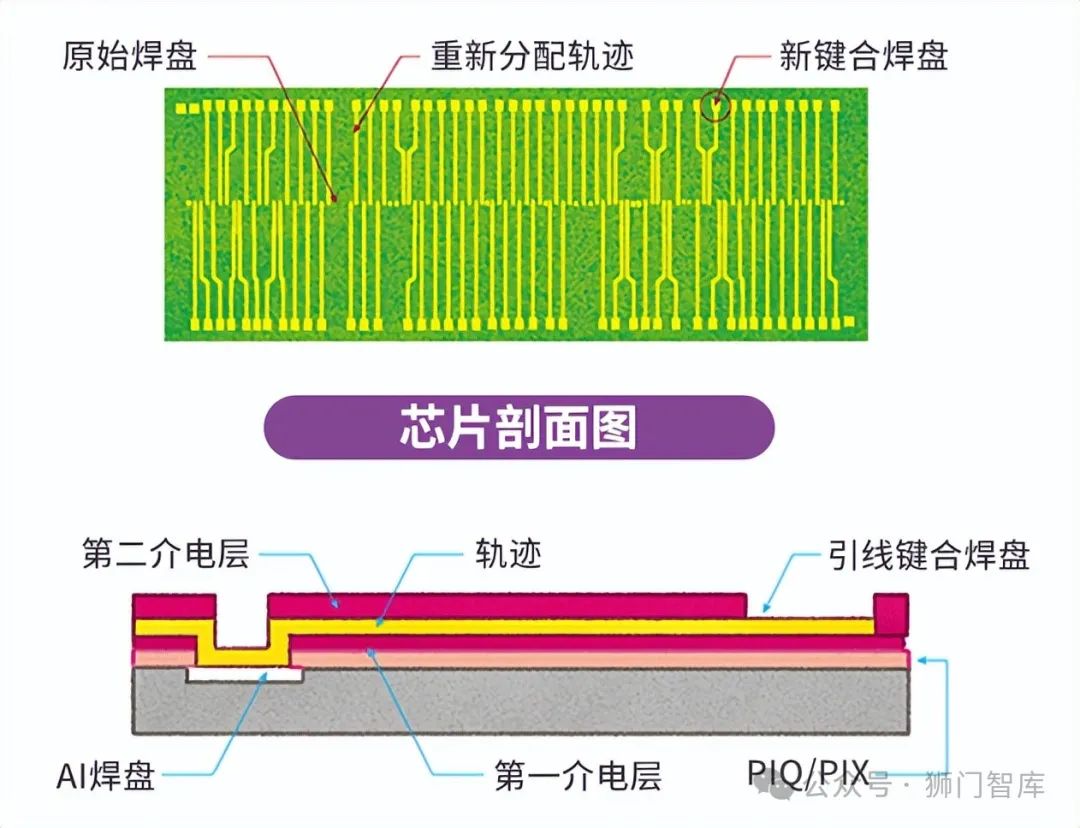

(二).重新分配层 (ReDistribution Layer, RDL)

RDL技术是对晶圆上已有键合焊盘进行重新布线的工艺,通过增加金属层来改变焊盘布局。这是一种晶圆级工艺,专为焊盘重排设计,处理后仍需传统封装。

客户若想独特排列晶圆焊盘,采用RDL技术比更改晶圆制造更高效。此外,RDL也适用于中心焊盘芯片的堆叠。

采用RDL技术的芯片与剖面图

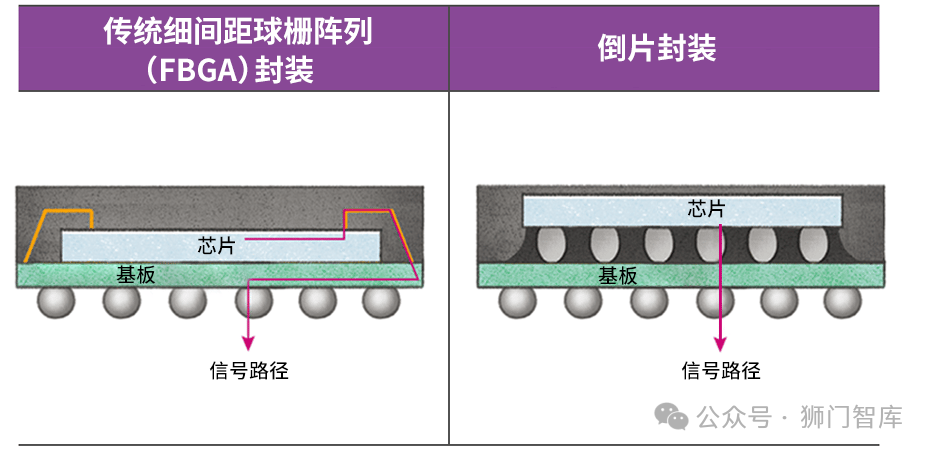

(三).倒片封装 (Flip Chip)

倒片封装技术通过将芯片上的凸点翻转并安装于基板等封装体上,实现芯片与板的电气连接。此技术已很大程度上取代传统引线键合,原因有二:

引线键合对输入/输出(I/O)引脚数量和位置有限制,而倒片封装无此限制。

倒片封装的电信号传输路径更短。

在引线键合中,金属焊盘一维排列于芯片表面,无法位于边缘或中心。而倒片封装中,焊盘可二维排列于芯片一侧,数量大幅增加。此外,凸点焊盘可布置于芯片顶部任意位置,供电焊盘也可靠近需供电区域,提升电气性能。

引线键合与倒片键合的信号传输路径对比

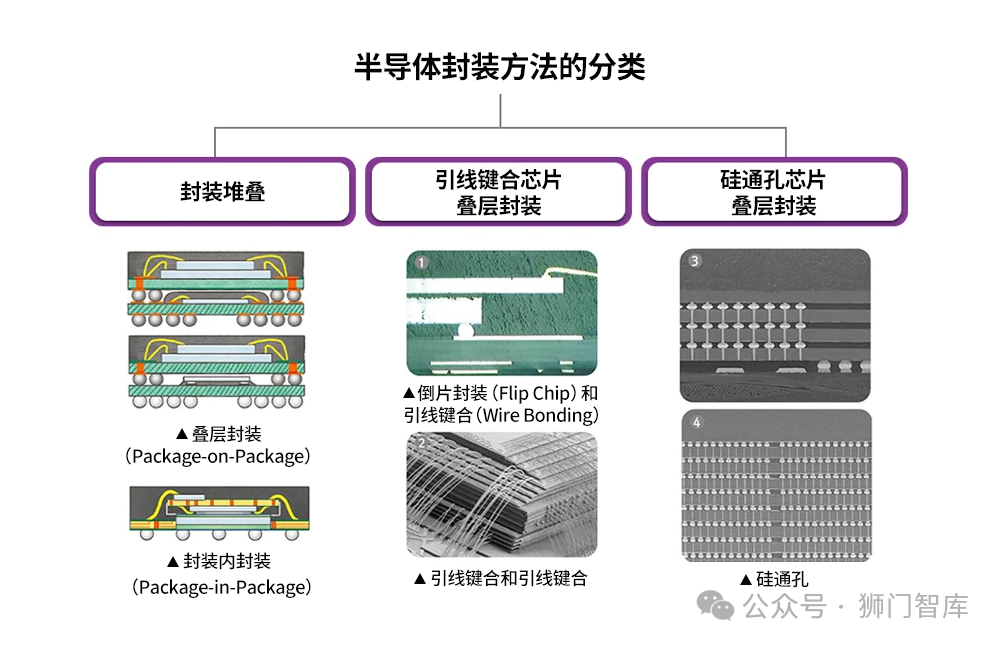

(四).堆叠封装 (Stacked Packages)

堆叠封装技术能减小产品体积,提升性能,是产品开发的重要方法。过去,一个封装体内通常只封装一个芯片,但现在可开发多芯片封装或大容量存储器封装,甚至整合多个系统组件于单个封装体内。这些技术助力半导体公司打造高附加值产品,满足市场需求。

堆叠封装技术主要分为三类:

封装堆叠:通过垂直堆叠封装体形成。

芯片叠层封装(引线键合):使用引线键合技术将不同芯片堆叠在单个封装体内。

芯片叠层封装(TSV):使用硅通孔技术替代引线键合实现内部电气互连。

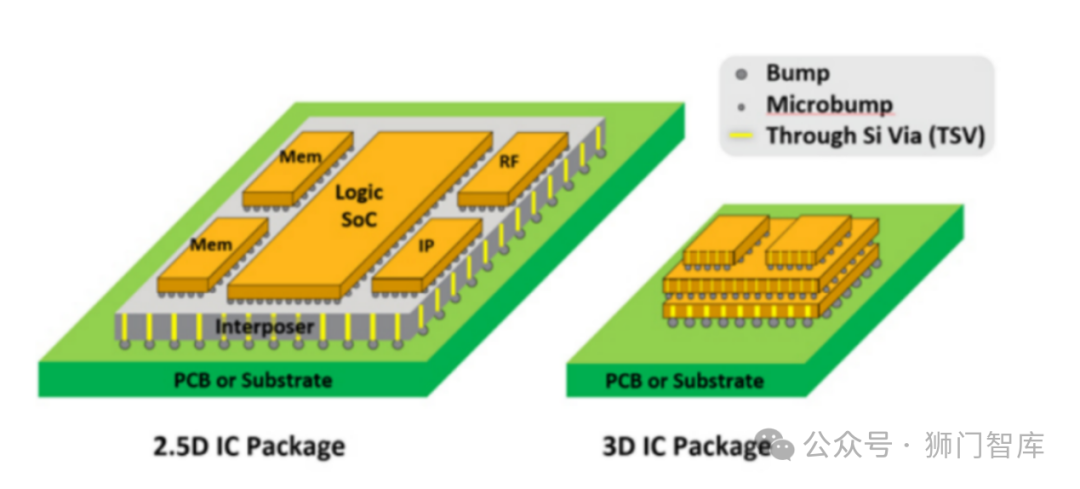

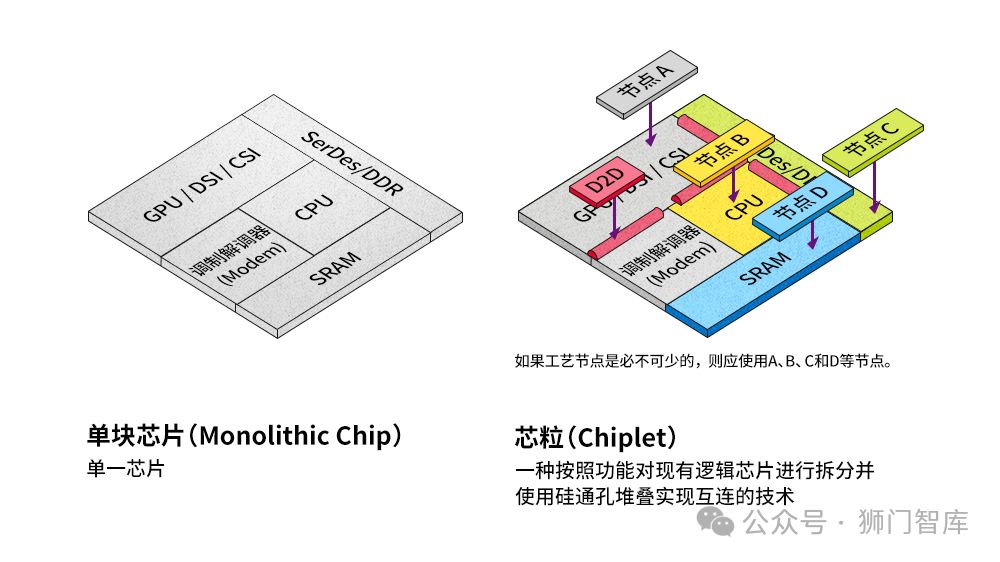

2.5D/3D封装与堆叠封装紧密相连,均为半导体封装的关键技术,旨在提升芯片集成度、性能和体积效率。

堆叠封装通过垂直堆叠多个封装体或芯片来减小体积、提升性能,可采用不同技术实现。2.5D封装利用中介层和TSV等技术连接多个芯片,降低成本、提高产量。3D封装则在芯片内部制作TSV,实现更高集成度,但技术难度和成本较高。

三者均追求高集成度、性能和体积效率,堆叠封装包含2.5D和3D封装。它们在不同领域有广泛应用,如高性能计算、网络通信等,且随着技术进步,将更广泛地应用于电子产品,推动半导体产业发展。

资料来演:芯观点

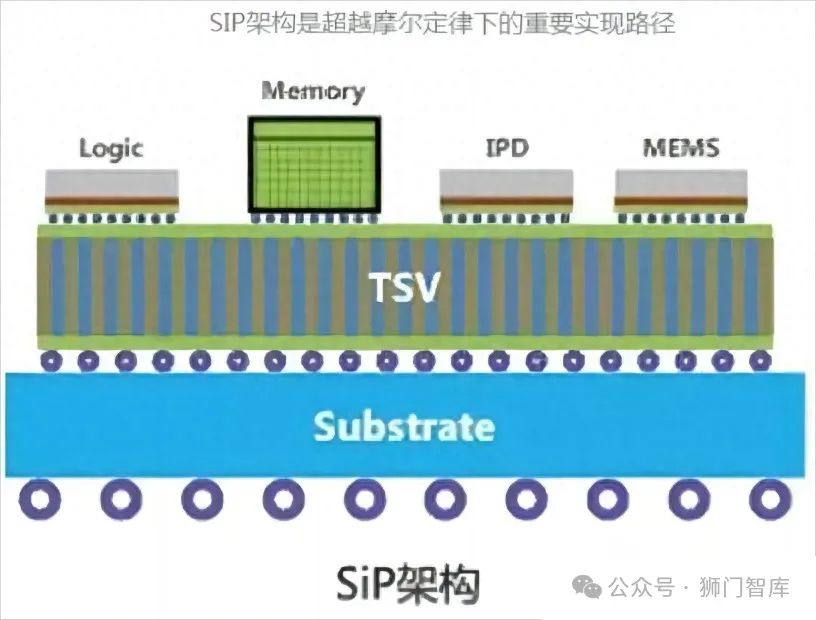

(五).系统级封装(SiP)

系统级封装(System in Package, SiP)是一种先进的封装技术,它通过将多个功能各异的集成电路(ICs),比如处理器、存储器、传感器等,集成在一个单一的封装内,来构建一个完整的系统解决方案。这种集成不仅限于硬件组件,还可以包括软件部分以及无源元件,如电阻器和电容器,从而实现高度的系统整合。

SiP技术的优势在于其高集成度,能够将多个芯片和元件集成在单一封装内,显著减少最终产品所需的空间。此外,由于元件之间的距离缩短,SiP能够提升电子设备的性能,减少信号传输的延迟。SiP还提供了设计灵活性,允许设计师在系统级别上进行创新,更容易实现定制化设计。从成本角度来看,SiP通过集成多个元件减少了组装成本和材料使用,从而降低了整体成本。同时,由于减少了外部连接和接口,SiP提高了系统的可靠性和耐用性。

芯粒概念图

然而,SiP技术也面临一些挑战。其设计和开发过程比传统封装更为复杂,需要跨学科的专业知识。此外,SiP封装的维修难度较高,一旦封装出现故障,可能需要更换整个模块,增加了维修成本。随着集成度的提高,散热成为SiP设计中的一个重要考虑因素。尽管长期来看SiP可以降低成本,但初期的制造成本可能较高,特别是对于产量不大的产品。这些挑战需要通过创新的设计和制造技术来克服,以实现SiP技术的全面优势。

四、先进封装市场格局

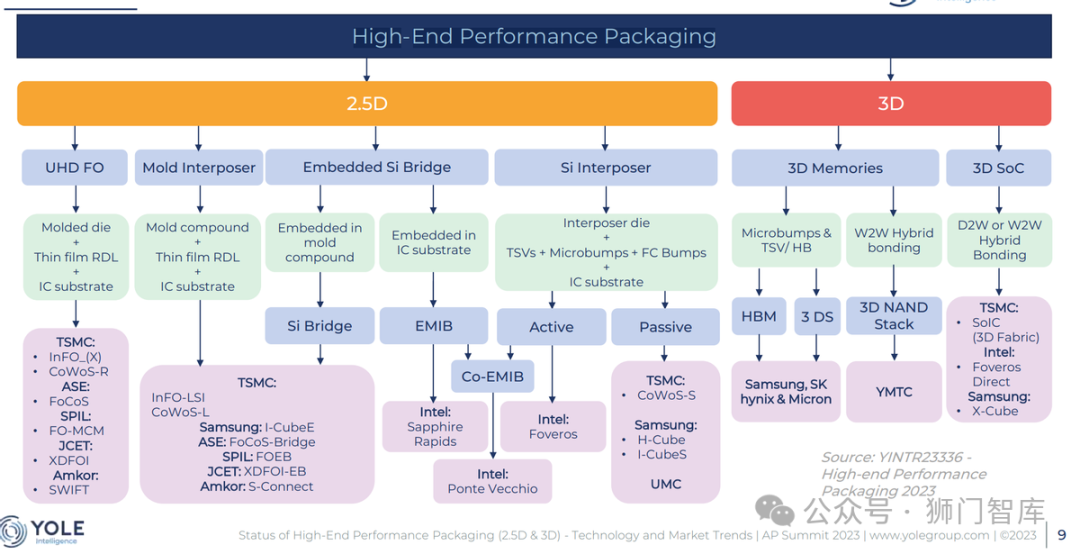

全球先进封装参与者众多,其解决方案涵盖(超)高密度扇出(有机中介层)、3D片芯堆叠、2.5D硅中介层、2.5D嵌入式硅桥、3D堆叠存储器等几大类。龙头代工厂及其解决方案包括台积电(InFO,集成扇出)、日月光(FOCoS,芯片后装的基板上扇出芯片)、三星(2.5D RDL(再分布层))、Amkor Technology(S - SWIFT,高密度扇出线)等。

典型工艺布局如下:

2.5D:CoWoS(台积电)、EMIB(英特尔)、I - Cube(三星)、XDFOI(长电科技)等;

3D:SoIC(台积电)、Foveros(英特尔)、X - Cube(三星)、3D - eSinC(华天科技)等。

所有高端性能封装平台(Yole对2.5D和3D的分类)

五、未来发展趋势

在当前AI等新兴领域带动下,移动和消费类、电信和基础设施以及汽车等终端市场需求强劲增长,先进封装市场快速增长,产业链各细分环节都有望迎来国产替代广阔机遇。未来,先进封装可能会朝着更高集成度、更小尺寸、更高性能以及智能化等方向发展。例如,可能会出现将更多种类芯片集成在一个封装体内的技术,进一步缩小封装尺寸,采用更先进材料和工艺提高性能,以及实现封装体的智能化监测和控制等。

六、结语

先进封装作为半导体产业的关键环节,在满足终端应用需求、推动半导体行业发展方面具有重要作用。随着市场需求的增长和技术的不断进步,全球先进封装市场规模将持续扩大,国内企业在市场格局中也有一定的发展机会,同时关键设备的国产化替代也在逐步推进。未来,先进封装技术将不断创新和发展,为半导体产业带来更多的可能性。

-

半导体

+关注

关注

334文章

27442浏览量

219429 -

晶圆

+关注

关注

52文章

4922浏览量

128064 -

封装技术

+关注

关注

12文章

549浏览量

67994 -

先进封装

+关注

关注

2文章

413浏览量

253

原文标题:半导体产业链重要环节,浅谈先进封装

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

怎样衡量一个芯片封装技术是否先进?

简述芯片封装技术

SiP与Chiplet成先进封装技术发展热点

12种当今最主流的先进封装技术

先进封装技术的发展与机遇

什么是先进封装?先进封装技术包括哪些技术

先进封装技术的类型简述

先进封装技术的类型简述

评论