以下文章来源于逍遥设计自动化 ,作者逍遥科技

引言

半导体行业不断发展,不断推动芯片设计和制造的边界。随着逐渐接近传统平面缩放的极限,先进封装技术正成为持续提升性能的关键推动力。在这些技术中,3.5D封装作为当前2.5D解决方案和完全3D集成之间的折中方案,正在获得广泛关注。本文将探讨3.5D封装的概念、优势、挑战以及对半导体设计未来的潜在影响。

什么是3.5D封装?

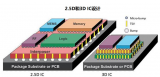

3.5D封装是一种结合了2.5D和3D集成技术元素的混合方法。在3.5D配置中,逻辑chiplet垂直堆叠,然后与其他组件一起键合到共享基板上。这种方法在广泛采用的2.5D技术和更复杂的完全3D-IC之间提供了一个中间地带,而业界已经努力将后者商业化近十年。

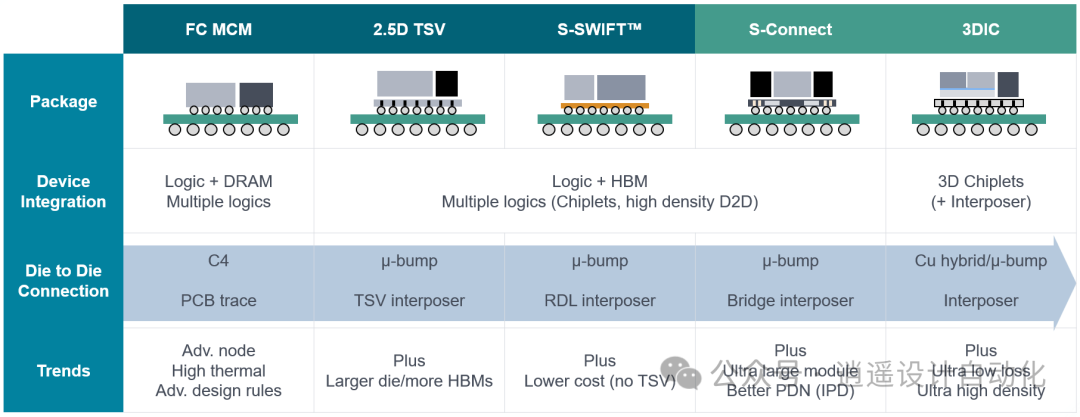

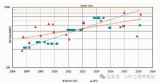

图1:三星的异构集成路线图,展示了封装技术的演变。(来源:三星代工厂)

3.5D封装的主要优势

热管理 :通过在组件之间创建物理分隔,3.5D封装有效解决了困扰更密集3D配置的热耗散和噪声问题。

增加SRAM集成 :由于SRAM缩放落后于数字晶体管缩放,3.5D允许通过垂直堆叠chiplet将更多SRAM添加到高速设计中。这对于维持处理器缓存性能非常重要。

改善信号传输 :减薄处理元件和内存之间的接口缩短了信号需要传输的距离,与平面实现相比显著提高了处理速度。

灵活性和可扩展性 :3.5D组件提供了更大的灵活性来添加额外的处理器核心,并通过允许已知良好的裸片单独制造和测试来实现更高的良率。

异构集成 :这种方法使用不同制程节点制造的芯片可以组合在一起,优化性能和成本。

实施策略

最常见的3.5D配置涉及将处理器堆叠在SRAM上。这种安排简化了冷却,因为高利用率处理元件产生的热量可以通过散热器或液体冷却来移除。减薄的基板允许信号传输更短的距离,减少了处理器和内存之间数据移动的功耗。

有趣的是,SRAM不一定需要与先进处理器处于相同的制程节点。这种灵活性有助于提高良率和可靠性。例如,三星提出了一个路线图,显示在不久的将来,2nm chiplet堆叠在4nm chiplet上,并计划到2027年实现1.4nm chiplet堆叠在2nm chiplet上。

英特尔的3.5D技术方法涉及在带有硅桥的基板上实现。这种方法以成本效益高的方式使用薄硅片来实现芯片间互连,包括堆叠芯片间互连。这种方法提供了硅密度和信号完整性性能的优势,而无需使用大型、昂贵的单片互连层。

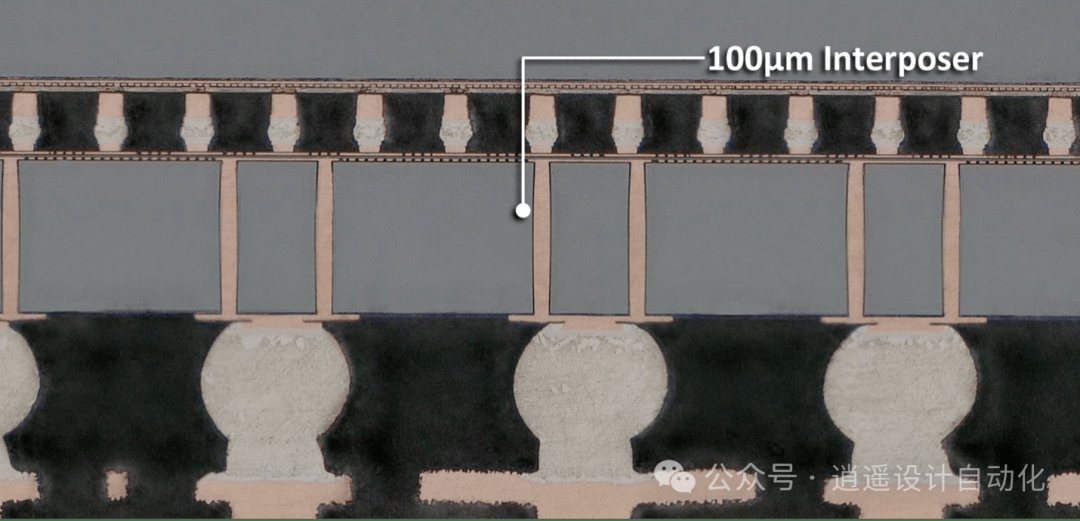

图3:当前互连层技术支持高I/O数量和精细间距。(来源:日月光集团)

挑战和持续发展

3.5D封装提供了众多优势,但也面临着挑战。一些关键的持续发展领域包括:

热管理 :尽管相比完全3D设计有所改善,但在3.5D组件中管理热量仍然是一个重大挑战。业界正在探索各种冷却解决方案,包括浸没式冷却、局部液体冷却和蒸汽室。

互连技术 :随着我们推动更高的密度,业界正在向更精细的凸点间距解决方案和混合键合技术发展。目标是实现25到20微米的凸点间距,混合键合可能实现小于10微米的间距。

共面性 :在数千个微凸点上实现所需的平整度水平对传统键合方法是一个重大挑战。这正推动人们对混合键合等替代方法产生兴趣。

时序收敛 :随着在3.5D配置中添加更多元素,确保信号在正确的时间到达正确的位置变得越来越复杂。这需要复杂的热感知和IR感知时序分析。

数据管理 :设计和分析这些复杂系统所涉及的数据量正在爆炸性增长。有效处理这些数据并减少模拟和分析运行时间是一个主要关注领域。

组装复杂性 :物理组装这些器件涉及管理具有不同厚度和热膨胀系数的各种裸片的热、电和机械连接。这需要进行密集的热机械认证工作。

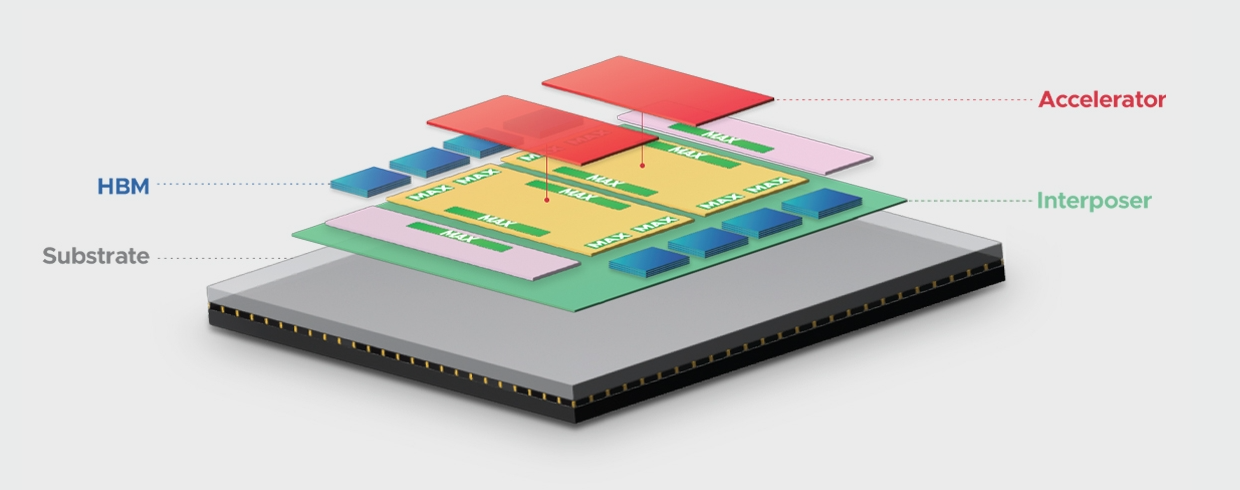

图4:先进封装路线图,说明互连技术的演变。(来源:安靠科技)

商业化的道路

3.5D封装的最终目标是实现芯片设计的"即插即用"方法,设计者可以从菜单中选择chiplet,并迅速将连接到经过验证的架构中。虽然这一愿景可能需要数年时间才能完全实现,但可能在未来几年内看到商用chiplet出现在先进设计中,从高带宽内存与定制处理器堆叠开始。

实现这一愿景需要在几个关键领域取得进展:

EDA工具 :电子设计自动化(EDA)工具需要发展以处理3.5D设计的复杂性。这包括同时考虑热、信号完整性和功率完整性问题,以及改善IC设计师和封装专家之间的协作。

工艺/组装设计套件 :3.5D工艺和组装的标准化设计套件非常重要。这些可能会在代工厂和外包半导体组装和测试(OSAT)提供商之间分配。

标准化 :为可以预先构建和预先测试的内容设置现实的参数将是提高组装速度和便利性的关键。像UCIe(通用chiplet互连快车)这样的行业标准就是朝这个方向迈出的步伐。

工艺一致性 :确保3.5D组装各个步骤的工艺一致性非常重要。这需要为每个工艺步骤定义可接受的输出,并开发实时优化配方的方法,以保持结果在所需范围内。

结论

3.5D封装代表了半导体集成的重要进步,在3D-IC的性能优势和当前2.5D解决方案的实用性之间提供了平衡。随着业界趋向于这种方法,可以期待在设计工具、制造工艺和标准化努力方面的快速发展。

在热管理和互连技术等领域仍然存在挑战,但3.5D封装的潜在优势正在推动大量投资和创新。随着这些技术的成熟,有望在从高性能计算到人工智能等广泛应用中实现新的性能和功能水平。

实现完全的3.5D封装及其他更高集成的旅程将需要整个半导体生态系统的持续合作。从EDA供应商到代工厂、OSAT和系统集成商,每个参与者在将这项技术推向市场方面都发挥着重要作用。随着我们向前发展,3.5D封装可能成为连接当前技术与未来完全3D-IC的桥梁,开启半导体创新的新时代。

-

芯片

+关注

关注

463文章

54463浏览量

469587 -

半导体

+关注

关注

339文章

31279浏览量

266702 -

封装

+关注

关注

128文章

9339浏览量

149062 -

晶体管

+关注

关注

78文章

10443浏览量

148685

原文标题:3.5D封装:2.5D和完全3D集成之间找到的平衡点

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一颗芯片面积顶4颗H200,博通推出3.5D XDSiP封装平台

先进封装成破局,博通率先落地3.5D,6000mm²超大集成

继vivo NEX 3后,OPPO又曝“瀑布屏”手机

Chiplet&互联要闻分享 「奇说芯语 Kiwi talks」

MEMS传感器在汽车应用增长快速,NEMS、3.5D封装技术成趋势

深入剖析2.5D封装技术优势及应用

3.5D封装来了(下)

3.5D封装来了(上)

先进封装技术:3.5D封装、AMD、AI训练降本

3.5D Chiplet技术典型案例解读

从 2D 到 3.5D 封装演进中焊材的应用与发展

什么是3.5D封装?它有哪些优势?

什么是3.5D封装?它有哪些优势?

评论