AMBA AXI4(高级可扩展接口 4)是 ARM 推出的第四代 AMBA 接口规范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 凭借半导体产业首个符合 AXI4 标准的即插即用型 IP 进一步扩展了 AMD 平台设计方法。 对于依靠 IP 来推动 UltraScale、7 系統、Zynq 7000、Virtex 6 和 Spartan 6 型设计上市进程的客户而言,AXI4 即插即用型 IP 提供了统一的标准接口,能显著简化 IP 集成。AMD 提供了一系列丰富的基于 AXI4 的 IP,为嵌入式、DSP 以及逻辑领域提供了统一的开放式标准接口。

更高的生产率

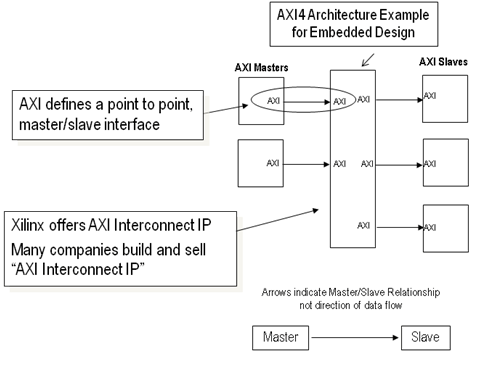

通过将多种不同的接口整合到一个接口(AXI4)中,用户仅需了解单个系列的接口即可。

简化了不同领域 IP 的集成,并使自身或第三方合作伙伴 IP 的开发工作更简单易行。

由于 AXI4 IP 已为实现最高性能、最大吞吐量以及最低时延进行了优化,从而使设计工作进一步获得简化。

更大的灵活性

支持嵌入式、DSP 及逻辑版本用户。

调节互连机制,满足系统要求:性能、面积及功耗。

帮助您在目标市场中构建最具号召力的产品。

广泛的 IP 可用性

AMD 同 ARM 密切合作,共同为基于 FPGA 的高性能系统和设计定义了 AXI4 规范。作为我们推广 AXI4 工作的一部分,AMD 已采用 AXI4 作为 UltraScale、7 系統、Zynq 7000、Spartan 6、Virtex 6 以及未来产品系列发展的新一代 IP 互连标准。

AXI4 目标设计平台帮助客户加速嵌入式处理、DSP和连接功能设计开发。

AXI4 参考指南可指导用户向 AXI4 标准过渡。

行业生态系统(Ecosystem)支持

第三方 IP 和 EDA 厂商普遍采用开放式 AXI4 标准,从而使该接口获得了更广泛的应用。

Cadence Design Systems, Inc. 、CAST, Inc.、Denali Software、Mentor Graphics Corp.、Northwest Logic、OMIINO ltd.、Sarance Technologies, Inc.、Synopsys, Inc. 以及 Xylon d.o.o. 纷纷宣布支持可满足 AXI4 接口标准的 IP 及工具。

这能够确保构建基于 AXI4 的系统设计能够获得强大的行业生态系统支持,从而实现终极生产率,并加速产品上市进程。

AXI4 接口的主要优势

随着 IP 通用用户接口普遍采用 AXI4 标准,AMD 用户将从中受益。AXI4 具有:

一致性:所有接口子集都使用相同的传输协议。

全面规范化:便于客户采用。

标准化:配套提供标准模型和检查器以供设计人员使用。

接口去耦化:互连电路与接口之间有去耦机制。

可扩展性:AXI4 是一种可满足未来需求的开放式标准。

其它优势:

支持存储器映射型和串流型接口。

为通信、视频、嵌入式以及 DSP 功能提供统一化 IP 接口。

简便易用,并具有自动流水线例程化等特性,可帮助用户轻松实现既定性能目标。

诸如 fMAX、LUT 使用、时延以及带宽等关键属性相当于或优于当前的解决方案。

使 AMD 能在所有应用领域高效提供增强型本地存储器、外部存储器接口以及存储器控制器解决方案。

AXI 详情AXI4

AXI4 协议是 AXI3 的升级,旨在提高多个主系统使用时的互连性能和互连利用率。其包括了如下增强功能:

支持高达 256 个突发长度

服务质量信令

支持多个区域接口

AXI4-Lite

AXI4-Lite 是 AXI4 协议的子集,旨在与组件中较小较简单的控制寄存器型接口实现通信。AXI4-Lite 接口主要特性为:

所有处理的突发长度为 1

所有数据存取的大小等同于数据总线宽度

不支持独占访问

AXI4-Stream

AXI4-Stream 协议旨在实现从主系统向从系统进行单向数据传输,从而显著减少信号传输。该协议的主要优势包括:

使用相同的共享线集支持单数据流和多数据流

在同一互连中支持多数据宽度

FPGA 实现的理想选择

-

FPGA

+关注

关注

1629文章

21743浏览量

603555 -

嵌入式

+关注

关注

5083文章

19129浏览量

305428 -

接口协议

+关注

关注

5文章

41浏览量

18544 -

AMBA

+关注

关注

0文章

68浏览量

14995 -

AXI4

+关注

关注

0文章

20浏览量

8898

原文标题:AMBA AXI4 接口协议

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

看看在SpinalHDL中AXI4总线互联IP的设计

学习架构-AMBA AXI简介

SoC Designer AXI4协议包的用户指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流协议断言用户指南

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍

AMBA AXI4接口协议概述

AMBA AXI4接口协议概述

评论