一、接收弹性缓冲器

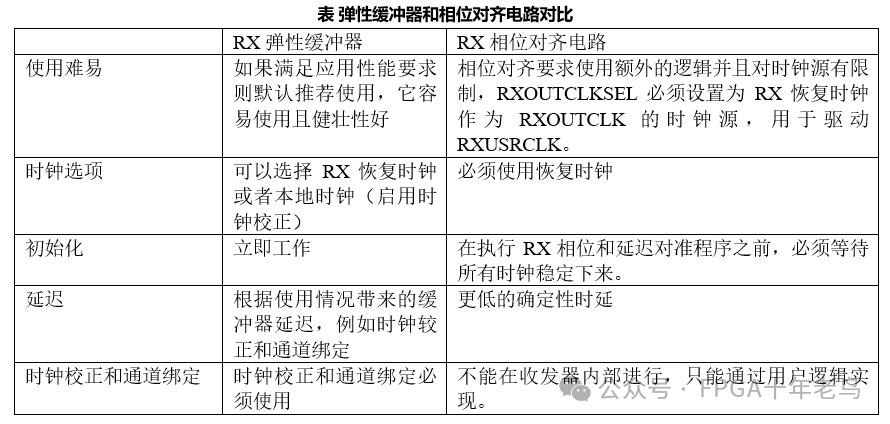

接收弹性缓冲器主要是为了解决XCLK和RXUSRCLK两个时钟域的差异,注意这里的差异包括频率差和相位差。如果使用RX的恢复时钟来作为RXUSERCLK的时钟源的话,此时不存在频率的差异,只存在相位的差异,则可以通过相位对齐电路来解决相位差异的问题。下表是使用弹性缓冲器和相位对齐电路的对比

弹性缓冲器除了消除相位差异的作用外,还承载着时钟校正和通道绑定这两个接收端特有的功能。读者可以留意下发送通道的缓冲器称为Phase Adjust FIFO,而接收通道的缓冲器称为Elastic Buffer,这个弹性(Elastic)就体现在实现这两个功能上。

二、时钟校正功能

当XCLK的时钟源是来自恢复时钟,而RXUSRCLK是来自本地时钟时,这两个时钟不同源,即使RXUSRCLK和XCLK以相同标称时钟频率运行,也总是存在很小的频率差,该差值可以被累加以导致RX弹性缓冲器最终上溢或下溢,除非对其进行校正。为了允许校正,每个GTX/GTH收发器TX周期性地发送一个或多个特殊字符,GTX/GTH收发器RX被允许根据需要在RX弹性缓冲器中移除或复制这些字符。当RX弹性缓冲区太满时删除字符以防止上溢,在RX弹性缓冲器太空时复制字符以防止下溢。

在高速收发器基础知识(4)中,笔者介绍了一下时钟校正实现的功能,读者可以回顾一下,其中主要需要关注的有两点:时钟校正序列设置以及弹性缓冲器的上下门限值,即缓冲器内字节超过什么门限则会移除字符,低于多少门限则会复制字符。

(一)时钟校正序列设置

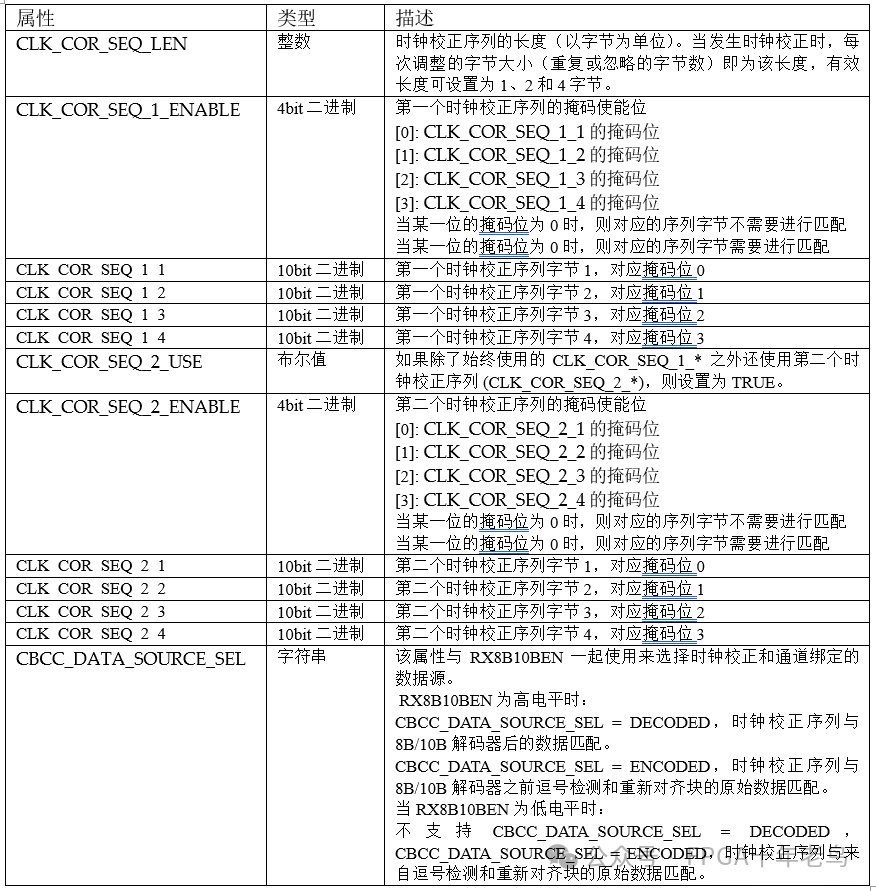

首先需要设置相关属性,如下表所示。

时钟校正序列使用 CLK_COR_SEQ_1_* 属性和 CLK_COR_SEQ_LEN 进行编程。每个CLK_COR_SEQ_1_*属性对应时钟校正序列1中的一个子序列。CLK_COR_SEQ_LEN用于设置要匹配的子序列的数量。如果使用 40 位或 20 位内部数据路径,时钟校正电路将匹配每个子序列的所有 10 位。如果使用 16 位或 32 位内部数据路径,则仅使用每个子序列的最右边的八位。

通过将 CLK_COR_SEQ_2_USE 设置为 TRUE 可以激活第二个备用时钟校正序列。第一和第二序列共享长度设置,但使用不同的子序列值进行匹配。设置 CLK_COR_SEQ_2_* 属性以定义第二序列的子序列值。

当使用 8B/10B 解码时(RX8B10BEN 为高电平),CBCC_DATA_SOURCE_SEL 设置为 DECODED,以搜索 8B/10B 解码器的输出以查找序列匹配而不是未解码的数据。这使得电路能够查找具有正或负差异的 8 位值,并将 K 字符与常规字符区分开来;当 CBCC_DATA_SOURCE_SEL 设置为 ENCODED 时,序列必须与传入的原始数据完全匹配。

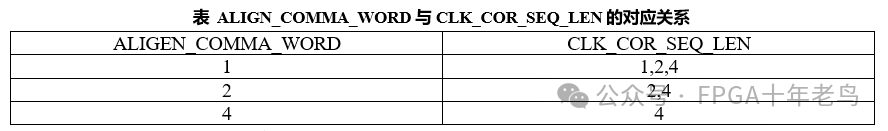

要通过弹性缓冲区保持逗点对齐,根据ALIGN_COMMA_WORD的值对CLK_COR_SEQ_LEN的设置有所限定,如下表所示。

(二)设置弹性缓冲器的门限

首先需要设置下面三个相关属性,如下表所示。

RX弹性缓冲区限制使用CLK_COR_MIN_LAT(最小延迟)和CLK_COR_MAX_LAT(最大延迟)设置。当 RX 弹性缓冲区中的字节数降至 CLK_COR_MIN_LAT 以下时,时钟校正电路会从其匹配的第一个时钟校正序列中写入额外的CLK_COR_SEQ_LEN 字节,以防止缓冲区下溢。类似地,当 RX 弹性缓冲区中的字节数超过CLK_COR_MAX_LAT 时,时钟校正电路从其匹配的第一个时钟校正序列中删除CLK_COR_SEQ_LEN字节,从该序列的第一个字节开始。7 系列 FPGA 收发器向导根据应用要求选择 CLK_COR_MIN_LAT 和 CLK_COR_MAX_LAT的最佳设置。

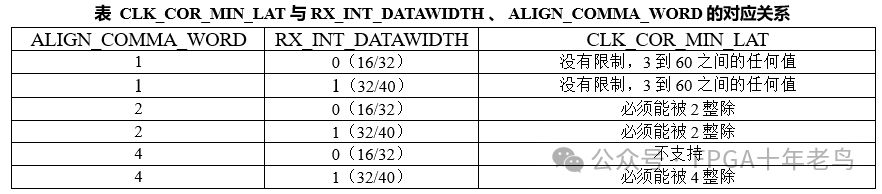

由于 CLK_COR_MIN_LAT 用于设置初始 RX 弹性缓冲区延迟,因此它必须能被 ALIGN_COMMA_WORD 设置整除,以通过弹性缓冲区保留逗号对齐。CLK_COR_MIN_LAT 的值必须符合 RX_INT_DATAWIDTH 和 ALIGN_COMMA_WORD的对应关系,如下表所示。

上限值CLK_COR_MAX_LAT 设置对建立的 RX 弹性缓冲区延迟没有影响,因此可以设置为 3 到 60 之间的任意值。

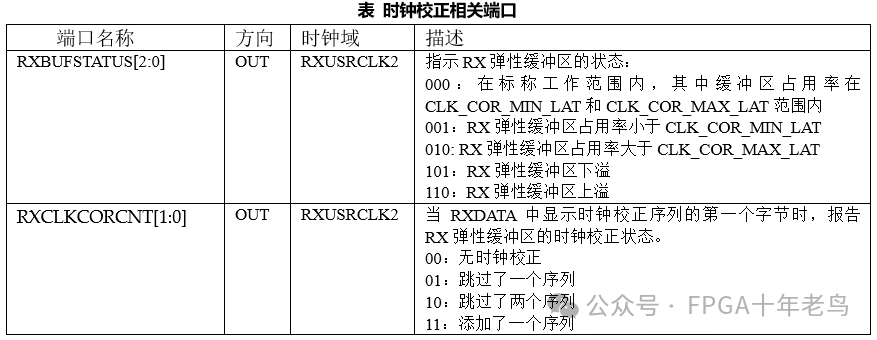

时钟校正功能不需要端口控制,只要通过属性设置好启用该功能,则会自动进行,可以通过RXCLKCORCNT和RXBUFSTATUS端口来观察时钟校正发生的情况,以及弹性缓冲器的空满状态,来判断是否出现异常。两个端口的介绍如下表所示。

-

FPGA

+关注

关注

1624文章

21580浏览量

600793 -

解码器

+关注

关注

9文章

1129浏览量

40600 -

收发器

+关注

关注

10文章

3357浏览量

105750 -

缓冲器

+关注

关注

6文章

1909浏览量

45408 -

时钟

+关注

关注

10文章

1706浏览量

131223

原文标题:Xilinx 7系列FPGA收发器——12、弹性缓冲器、时钟校正等

文章出处:【微信号:FPGA十年老鸟,微信公众号:FPGA十年老鸟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx FPGA收发器参考时钟设计要求

关于FPGA如何连接CAN收发器?

7系列收发器与时钟的关系是什么?

如何生成带有相应ref时钟输入的5GHz收发器?

使用一个收发器的Txoutclk为两个收发器配备Txusrclock吗?

介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题

FPGA高速收发器设计原则

Altera发售业界性能最好、具有背板功能的收发器Stratix V FPGA

Xilinx推出UltraScale FPGA收发器设计

如何在spartan-6 FPGA中使用GTP收发器的详细资料说明

GTX/GTH收发器时钟架构应用介绍

Xilinx FPGA收发器参考时钟设计要求与软件配置及结果测试

Xilinx 7系列FPGA收发器架构之硬件设计指导(一)

FPGA收发器的时钟校正功能

FPGA收发器的时钟校正功能

评论