一、通道绑定功能

XAUI 和 PCI Express 等协议结合了多个串行收发器连接来创建单个更高吞吐量的通道。每个串行收发器连接称为一个通道(lane)。除非每个串行连接的长度完全相同,否则通道之间的偏差可能会导致数据同时传输但到达时间不同。通道绑定通过使用 RX 弹性缓冲区作为可变延迟块来消除 GTX/GTH 收发器通道之间的偏差。用于绑定通道的 GTX/GTH 发射机都同时发送通道绑定字符(或字符序列)。接收到序列后,GTX/GTH 接收器可以确定每个通道之间的偏斜,并调整 RX 弹性缓冲区的延迟,以便在RX 用户接口处无偏斜地呈现数据。

在高速收发器基础知识(4)中已经介绍了通道绑定的功能,读者可以回顾一下,这里主要介绍GTX/GTH收发器内置的通道绑定功能如何设置与使用。

(一)通道绑定序列设置

通道绑定仅支持8B10B编码的数据,不支持64B/66B、64B/67B、128B/130B、加扰数据等。

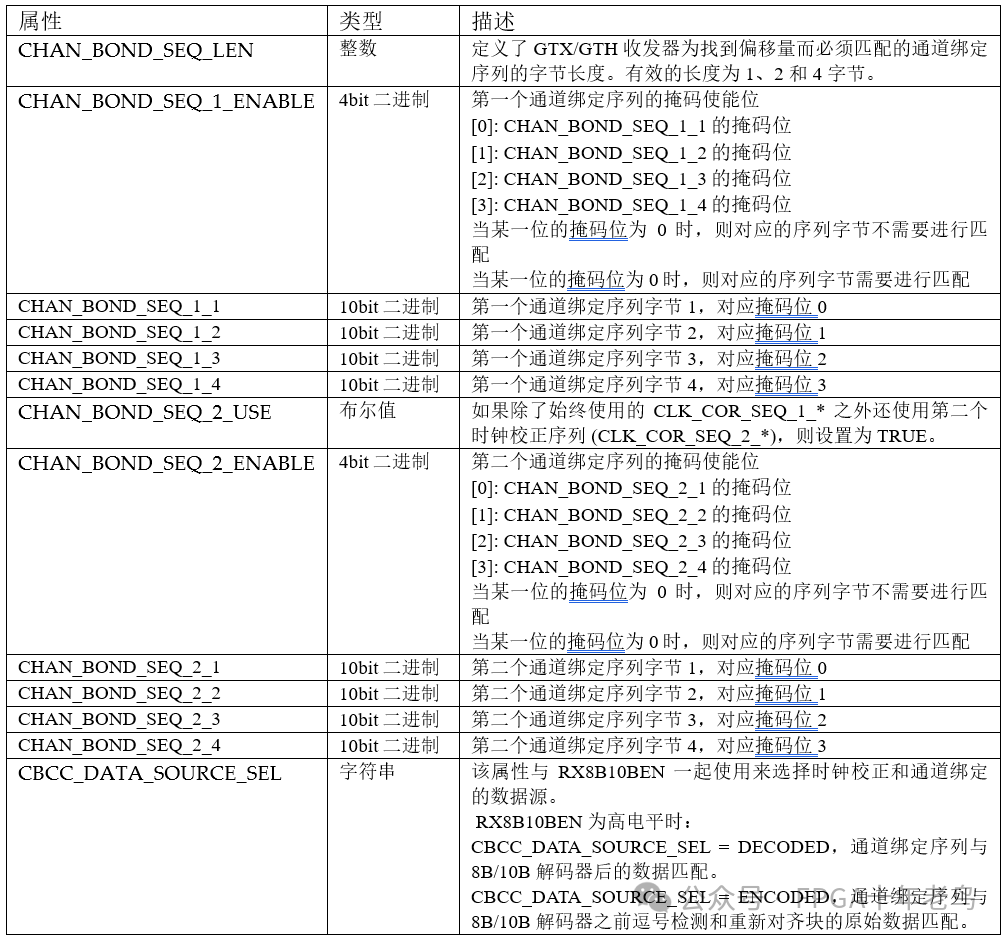

首先需要设置相关属性,如下表所示。

对比通道绑定的相关属性表格和时钟校正的相关属性表格,可以看出通道绑定序列设置方式基本是和时钟校正序列的设置是相同的。

(二)通道绑定最大偏移的设置

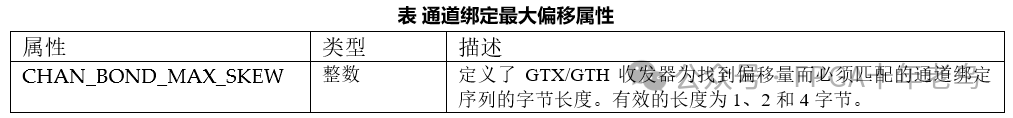

通道绑定最大偏移的属性如下表所示。

当主设备接收到通道绑定序列时,它不会立即触发通道绑定。如果从设备存在延迟,还会有多个字节到达。这个等待时间实际上就变成了接收端(RX)弹性缓冲器能够处理的最大偏移量,即CHAN_BOND_MAX_SKEW。如果实际的偏移量大于CHAN_BOND_MAX_SKEW,那么当主设备触发通道绑定时,从设备可能无法接收到该序列。

(三)通道绑定的使用

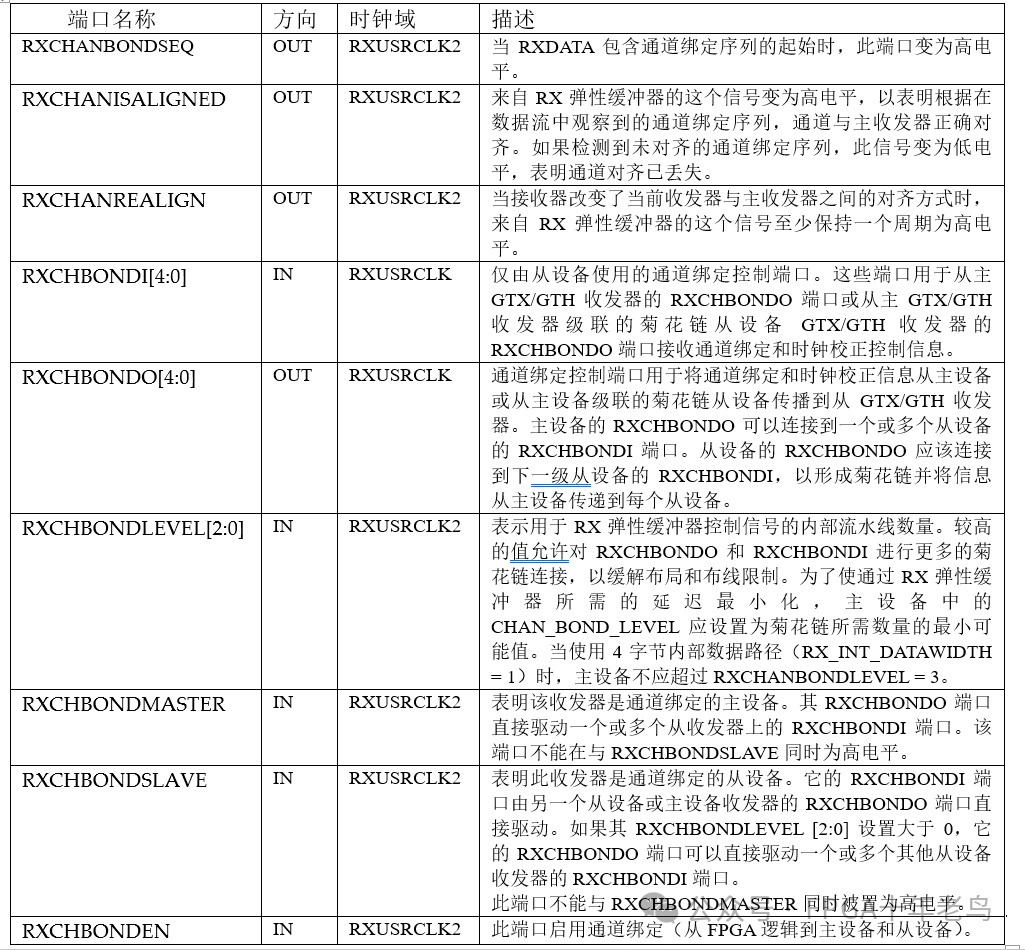

通道绑定相关的端口,如下表所示。

由于通道绑定需要使用 RX 缓冲区,因此RXBUF_EN 属性必须设置为 TRUE。

配置 GTX/GTH 收发器进行通道绑定需要以下步骤:

1. 设置每个GTX/GTH 收发器的通道绑定模式。

2. 将主收发器的 RXCHBONDMASTER 端口拉高。

3. 将从收发器的 RXCHBONDSLAVE端口 拉高。

4. 直接或通过菊花链将通道绑定端口从主设备连接到每个从设备。

每组通道绑定的 GTX/GTH 收发器必须有一个主设备和任意数量的从设备。通道绑定操作需要将主 GTX/GTH 收发器 RXCHBONDO 端口连接到组中所有从属收发器的 RXCHBONDI 端口。只有属于同一列的 GTX/GTH 收发器才能通道绑定在一起,且相邻的 GTX/GTH 收发器需要直接连接。

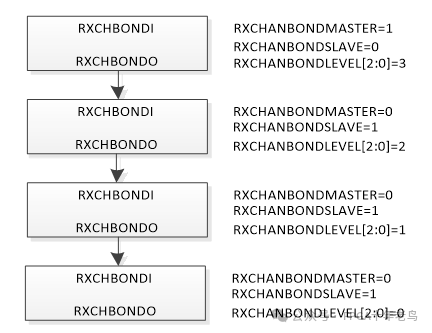

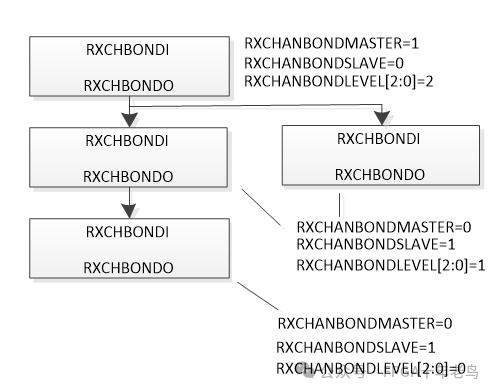

当 GTX/GTH 收发器直接连接时,随着收发器距离越来越远,满足时序限制变得困难。该问题的解决方案是以菊花链方式连接收发器。使用 RXCHBONDLEVEL[2:0] 端口执行菊花链,以允许主设备和从设备之间有额外的管道级。每个从设备的 RXCHBONDO 端口用作来自主设备的 RXCHBONDO 路径中的管道级。下面两个图显示了两个菊花链示例。

当决定 GTX/GTH 收发器之间的通道绑定端口之间的连接时,我们要记住 RXCHBONDI 和 RXCHBONDO 属于 RXUSRCLK 时钟域。随着 RXUSRCLK 频率的增加以及直接连接的收发器之间的距离越来越远,满足 RXUSRCLK 的时序约束变得越来越困难。只要满足时序限制,就可以将相邻的收发器通道绑定在一起。

选择 GTX/GTH 收发器列中间的 GTX/GTH 收发器作为通道绑定的主收发器,可以在连接通道绑定端口时实现最大的灵活性。当通道绑定主机位于 GTX/GTH 收发器列的中间时,可以与主机北侧和南侧的 GTX/GTH 收发器进行连接。由于 GTX/GTH 收发器专用时钟布线结构,将通道绑定主机置于 GTX/GTH 收发器列中心的另一个好处是,可以使用单个时钟引脚将多达 12 个 GTX/GTH 收发器通道绑定在一起一对。

只要满足时序约束,特定 RXCHHANBONDLEVEL 上的 GTX/GTH 收发器的数量就没有限制。

(四)通道绑定和时钟校正之间的优先级

时钟校正和通道绑定电路都对 RX 弹性缓冲器的指针执行操作。通常,两个电路一起工作不会发生冲突,除非时钟校正事件和通道绑定事件同时发生。在这种情况下,两个电路之一必须优先。要使时钟校正的优先级高于通道绑定,必须将 CLK_COR_PRECEDENCE 设置为 TRUE。要使通道绑定具有更高的优先级,必须将 CLK_COR_PRECEDENCE 设置为 FALSE。

-

FPGA

+关注

关注

1624文章

21580浏览量

600797 -

收发器

+关注

关注

10文章

3357浏览量

105750 -

接收器

+关注

关注

14文章

2452浏览量

71721 -

端口

+关注

关注

4文章

938浏览量

31964

原文标题:Xilinx 7系列FPGA收发器——13、通道绑定

文章出处:【微信号:FPGA十年老鸟,微信公众号:FPGA十年老鸟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

关于FPGA如何连接CAN收发器?

请问通道绑定是导致GTP收发器数据损坏的原因吗?

FPGA高速收发器设计要遵循哪些原则?

收发器向导中启用8b/10b编码器的方法是什么?

介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题

FPGA高速收发器设计原则

Altera发售业界性能最好、具有背板功能的收发器Stratix V FPGA

Xilinx推出UltraScale FPGA收发器设计

Virtex UltraScale+ FPGA收发器的演示

Xilinx 7系列FPGA收发器架构之硬件设计指导(一)

FPGA收发器的通道绑定功能

FPGA收发器的通道绑定功能

评论