在无线收发器等应用中,系统一般处于偏远地区,通常由电池供电。由于鲜少有人能够前往现场进行干预,此类应用必须持续运行。系统持续无活动或挂起后,需要复位系统以恢复操作。为了实现系统复位,可以切断电源电压,断开系统电源,然后再次连接电源以重启系统。本文将探讨使用什么方法和技术可以监控电路的低电平有效输出来驱动高端输入开关,从而执行系统电源循环。

为了提高电子系统的可靠性和稳健性,一种方法是实施能够检测故障并及时响应的保护机制。这些机制就像安全屏障,能够减轻潜在损害,确保系统正常运行。电源循环可以确保系统正常运行并提供保护,通常在系统无响应和不活动时工作,以使其能够持续运转。电源循环借助电源开关实现,该开关会先断开电源输入与下游电子系统之间的路径,再闭合相关路径以重启系统。一旦系统的微控制器单元(MCU)无响应,并且持续不活动,系统就会进入复位模式,开始电源循环。

较常用于实现高端电源路径或输入开关的方法是使用MOSFET。N沟道或P沟道MOSFET均可用作输入开关,每种开关的驱动要求各有不同。驱动N沟道MOSFET作为高端开关有点复杂,因此,通常会选用P沟道MOSFET。

监控电路通过监测电源电压和/或使用看门狗定时器检测是否存在脉冲,可以轻松检测到系统是否处于不活动状态。看门狗定时器功能增强了监控电路作为综合保护解决方案的能力。一旦检测到不活动状态,看门狗定时器就会置位复位输出,该输出通常是低电平有效信号。此信号可用于将微控制器置于复位模式,或触发不可屏蔽中断,促使系统采取纠正措施。虽然低电平有效输出主要用于复位微控制器,但在系统长时间无响应等情况下,也需要执行电源循环。为此,可以利用多种技术从监控电路低电平有效输出驱动高端P沟道MOSFET输入开关,从而获得更出色的系统可靠性。

使用 MOSFET 作为高端输入开关

图1为一个应用电路,使用了高端输入开关保护下游电子系统不受掉电故障影响。MOSFET 支持根据应用需要,轻松选择适当的电压和电流额定值,是系统高端开关设计的理想器件。

图1.高端输入开关实现示例,可保护系统不受掉电故障影响

高端输入开关可以是 N 沟道或 P 沟道 MOSFET。栅极电压较低时,N 沟道 MOSFET 开关断开,电源电压连接随之断开。要使 N 沟道 MOSFET 完全闭合并将电源连接到下游电子系统,栅极电压必须比电源电压高,并且差值需至少等于 MOSFET 阈值电压。因此,如使用 N 沟道 MOSFET 作为高端输入开关,将需要额外配置电路,例如电荷泵。有些保护电路还集成了比较器和电荷泵来驱动高端 N 沟道 MOSFET,同时保持解决方案的简单性。使用 P 沟道 MOSFET 作为高端输入开关不需要电荷泵,但极性相反。这种方法更简单,因而成为许多应用的常用方法。

监控电路输出驱动输入开关

在电路中使用P沟道MOSFET时,先为栅极、源极和漏极端建立适当的偏置条件非常重要。栅源电压(VGS)在控制MOSFET导通方面起着关键作用。对于P沟道MOSFET,栅极电压必须比源极电压低,并且差值需至少等于MOSFET阈值电压。此负偏置确保P沟道MOSFET偏置到其有源区,使电流可以从源极流向漏极。此外,栅源阈值电压 (VGS(th)) 决定了在栅极和源极端子之间建立导电通道所需的最小电压。对于P沟道MOSFET, (VGS(th)) 通常指定为负值,表示相对于源极而言,栅极电压需要足够低才能导通。另一个重要考虑因素是漏源电压(VDS),这是施加在漏极和源极端子上的电压。MOSFET必须在规定的VDS限值内工作,以防止损坏器件。

电压监视器或监控电路可以为其逻辑电平输出提供两种选择:低电平有效和高电平有效输出信号。前者“低电平有效”是指当输入条件为真且得到满足时,输出置为低电平;而当输入条件为假时,输出置为高电平。后者“高电平有效”是指当输入条件为真时,输出置为高电平;而当输入条件为假且未得到满足时,输出置为低电平。监控电路常用于复位微控制器,因此故障期间会使用低电平有效输出将微控制器的复位引脚拉低。利用高电平有效输出驱动P沟道MOSFET非常简单,对于开漏拓扑来说尤为如此。

监控电路的高电平有效输出连接到 P 沟道 MOSFET 的栅极。当监控的电压低于指定阈值时,OUT 引脚将栅极拉低,接通 P 沟道 MOSFET。负载因此连接到电源电压。当监控的电压超过阈值时,OUT 引脚变为高电平,P 沟道 MOSFET 关断,负载与电源电压断开连接。

图 2 中, 高压可调时序控制和监控电路MAX16052用作过压保护电路。该器件的OUT引脚直接连接到P沟道MOSFET的栅极。P沟道MOSFET的源极连接到输入电压,漏极连接到负载。外部上拉电阻连接在VCC和P沟道MOSFET栅极之间,以在OUT引脚为低电平时让栅极保持高电平。

图2.P沟道MOSFET用作高端输入开关,可提供过压保护

当监控的电压低于MAX16052指定的固定阈值时,OUT引脚将栅极引脚拉低,导致P沟道MOSFET开关处于短路状态或导通状态。当监控的电压超过阈值时,OUT引脚变为高电平,P沟道MOSFET关断,负载与电源电压断开连接。

在某些应用中,期望的监控要求可能仅适用于低电平有效输出。这意味着,当满足监控条件时,输出信号为低电平。在这些情况下,我们必须要借助一些技术来利用低电平有效输出控制输入开关。例如,系统32秒不活动后微控制器需要复位,128秒持续不活动后系统需要启用电源循环,那么可以使用看门狗定时器的看门狗输入(WDI)引脚来检测不活动情况。当一段时间(看门狗超时时长tWD)内没有检测到脉冲或变化时,看门狗输出(WDO)变为低电平。带有看门狗定时器的MAX16155nanopower电源监控器有多个型号,可以满足所需的32 s和128 s看门狗超时时长要求。为了实现所需的功能,我们需要两个看门狗定时器,一个用于复位微控制器,另一个用于启动图3所示的电源循环例程。其中要解决的主要挑战在于需确定如何使用不同型号看门狗定时器的低电平输出,以在不活动或系统无响应状态下断开输入开关,实现电源循环。

图3.使用了两个具有不同看门狗超时时长的 MAX16155 看门狗定时器,分别用于软复位和电源循环

驱动 P 沟道高端开关的一种方法是使用 NPN 双极结型晶体管(BJT),如图4所示。此电路形成一个逆变器,将来自看门狗输出的低电平有效信号转换为P沟道 MOSFET 开关所需的高电平逻辑信号。

图4.使用NPN双极结型晶体管(Q1)从低电平有效输出驱动P沟道MOSFET(Q2)

当系统处于活动状态时,MAX16155 WDO引脚的看门狗输出处于空闲状态,通常为高电平。然后会通过限流电阻网络连接到驱动晶体管的基极引脚。WDO引脚的正常高电平输出提供必要的基极-发射极电压,作为NPN双极结型晶体管的控制输入。它在基极-发射极结上建立足够的电压,使晶体管进入导通状态。

电阻分压器连接到高端MOSFET开关的栅极引脚和源极引脚,以控制其栅源电压(VGS)。该栅源电压决定了MOSFET是保持导通状态还是关断状态。当WDO引脚激活NPN双极结型晶体管时,电流流过晶体管。这会将电阻分压器拉低至GND,从而改变电阻分压器结点处的电压。然后,此电压被施加到高端MOSFET的栅极引脚。这会产生一个电位差,栅极引脚的电位低于源极引脚的电位,导致MOSFET导通。当MOSFET处于导通状态时,电源就被提供给系统微处理器或负载。图5显示了系统处于活动状态,电源通过开关Q2提供的电流流动情况。

图5.正常运行时的电流——系统处于活动状态

然而,当微处理器无响应或无法在MAX16155看门狗定时器的预定超时时长内提供输入脉冲时,就会发生看门狗超时事件,WDO置为低电平。因此,NPN BJT Q1的基极被拉至地,导致其关断。当Q1断开时,P沟道MOSFET Q2上栅极和源极的电压将大致相等,这足以使其关断。

如图5所示,NPN双极结型晶体管的集电极引脚连接到高端MOSFET两端的电阻分压器。由于NPN双极结型晶体管处于关断状态,电阻分压器结点和栅极上的电压将大致等于源极引脚中的电压。这将导致MOSFET的栅极和源极之间的电位差为零,从而无法满足MOSFET Q2保持导通状态所需的VGS阈值。因此,随着MOSFET关断,微处理器的3.3 V电源也被断开,从而有效切断微处理器或负载的电源。系统不活动和电源循环期间的等效电路和电流如图6所示。

图6.系统不活动期间的电流流动——发生电源循环

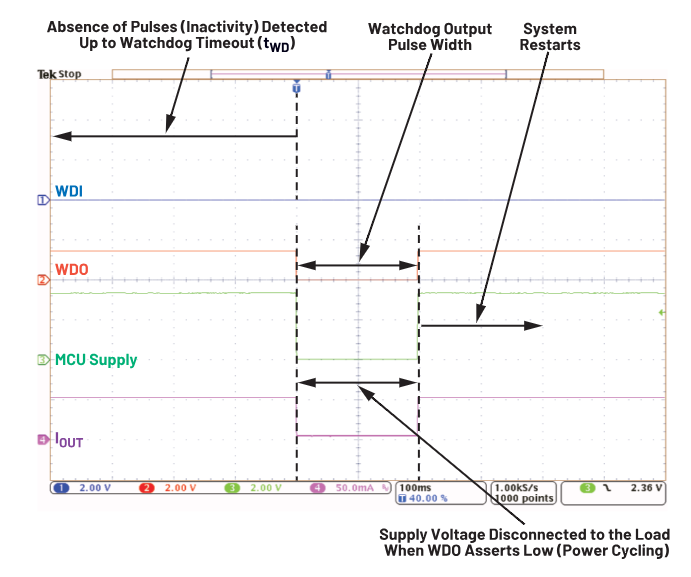

当WDO输出脉冲宽度完成并返回高电平后,系统恢复正常运行。在此阶段,微处理器恢复向WDI引脚发送常规输入脉冲,以防更多看门狗超时事件发生。NPN双极结型晶体管返回活动状态,使高端MOSFET可以保持导通状态,确保微处理器或负载的电源不间断。图7显示了使用NPN双极晶体管的电源循环事件期间的波形。如CH1所示,在WDI信号中未检测到任何变化,这意味着系统处于不活动状态。经过超时时长后,CH2中的WDO信号置为低电平,在此期间,高端输入开关Q1断开。因此,CH3中没有测量到电压,MCU也没有电源电压,系统开始重启。CH4是负载消耗的输出电流,该电流变为零安培,表明负载已与电源电压断开连接。

图7.驱动电路中采用NPN双极结型晶体管的信号(CH1—WDI信号;CH2—WDO信号;CH3—MCU电源;CH4—IOUT).

使用NPN双极结型晶体管作为高端开关驱动器的主要优点之一是双极结型晶体管的成本较低。然而,偏置NPN双极结型晶体管需要借助电阻等附加外部元件进行适当调整。

N沟道MOSFET用作驱动电路

另一种采用N沟道MOSFET的驱动电路可用来控制高端P沟道MOSFET。与使用双极晶体管相比,这种方法有几个优点。

N沟道MOSFET的低导通电阻可确保器件上的压降非常小,因而功耗更低,能效更高。MOSFET的快速开关特性可缩短响应时间,监控系统的实时性能得以增强。MOSFET的另一个优点是开关损耗更低,工作频率更高。这有助于实现平稳高效的操作并节省电量,对电池供电等类似应用非常有益。

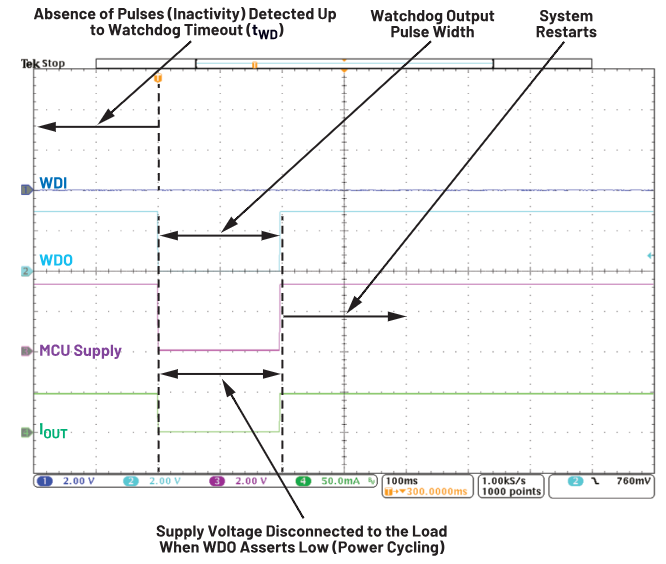

此外,栅极驱动要求比双极结型晶体管的要求更低,因此可以进一步简化驱动电路,减少需要的元件数量。看门狗输出可以直接驱动图8所示N沟道MOSFET的栅极。WDO的上拉电压应达到N沟道MOSFET的栅极阈值电压VGS(th)才能正常工作。当系统处于活动状态时,WDO的逻辑高电平输出电压将使Q1导通,进而Q2导通,向系统供电。与双极晶体管的情况一样,在系统不活动期间,WDO引脚的逻辑低电平输出将关断Q1并断开Q2,从而切断系统的电源电压。使用N沟道MOSFET作为驱动电路时,电源循环期间的信号行为如图9中捕获的波形所示。

Figure 8. Using an N-channel MOSFET (Q1) in driving a P-channel MOSFET (Q2) from an active low output.

图9.驱动电路中采用N沟道MOSFET的信号(CH1—WDI信号;CH2—WDO信号;CH3—MCU电源;CH4—IOUT).

本文所讨论的高端开关驱动方法不仅对无线收发器有益,而且对故障期间(例如功能和本质安全系统中的过压和过流情况)需要通过电源循环例程来提供系统保护的其他应用也很有帮助。检测级取决于发生电源循环所需的条件,既可以是检测电压故障的电压监控器,或是防止过流的电流传感器,也可以是其他技术。本文讨论了如何使用具有低电平有效输出的传感器和电源监控器来实现电源循环,从而保护下游系统。

结论

市面上有许多技术支持使用了来自监控电路的低电平有效信号来驱动高端开关,以实现电源循环。带有附加元件的NPN双极晶体管是一种成本较低的选择,可满足驱动P沟道MOSFET输入开关的要求。另一方面,N沟道MOSFET方案需要的元件更少,更容易实现,但总体成本更高。N沟道MOSFET在用作高频开关时也表现出不少优势。这两种方法都经过了充分验证,可为系统电源循环设计带来裨益。

-

微控制器

+关注

关注

48文章

7542浏览量

151316 -

MOSFET

+关注

关注

147文章

7156浏览量

213140 -

电源开关

+关注

关注

12文章

1033浏览量

44559 -

监控电路

+关注

关注

1文章

89浏览量

23149

原文标题:如何利用低电平有效输出驱动高端输入开关?

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为什么单片机有些管脚要设计成低电平有效?

数字电路为什么是低电平有效的多

PWM的输入是高电平有效还是低电平有效的?

为什么单片机管脚设计成低电平才有效

利用低电平有效输出驱动高端输入开关

利用低电平有效输出驱动高端输入开关

评论