以下文章来源于CAE工程师笔记 ,作者CAE工程师笔记Tony

随着基于半导体技术的电子器件和产品在生产和生活中广泛应用,以集成电路为核心的半导体产业已成为推动国民经济发展的支柱型产业。为了满足消费者对电子产品轻薄化、高性能和低功耗的发展需求,半导体集成电路和集成电路封装技术也朝着高密度集成和系统化发展方向前进。

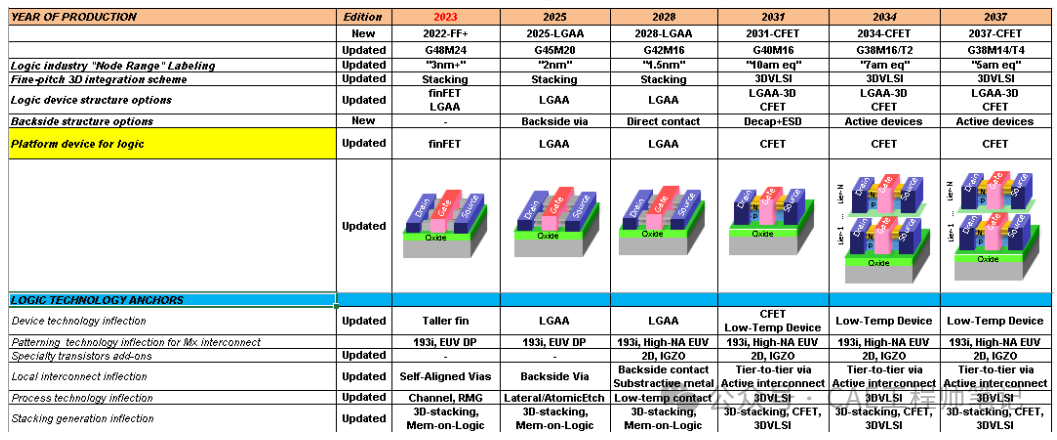

近年来 5G、AI、Autopilot、HPC 等新兴领域的发展,要求电子器件具有更低的信号传输延迟和更大的数据吞吐量。此外,随着集成电路晶体管特征尺度逐步逼近物理极限,进一步提升单颗芯片的集成度面临技术难度和成本激增的严峻问题,先进电子封装技术被认为是延续摩尔定律的关键途径。

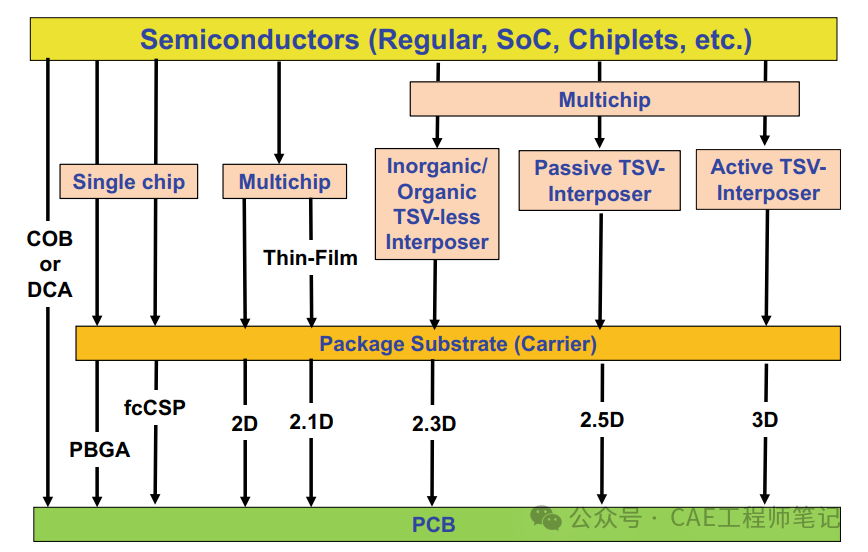

全球半导体行业领域内对于先进封装技术和传统封装技术通过是否有焊线进行区分。传统封装通常采用引线框架作集成电路线路互通和支撑连接的载具,典型的传统封装形式由双列直插式封装(DIP)、小外形封装(SOP)、小型方块平面封装(QFP)等,随着智能移动终端、物联网、人工智能和大数据等新兴领域的快速扩展,全球封装市场为适应小型化,高集成的需求在不断扩容。当前已发展三维集成封装、晶圆/面板级扇出型封装等先进封装技术。越来越多的芯片被集成到一个封装体中,促使电子封装向系统级封装(System In Package)和异构集成(Heterogeneous Integration)方向发展。

系统级封装(System In Package)基于多种先进封装互连技术,将多个不同功能模块集成组装在一个封装包内。国际半导体技术路线图(ITRS 2005)在组装与封装中对系统级封装定义为:

系统级封装是采用任意组合, 将数个具有不同功能的有源电子器件、可选择性的无源器件及如机电系统或光学器件等组装成为具有多种功能的单个标准封装件,从而形成一个系统或者子系统。

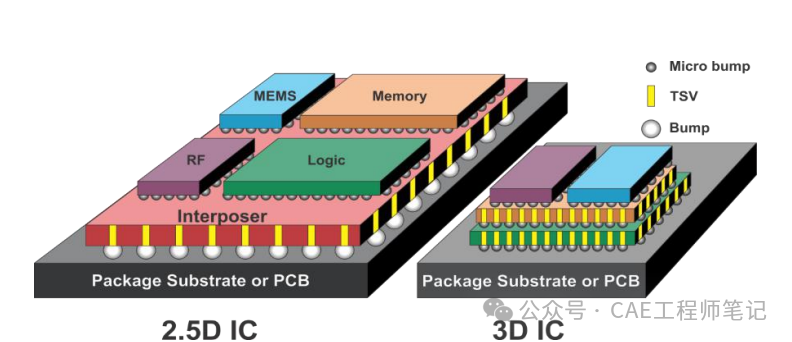

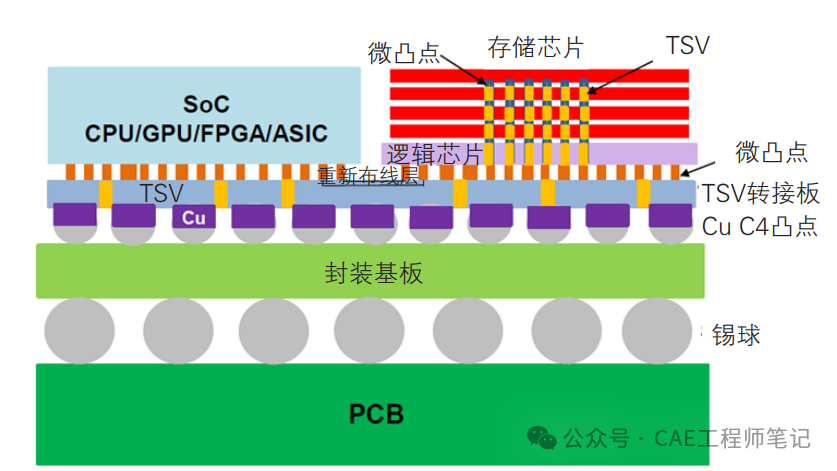

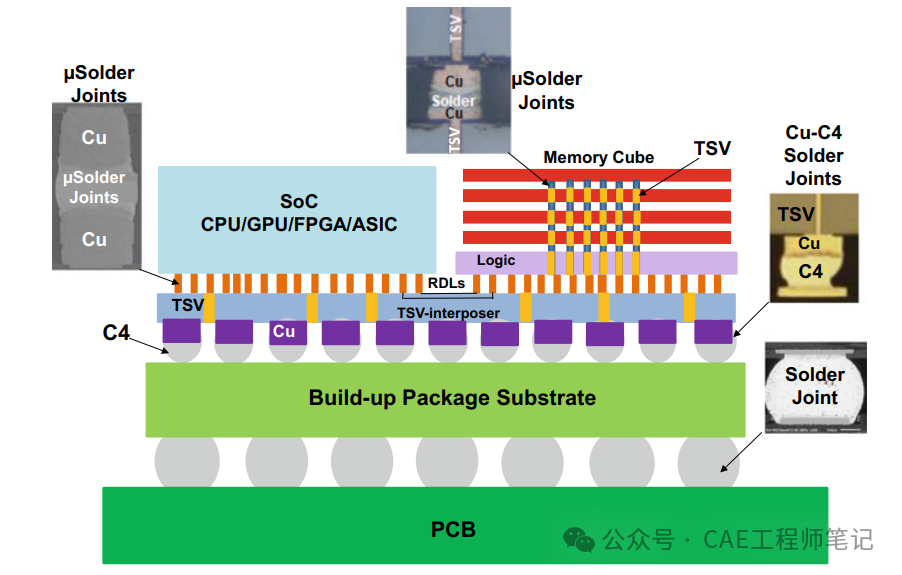

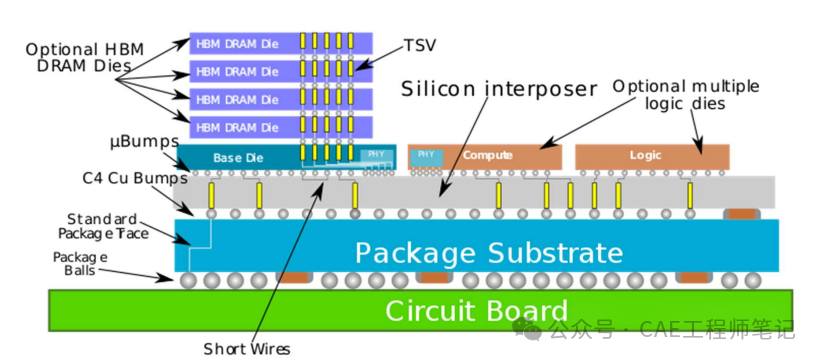

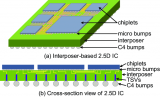

行业内为了实现元器件更小尺寸和封装密度更高、成本更低的发展目标, 2.5D/3D 封装技术作为系统封装的关键封装技术已经成为未来重点发展的方向。2.5D/3D 封装都是基于此前二维平面封装 X-Y 平台的基础上,通过TSV技术在 Z 方向实现芯片互连或者堆叠。2.5D 封装是通过 TSV 技术将多个芯片通过硅转接板互连,多个芯片堆叠在内含有 TSV 的硅转接板的顶部,因此硅转接板是芯片和基板之间的桥梁,能够为系统提供更多的 I/O 带宽。而3D封装是将具有 TSV 结构的芯片叠合起来在 Z 向完成互连,将平面组装发展为具有纵向高度的立体组装,具有更高的集成度。

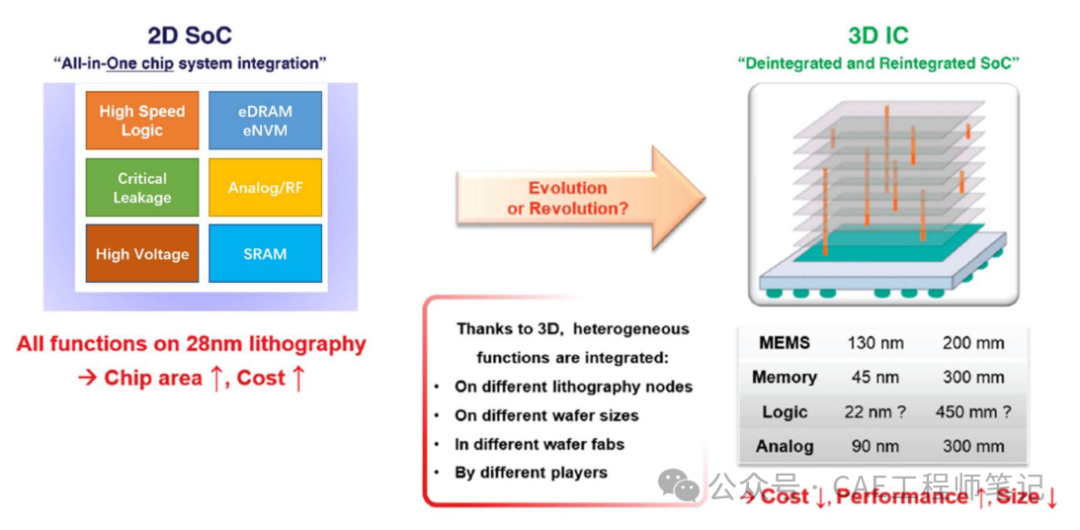

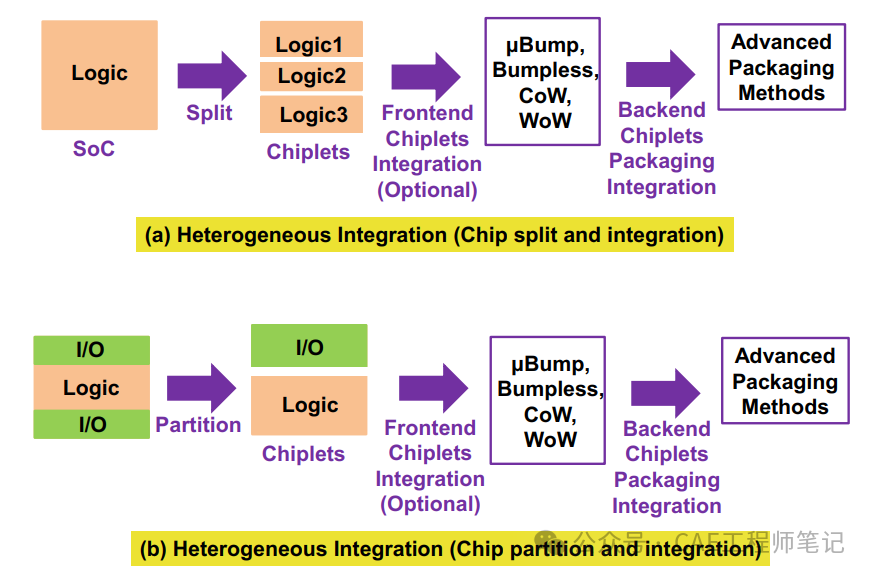

芯片异构集成是使用先进封装技术将来自不同晶圆制造厂商且具有不同晶圆尺寸和特征技术节点或具有不同材料和功能的系列芯片,采用并排或堆叠方式布局到转接板或封装基板上组成系统或子系统,从而构成集成度更高、性能更强、功能更多的更高级的系统级封装技术。

异构集成面向更细节距、更多输入输出端口、更高密度和更高性能的应用,可以使整个封装系统性能得到数量级上的提升。异构集成是在同一个封装中集成多个芯片,使得这个封装体具有特定的且更复杂的功能和更小的成形因子,而与将大部分功能集成到一个芯片中的系统级芯片(SoC)有着明显的不同。

举例来说,为了进一步提高芯片的处理能力,通常会增加 SoC 的核数,进一步提高晶体管微缩化,这不仅会造成设计研发周期延长和成本剧增,还会使得单颗芯片的面积增加,从而使生产良率降低。

采用异构集成技术进行整合,可以将 SoC 分割成更小的芯片(Chiplet)进行制造,从而可以从同样大小的晶圆上获得更多的芯片,使得生产良率提升数倍,并大大降低成本。并且不同功能的芯片有着不同的最优工艺制程,采用相同工艺制程制造不同功能的芯片反而使芯片的性能得不到有效发挥。

异构集成封装系统中集成了多种不同功能的芯片,为满足芯片之间及芯片与外部电路的高效交流,必须为之建立低延迟、高带宽的信号传输路径,这就需要采用包括转接板、互连焊点、硅通孔(TSV)或模塑通孔(TMV)在内的封装技术。

2.5D 异构集成封装技术在横向纵向技术对比上具有显著的性能提升、成本可控和效率提高等优势:

封装效率高,高集成。同一封装体内可多芯片组合贴装,减少封装体积。

降低系统成本。相比传统封装,可以实现多芯片多模块互连在一个系统里,节省更多系统设计和产出成本。

低功耗,稳定性好,电性能高。相比而言焊点数目减少,封装体积重量降低,元器件互连路线缩短。

应用更广泛。可以在光通信系统,传感器系统以及 MEMS 系统等更多领域。

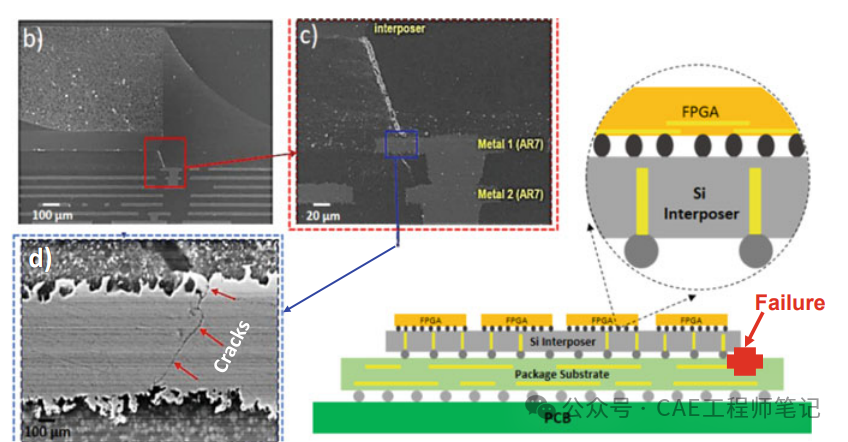

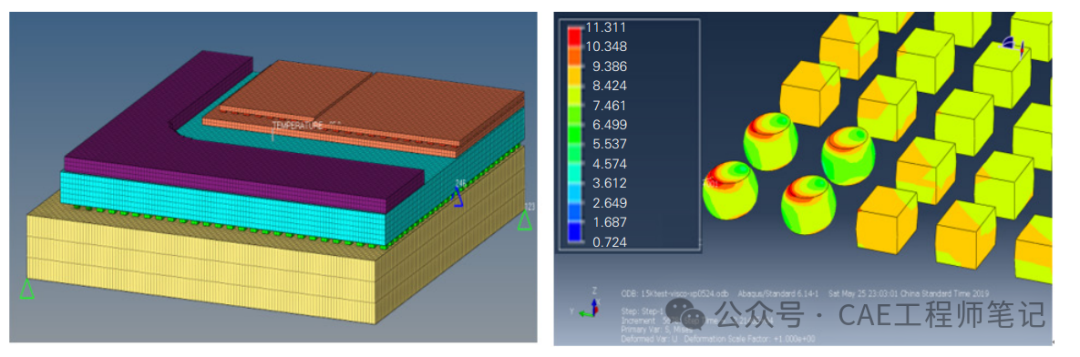

2.5D 异构集成封装结构精细且复杂,为保护脆弱的互连焊点,降低互连线路的电容电感,通常采用底部填充胶(Underfill)、环氧模塑料(EMC)、低介电常数材料(Low-k Dielectric)等多种材料构成复合材料体系。因此,封装结构中存在许多材料界面,由于界面两侧材料结合力较弱且不同材料性质差异较大,主要是热膨胀系数(CTE)和弹性模量的差异,导致封装器件在制造、测试和服役过程中界面开裂甚至大范围剥离。

2.5D 异构集成封装通常采用跨尺度互连焊点进行多级装配,从而满足超高输入输出端口数量的需要,处于不同级别的互连焊点经历回流次数不同且由于应用尺寸的差异,导致这些跨尺度互连焊点力学性能具有较大差异。

例如在三维堆叠的 HBM芯片之间,以及 GPU 与硅转接板之间的微凸点互连尺寸小于 25 μm,转接板与封装基板之间的 C4 焊点尺寸在 100 μm 左右,而封装基板与 PCB 板之间的 BGA 焊点尺寸可以达到数百微米。互连焊点作为芯片与外部电路连接和交流的重要通道,它是最容易出现可靠性问题的薄弱环节。

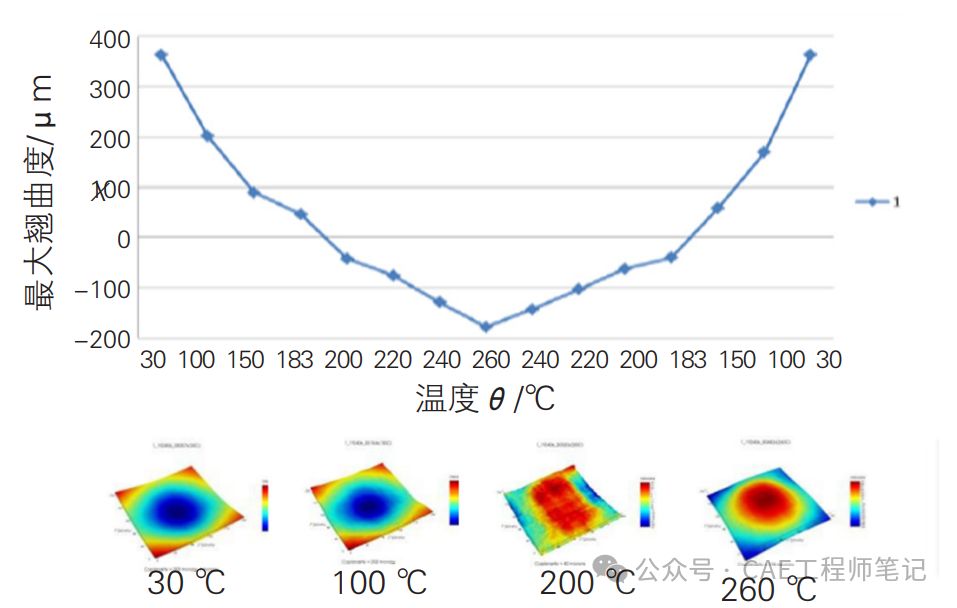

同时多层不同材质的结构分布会使得整个封装结构在热服役环境过程中由于热不匹配产生封装可靠性问题。由于热膨胀系数之间的差异,在服役过程中,各材质在热或冷或冷热交替的环境中产生不同程度的变形,因而在接触界面之间产生应力集中现象。

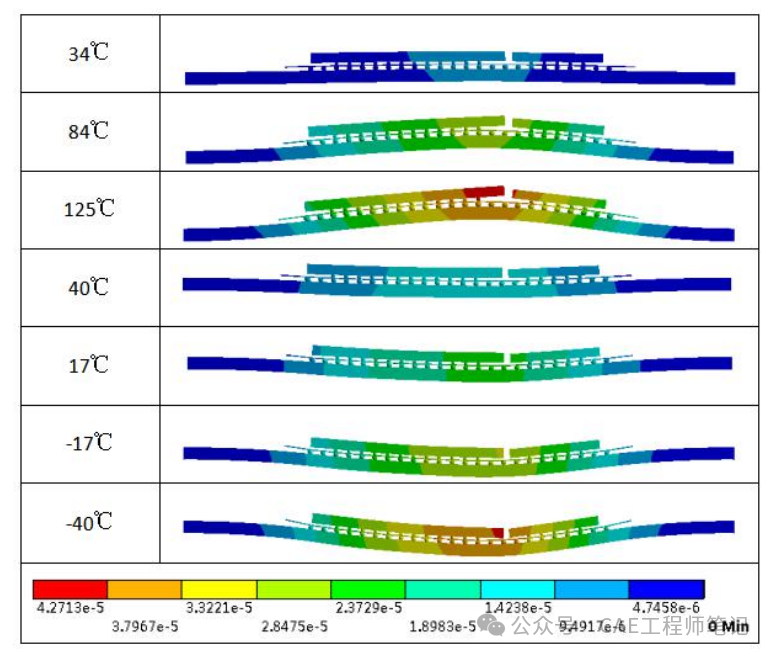

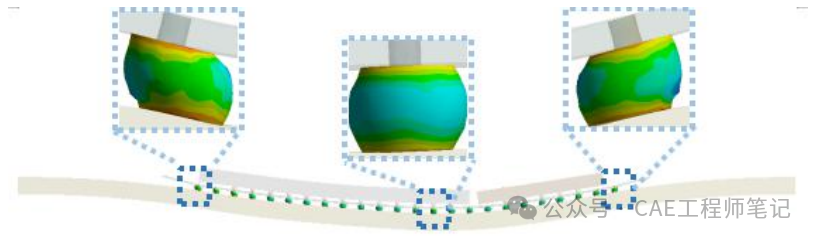

下图案例为在一个温度循环过程中不同温度下 2.5D 封装结构模型的翘曲变形情况。从图中可以看出,在升温阶段从室温升至最高温度125℃ 过程中,结构模型产生向 Z 向正方向的翘曲变形,在 125℃ 时翘曲变形达到正向最大值。而在降温阶段从室温降至最低温度 -40℃ 过程中,结果模型产生向 Z 向负方向的翘曲变形,在 -40℃ 时翘曲变形达到负方向最大值。

在温度循环中由于封装结构材质热膨胀系数差异,焊点热膨胀系数最大,硅材质的芯片和硅转接板热膨胀系数最小,结构受热在 Z 向正方向发生翘曲变形。随着温度升高,焊点热膨胀系数增大,与芯片和硅转接板差异增大,结构在 Z 向翘曲变形越来越大。

总得来说,2.5D 封装的核心在于芯片与基板之间的嵌入式硅转接板,通过转接板上的 TSV 通孔、再布线层、微凸点等,达成芯片与芯片、芯片与封装基板间更高密度的互连。再结合异构集成技术将不同的芯片集成到一个封装体中,在缩短研发上市周期、提升性能、降低功耗和成本等方面具有传统 SoC 无法比拟的优势。

然而由于 2.5D 异构集成封装结构中包含 TSV-Cu/Ta/SiO2/Si 多层界面、硅转接板/微凸点的 Cu/Sn 界面等多级互连界面,热膨胀系数及结构尺寸均存在较大差异,极易在热应力作用下因热失配产生热疲劳失效。如何降低封装结构的局部应力和减小封装翘曲,从而提高封装可靠性,就显得尤为重要了。

-

半导体

+关注

关注

334文章

27693浏览量

222046 -

系统级封装

+关注

关注

0文章

36浏览量

9105 -

先进封装

+关注

关注

2文章

427浏览量

277 -

2.5D封装

+关注

关注

0文章

23浏览量

256

原文标题:先进封装技术(Semiconductor Advanced Packaging) - 10 2.5D封装与异构集成技术

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

传闻不攻自破?华为和Altera合力实现2.5D异构封装技术!

分享一下小芯片集成的2.5D/3D IC封装技术

日本计划量产2nm芯片,着眼于2.5D、3D封装异构技术

2.5D与3D封装技术:未来电子系统的新篇章

探秘2.5D与3D封装技术:未来电子系统的新篇章

深入剖析2.5D封装技术优势及应用

2.5D封装与异构集成技术解析

2.5D封装与异构集成技术解析

评论