在创新加速的浪潮中,为更好地响应客户群需求,芯驿电子 ALINX 推出全新 IP 核产品线,致力于为高性能数据传输和复杂计算需求提供高带宽、低延迟的解决方案。发布的第一批 IP 核包括 10GBe/40GBe UDP 协议栈 IP 核、10GbE TCP/IP 协议栈 IP 核和 NVMe AXI IP 核。

ALINX 发布的 10GbE TCP/IP 协议栈 IP 核,能够实现符合 IEEE802.3 标准的完整协议栈,支持高达 9000 字节的 MTU,特别适用于需要大规模数据传输和实时视频处理的应用场景。

10GbE TCP/IP 协议栈 IP 核注重数据传输的可靠性,具备完整的 TCP 传输控制机制,包括流量控制、重传和保序,以确保数据的完整性和准确性。支持最多两条TCP 连接的设计使其能够在数据库同步、文件传输等应用中提供强劲稳定的传输性能。

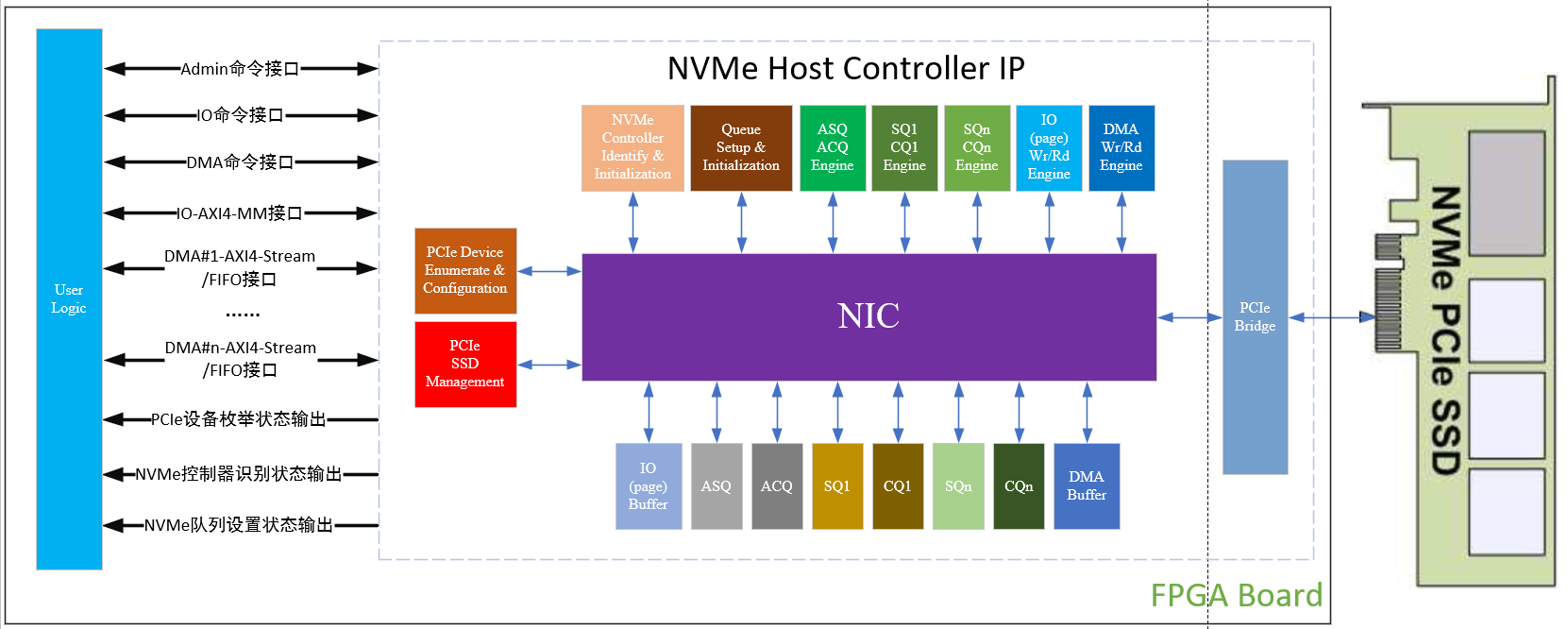

ALINX 发布的 NVMe AXI IP 核,专注于加速存储访问,通过 PCIe 接口连接外部 NVMe SSD,支持自动链路初始化和 3000MB/s 的读写速率,充分满足高性能存储应用的需求。该 IP 核便于集成到 Xilinx 架构中,在数据中心和高性能计算应用中大幅提升存储效率。

凭借高效的设计和完备的技术支持服务,芯驿电子 ALINX 的 IP 核将帮助客户在复杂的计算和存储环境中实现性能优化与快速部署,推动企业在竞争激烈的市场中持续创新与突破。

以下为产品特性介绍,完整用户手册请联系销售工程师获取。

10GbE TCP/IP协议栈IP核

产品特性

根据 OSI 分层模型实现符合 IEEE802.3 标准的 ARP、IPV4、ICMP、TCP 协议栈

支持 ARP,用于获取或发送 MAC 地址

支持 ICMP,用于响应 Ping 命令

作为 TCP 的 server,响应 client 的建联请求、断联请求,也可主动发起断联请求

ARP 报文应答支持所有来查询的应答,但只维护一个业务所用的 ARP 表

ARP 表未建立时,不响应建联请求

ARP 表已建立时,接受到配置的 TCP 监听请求后才会响应建联请求

10Gps 以太网连接,支持 TCP,IP 的校验和的产生与校验,CRC 由 MACIP 计算产生

基于 Xilinx 10G MAC IP 开发,支持最大 MTU 高达 9000 Bytes,最小 64 Bytes 的数据传输

TCP 数据报文的发送、接收、应答及心跳包的维护

TCP 传输中保序、重传、确认、快重传

TCP 传输中基于接收和发送窗口的流量控制

TCP 建联后,接收到客户端 RST 报文时,直接断开连接

最多支持两条 TCP 连接

用户接口为 AXI4stream 接口,协议栈利用 MACIP 产生的时钟 156.25MHz,10Gps 数据总线宽度 64 bit

TCP_IP 协议栈 IP core 内部数据为 8Bytes 对齐处理

应用场景

各类需要高速数据传输、高吞吐量的网络通信应用场景:

数据中心与云计算

4K/8K 视频传输与处理

高性能嵌入式系统

网络测试设备与网络监测

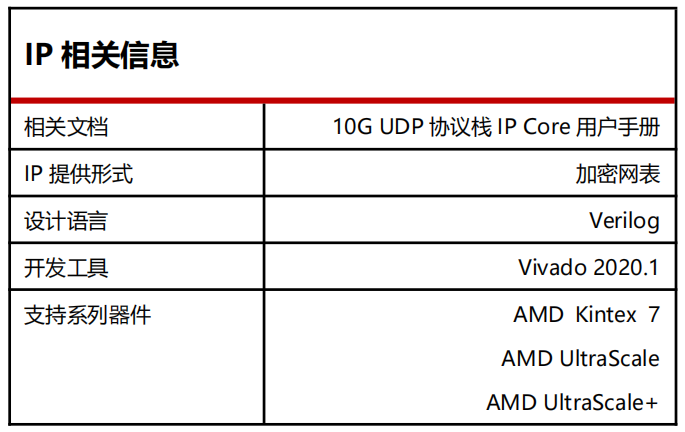

10GbE UDP协议栈IP核

产品特性

根据 OSI 分层模型实现符合 IEEE802.3 标准的 ARP、IPV4、ICMP、UDP 协议栈

支持 ARP,用于获取或发送 MAC 地址

支持 ICMP,用于响应 Ping 命令

ARP 报文应答支持所有来查询的应答,可以缓存 10 个 ARP 表

ARP 表未建立时,不会发送 UDP 数据包

10Gps 以太网连接,支持 UDP,IP 的校验和的产生与校验,CRC 由 MACIP 计算产生

基于 Xilinx 10G MAC IP 开发,支持最大 MTU 高达 9000 Bytes,最小 64 Bytes 的数据传输

用户接口为 AXI4stream 接口,协议栈利用 MACIP 产生的时钟 156.25MHz,10Gbps 数据总线宽度 64 bit

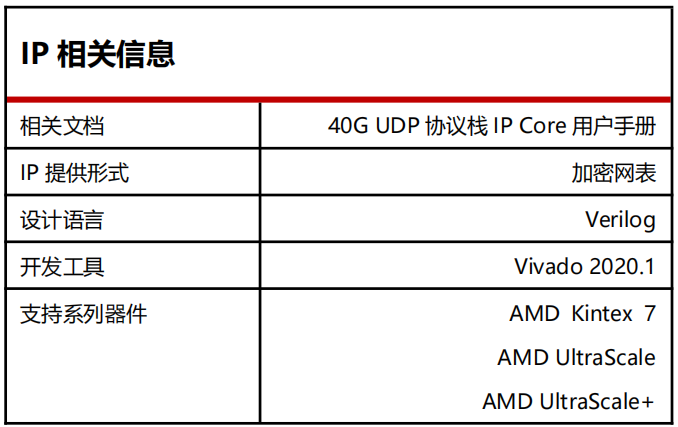

40GbE UDP协议栈IP核

产品特性

根据 OSI 分层模型实现符合 IEEE802.3 标准的 ARP、IPV4、ICMP、UDP 协议栈

支持 ARP,用于获取或发送 MAC 地址

支持 ICMP,用于响应 Ping 命令

ARP 报文应答支持所有来查询的应答,可以缓存 10 个 ARP 表

ARP 表未建立时,不会发送 UDP 数据包

40Gbps 以太网连接,支持 UDP,IP 的校验和的产生与校验,CRC 由 MACIP 计算产生

基于 Xilinx 40G MAC IP 开发,支持最大 MTU 高达 9000 Bytes,最小 64 Bytes 的数据传输

用户接口为 AXI4stream 接口,协议栈利用 MACIP 产生的时钟 312.5MHz,40Gbps 数据总线宽度 256 bit

应用场景

大规模数据中心和云计算

媒体和娱乐领域实时视频处理与传输

科研、医疗成像、基因测序等

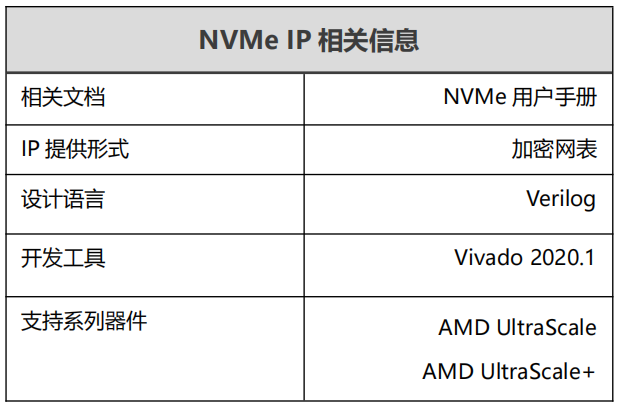

NVMe AXI IP

产品特性

实现不依靠 CPU 通过 PCIe 访问外部内存 NVMe SSD

支持命令:Identify, Write, Read, and Flush

支持 PCIe Gen 1.0,2.0,3.0,4.0

兼容 NVM Express 1.4 协议

自动初始化 NVMe 和 PCIe 链路硬件模块

自动的提交和完成命令

支持最大每个队列 65535 个 I/O 命令

基于 PCIe3.0 X4 读写速率均可达到 3000MB/s

MPSMIN(最小内存页传输大小):4Kbyte

MDTS(最大数据传输大小):至少 128Kbyte 或者没有限制

LBA 单元:512 字节或者 4096 字节

NVMe IP 支持两个版本,包括 AXI FULL 版本和 AXI Stream 版本

实现的参考设计:XCZU19EG+FMC子板(FH1402)+SAMSUNG 980 M.2 SSD

提供完备的技术支持与定制化设计服务

应用场景

智能监控

医疗设备

审核编辑 黄宇

-

FPGA

+关注

关注

1629文章

21729浏览量

603046 -

IP核

+关注

关注

4文章

327浏览量

49485

发布评论请先 登录

相关推荐

浅谈ALINX NVMe IP产品特性

Xilinx DDS IP核的使用和参数配置

ALINX VERSAL SOM产品介绍

TCP IP协议属性设置中的IP配置

关于FPGA IP核

高性能NVMe主机控制器,Xilinx FPGA NVMe Host Accelerator IP

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

Xilinx FPGA NVMe Host Controller IP,NVMe主机控制器

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

芯驿电子 ALINX 推出全新 IP 核产品线,覆盖 TCP/UDP/NVMe AXI IP 核

芯驿电子 ALINX 推出全新 IP 核产品线,覆盖 TCP/UDP/NVMe AXI IP 核

评论