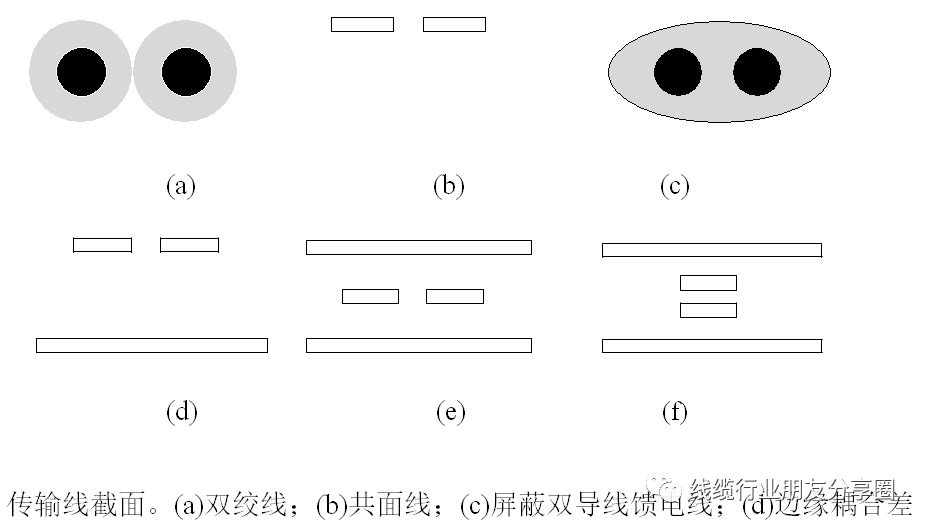

随着近几年来对速率的要求快速提高,串行总线由于有更好的抗干扰性和更少的信号线、更高的数据率而受到众多设计者的青睐。而串行总线又尤以差分信号的方式最多,差分信号与普通的单信号走线相比有3个明显的优势:抗干扰能力强;能有效抑制EMI;时序定位精确,所以越来越多的系统采用差分信号进行接收与传输。差分信号的传输需要一对传输线来实现,那么这对传输线又叫做差分对。能够用单端传输线组成差分对的两条传输线。和单端传输线相类似,差分对传输有多种多样的横截面形状。下图我们列举了最常见的几种截面几何外形。

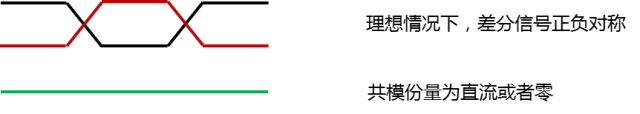

差分传输之所以能够抗干扰,这是因为对两个单端信号进行差分检测的时候,其噪声有可能会抵消。只要外界对差分对中两个单端信号上的干扰基本一致,就不会影响差分信号的传输。所以无论采取何种走线方式,关键是要控制两条传输线周围环境基本一致,并尽量减少其他信号干扰。理想情况下,差分信号是正负对称的,其共模份量为零或者只有直流份量,如下图1所示。如果差分线的正负传输线长度不等,造成传输时间不一致,实际上就是信号在时间轴上的不对称,在终端负载电阻上就能观察到图2所示的波形。显然此时的正负波形不能严格对称,差分电路中的正负电流无法抵消,于是其电源中就有共模电流份量在流动。如果研究过EMI的人都知道,共模辐射是最难对付的。

图1

所以差分信号的阻抗匹配也就成为一个非常重要的问题,目前,一般有两种不同匹配的方式,即分别并联匹配和单电阻跨接匹配。在通信过程中,有两种原因导致信号反射:阻抗不连续和阻抗不匹配。阻抗不连续或者不匹配,信号在传输线末端突然遇到阻抗不匹配,信号在这个地方就会引起反射。一旦产生反射,将会对需要的信号造成不同程度的影响,因此,应尽最大努力去消除这种反射,其中的一种方法,就是让终端电阻完全匹配。消除了反射,传输线上的能量就能全部被负载吸收,不再产生反射。那么,究竟是什么原因引起发射,为什么遇到阻抗不匹配时会发生反射呢?

无耦合时的差分阻抗

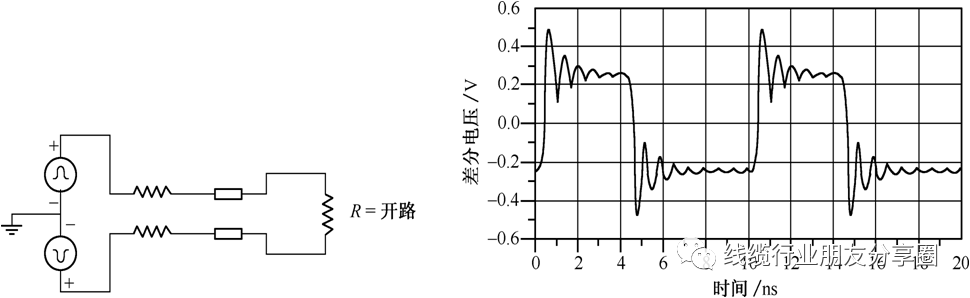

假设两条传输线相隔足够远,比如两线相隔距离至少是线宽的两倍,两条线之间的相互作用就不明显了,这就是无耦合的情况。如果一个差分信号沿差分对传输到达接收终端,那么终端的差分阻抗非常大,差分信号将会反射回源端。这种多次反射就会产生噪声,影响信号质量。下图所示的就是一个差分线末端出现的模拟差分信号。振铃的出现是由于差分信号在低阻抗的驱动器和高阻抗的线端之间的多重反弹。图中差分对互连末端没有端接,并且差分对之间没有耦合,下图为差分电路和差分线对的远端接收信号。

消除反射的一种方法就是在两条信号线的末端跨接一个端接电阻来匹配差分阻抗。对差分信号来说,信号线末端的端接电阻和差分对的阻抗是相同的,这将会消除反射。下图就是在两信号线之间加入100欧姆电阻后,接收端的差分信号。图中差分对末端有端接,并且差分对之间没有耦合,下图为差分对远端接收到的差分信号。

耦合时的差分阻抗

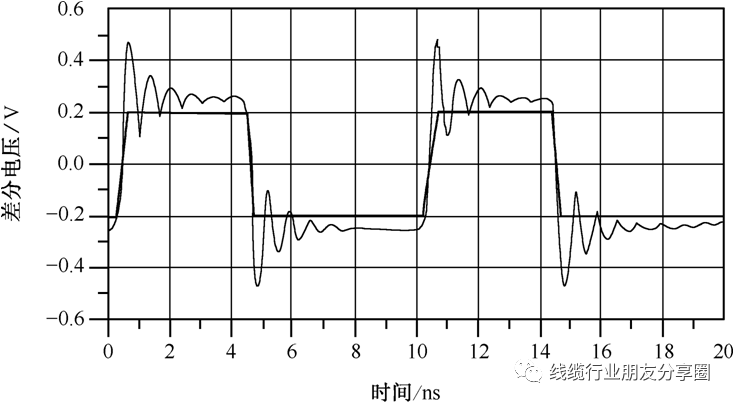

当两条带状线相距越来越近时,它们边缘的电场和磁场会重叠,二者之间的耦合程度也会越来越强。耦合程度用单位长度上的互感电容C12与互感电感L12表示。当把两信号线靠近时,C11和C12都会改变。当信号线1与其返回路径的一些边缘区域被相邻信号线干扰时,C11将减小,C12会增加。但是,负载电容CL= C11+ C12改变不大。下图所示为单位长度上负载电容CL、单位长度对角电容C11及耦合电容C12的变化情况。带状线材料是FR4,线宽5 mil,特性阻抗50欧姆,CL, C11与C12随两线的边缘举例的变化。

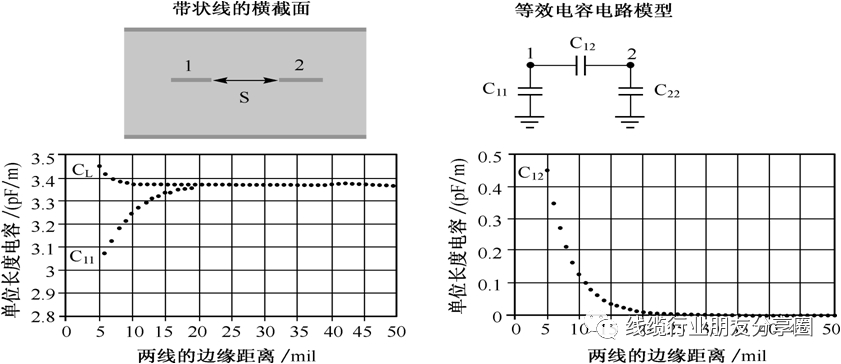

当把两信号线靠近时,L11和L12都将发生改变。下图所示为单位长度上环路自感L11的变化和单位长度上环路互感L12随两线的边缘举例的变化。由于相邻导线的感应涡流,L11将会有略微的减小(最近时的减小量小于1%),L12会增加。L11与L12随两线的边缘举例的变化。

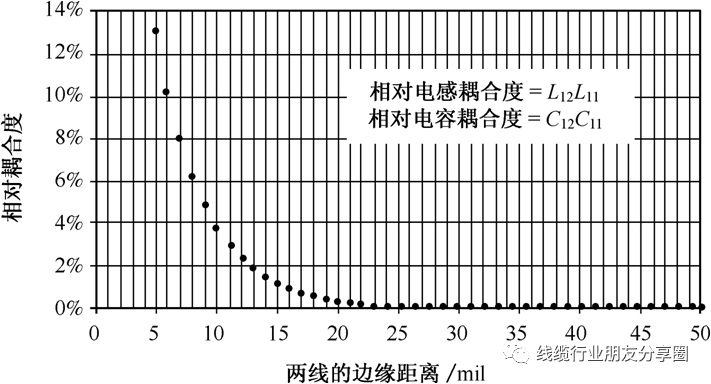

总之,把两条走线放置在一起时,耦合增加。但是,即使在间距更紧密的情况下,间距等于线宽,最大的相对耦合度(即C12/C11或L12/L11)仍小于15%。当间距大于15 mil时,相对耦合减小至1%,基本可忽略不计。下图所示为当两条50欧姆、5 mil的FR4带状线间的间距变化时相对互容和相对互感的随线距的变化,即相对电容耦合与相对电感耦合的比值,如何随间隔的变化而变化。注意,对于带状线这种有相同介质结构的传输线,两传输线的相对耦合电容与相对耦合电感是相同的,间距变化时相对互容和相对互感的变化.

差分信号线由于传输过程中存在差分模式和共模模型两种情况,所以存在各自的匹配,如果哪一种模式不匹配,那么这种模式就会出现信号震荡。通常我们工作在奇模模式下,所以不太关注共模匹配,因为理想情况下,共模电压为理想的DC电平,不匹配影响不大,如果共模噪声较大,还是需要对共模阻抗进行匹配。

-

阻抗匹配

+关注

关注

14文章

350浏览量

30794 -

串行总线

+关注

关注

1文章

182浏览量

30615 -

差分信号

+关注

关注

3文章

367浏览量

27676

发布评论请先 登录

相关推荐

TH63LVD104C+GV7600视频采集转码板,图像失真严重

怎样理解阻抗匹配_pcb阻抗匹配如何计算

差分信号的阻抗匹配

差分信号的阻抗匹配

评论