有源区工艺是指通过刻蚀去掉非有源区的区域的硅衬底,而保留器件的有源区。

1)清洗。将晶圆放入清洗槽中清洗,得到清洁的硅表面,防止硅表面的杂质在生长前置氧化层时影响氧化层的质量。

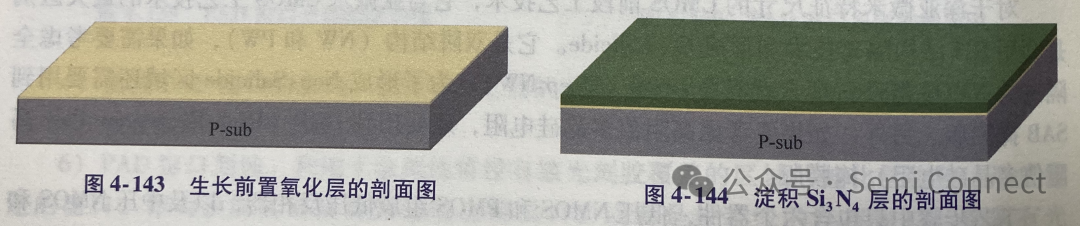

2)生长前置氧化层。利用炉管热氧化生长一层前置二氧化硅薄膜,它是干氧氧化法。利用高纯度的氧气在900°C左右的温度下使硅氧化,形成厚度约100~200A 的二氧化硅薄膜。生长前置氧化层的目的是缓解后续步骤淀积 Si3N4层对衬底的应力,因为衬底硅的晶格常数与Si3N4的晶格常数不同,直接淀积Si3N4会形成位错,较厚的氧化层可以有效地减小Si3N4层对衬底的应力。如果太薄,会托不住Si3N4,如果Si3N4层的应力超过衬底硅的屈服强度就会在衬底硅中产生位错。图4-143所示生长前置氧化层的剖面图。

3)淀积Si3N4层。利用LPCVD 淀积一层厚度约1600~1700A 的Si3N4层,利用SiH4和NH3在800°C的温度下发生化学反应淀积Si3N4。它是AA刻蚀的硬掩膜版和后续STI CMP 的停止层,也是场区离子注入的阻挡层。图4-144所示为淀积Si3N4层的剖面图。

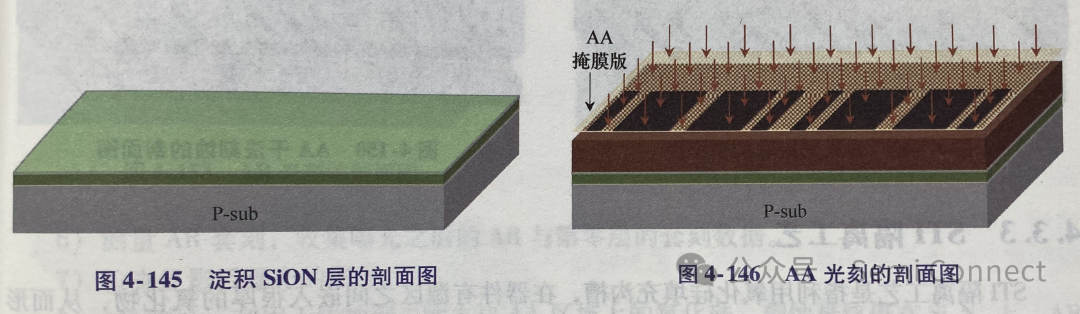

4)淀积SiON层。利用 PECVD 淀积一层厚度约200~300A 的SiON 层,利用SiH4、N2O和He在400C的温度下发生化学反应形成 SiON淀积。SiON 层作为光刻的底部抗反射层,可以降低驻波效应的影响。图4-145所示为淀积SiON 层的剖面图。

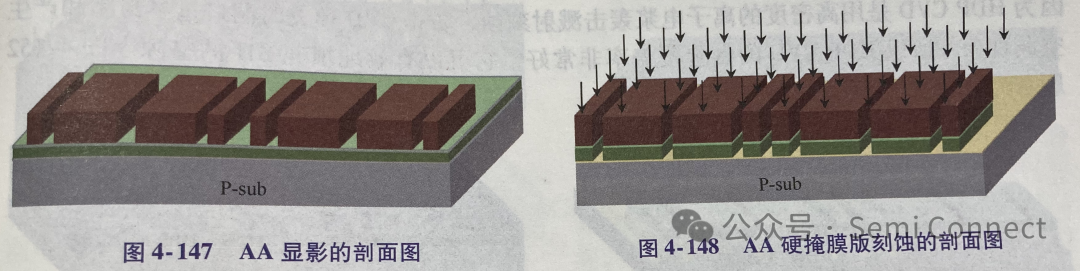

5)AA 光刻处理。通过微影技术将 AA 掩膜版上的图形转移到晶圆上,形成AA 的光刻胶图案,AA 区域上保留光刻胶。第零层作为 AA 光刻曝光对准。图4-19所示为电路的版图,工艺的剖面图是沿 AA'方向。图4-146所示为 AA 光刻的剖面图,图4-147所示为AA显影的剖面图。

6)测量 AA光刻的关键尺寸。收集刻蚀后的AA关键尺寸数据,检查 AA关键尺寸是否符合产品规格。

7)测量 AA 套刻,收集曝光之后的AA与第零层的套刻数据。

8)检查显影后曝光的图形。

9)AA 硬掩膜版刻蚀。干法刻蚀利用Ar 和CF4形成等离子浆去除没有光刻胶覆盖的Si3N4和SiO2层,刻蚀停在前置氧化层上,形成AA 区域的硬掩膜版。如图4-148所示,是AA 硬掩膜版刻蚀的剖面图。

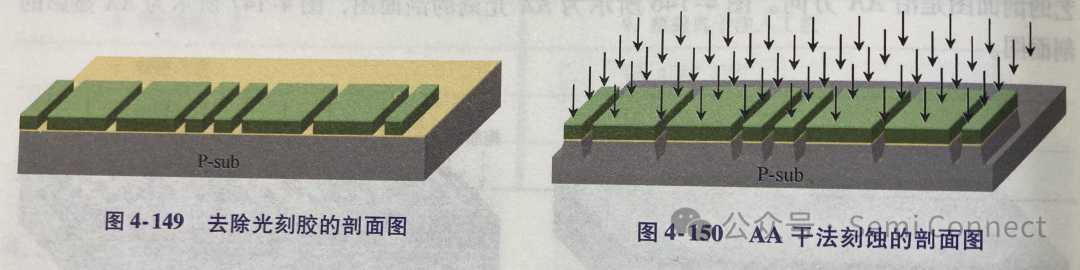

10)去光刻胶。通过干法刻蚀和湿法刻蚀去除光刻胶。图4-149所示为去除光刻胶的剖面图。

11)AA干法刻蚀。干法刻蚀利用O2和 HBr形成等离子浆去除没有硬掩膜版覆盖的硅形成晶体管有源区,刻蚀深度是0.45~0.55μm,沟槽侧壁的角度是75°~80°,最终形成AA 图形和STI。去除光刻胶再进行 AA干法刻蚀是为了防止光刻胶与衬底硅直接接触,污染衬底硅。STI可以有效地隔离 NMOS与PMOS,改善闩锁效应。图4-150所示AA干法刻蚀的剖面图。

12)测量AA 刻蚀关键尺寸。收集刻蚀后的AA 关键尺寸数据,检查 AA关键尺寸是否符合产品规格。

13)检查刻蚀后的图形。如果有重大缺陷,将不可能返工,要进行报废处理。

-

晶圆

+关注

关注

52文章

5018浏览量

128602 -

工艺

+关注

关注

4文章

622浏览量

29002 -

光刻

+关注

关注

8文章

330浏览量

30324

原文标题:有源区工艺-----《集成电路制造工艺与工程应用》 温德通 编著

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【「大话芯片制造」阅读体验】+芯片制造过程工艺面面观

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺

TRCX:掺杂过程分析

机械加工厂制造工艺过程中热处理工序位置

单片机晶圆制造工艺及设备详解

《炬丰科技-半导体工艺》IC制造工艺

浅谈晶圆制造工艺过程

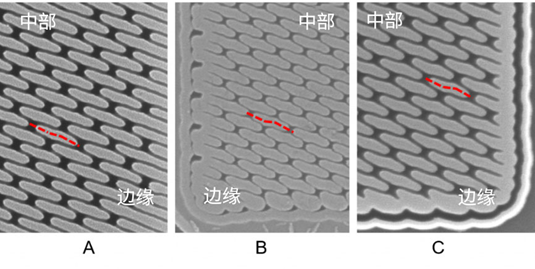

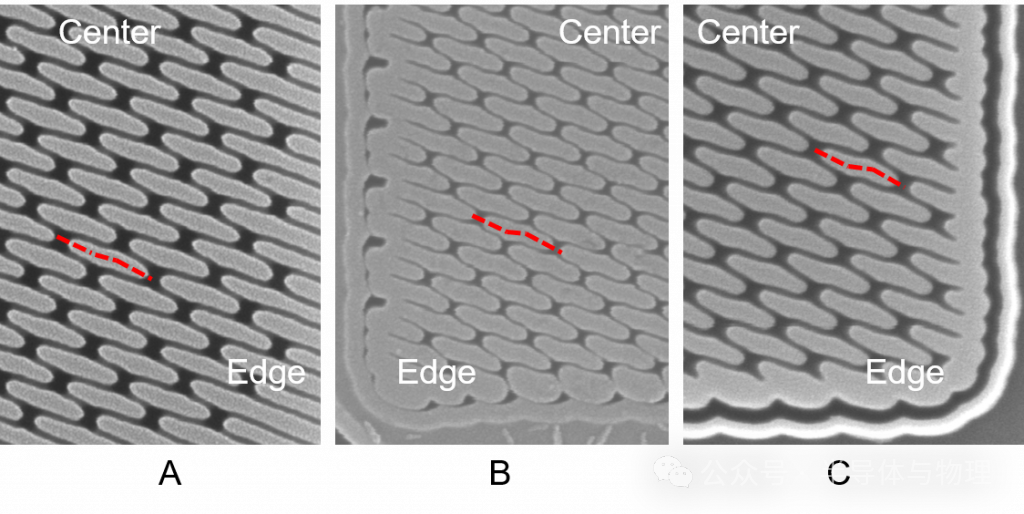

对先进DRAM工艺中有源区形状扭曲的研究

有源区工艺的制造过程

有源区工艺的制造过程

评论