Part 01

前言

在之前的两篇文章中我们介绍了运放的关键特性参数共模抑制比,以及如何设计并计算差分放大电路,差分放大电路的特点就是它可以有效放大两个输入信号的差值,同时可以有效抑制共模噪声对运放输出的影响,注意我们的用词是抑制,你要明白的是即便是差分电路也无法完全规避共模输入干扰对输出的影响,只能尽可能降低影响,所以在差分放大电路中我们仍然需要评估共模输入干扰对输出的影响,那么如何评估呢?相信大家的答案都是基于共模抑制比去评估。

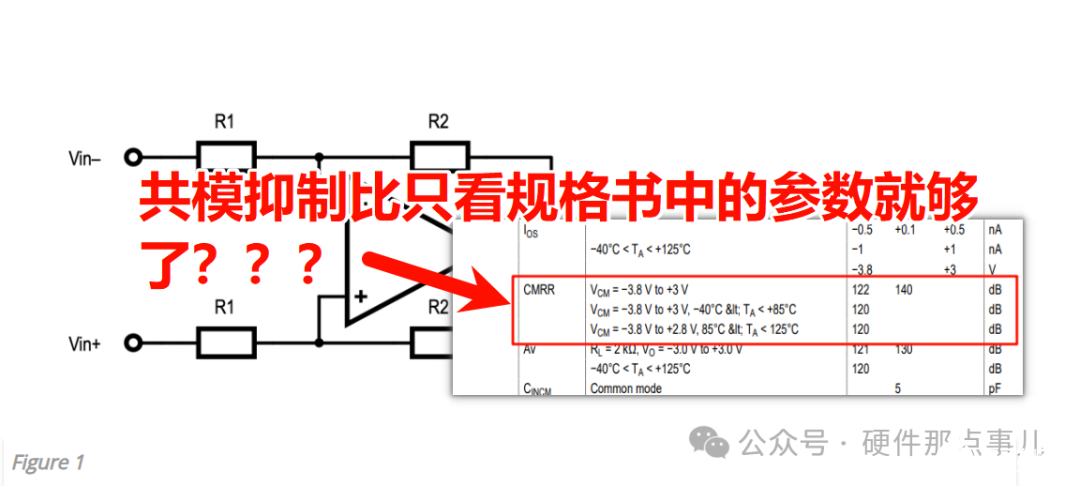

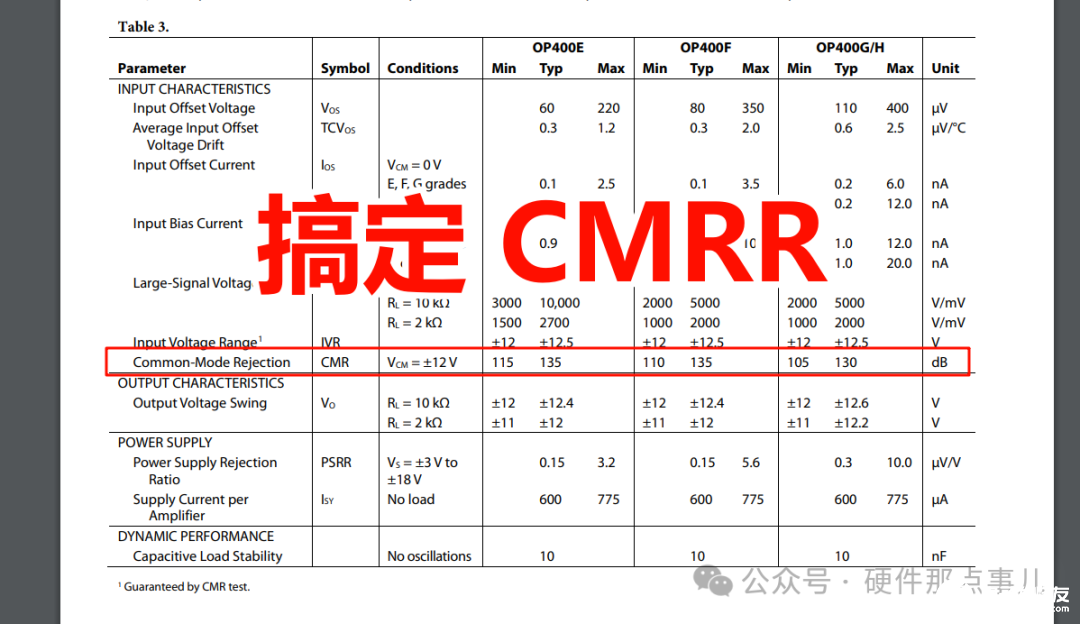

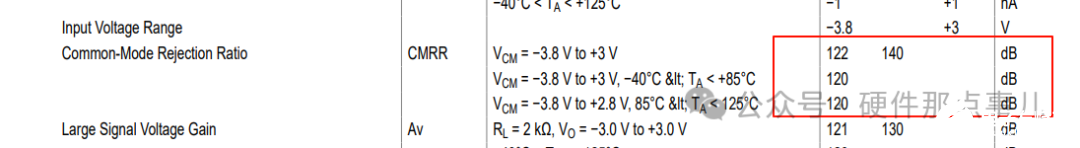

那么问题来了?如何得到差分放大电路的抑制比呢?是不是打开运算放大器的规格书看看规格书中的共模抑制比参数就够了?答案当然没有这么简单。

今天这篇文章我们就介绍一下,如何计算差分电路的共模抑制比,差分电路中有哪些因素会影响共模抑制比?结论可能会让你大吃一惊。

Part 02

差分放大电路的CMRR计算

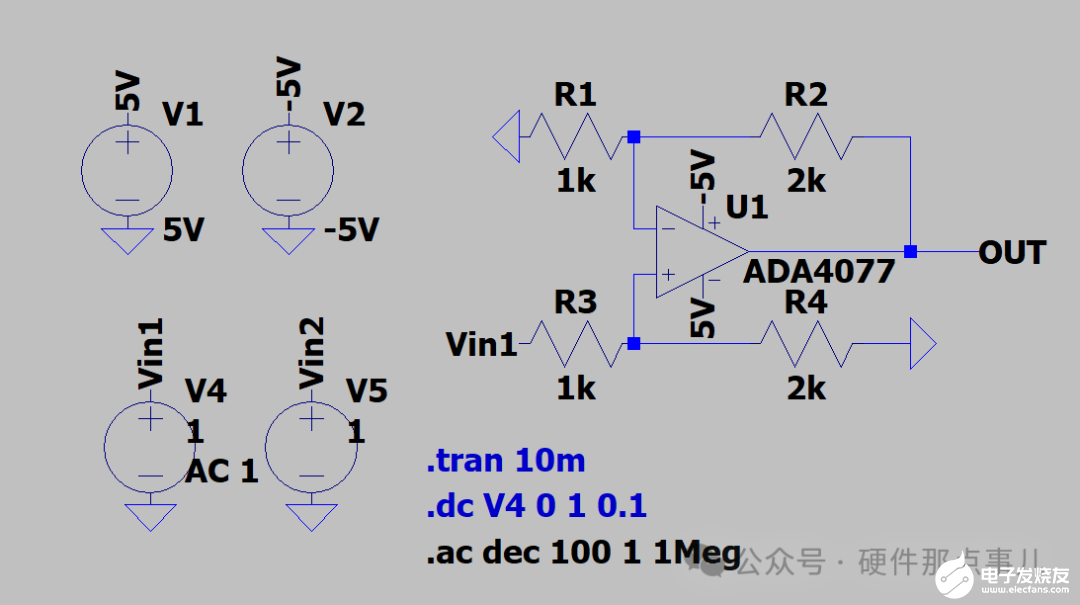

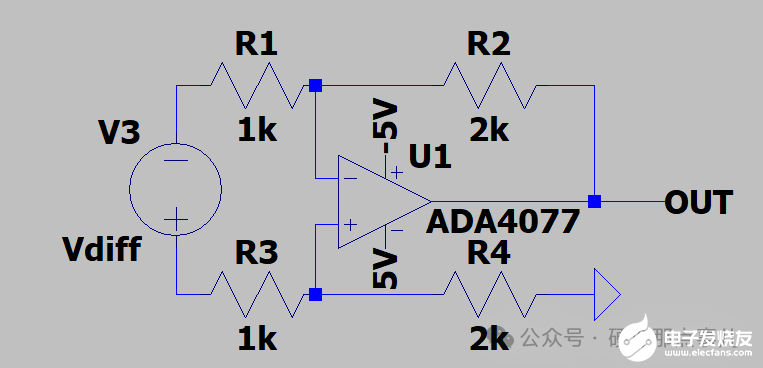

首先我们推导一下差分电路的CMRR,以上一篇文章我们分析的差分放大电路为例:

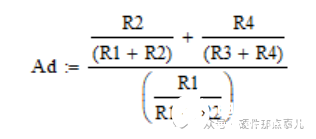

共模抑制比CMRR定义为差模增益Ad与共模增益Acm的比值,所以要想得到差分放大电路的CMRR,我们需要分别计算出差模增益Ad与共模增益Acm才行。 1.差模增益Ad推导 当输入信号为差模信号时,等效电路如下,具体的推导过程可以参考上一篇文章,可以得到Ad: Ad=Vout/Vdiff

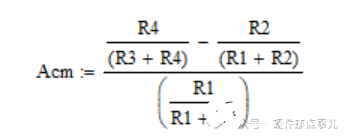

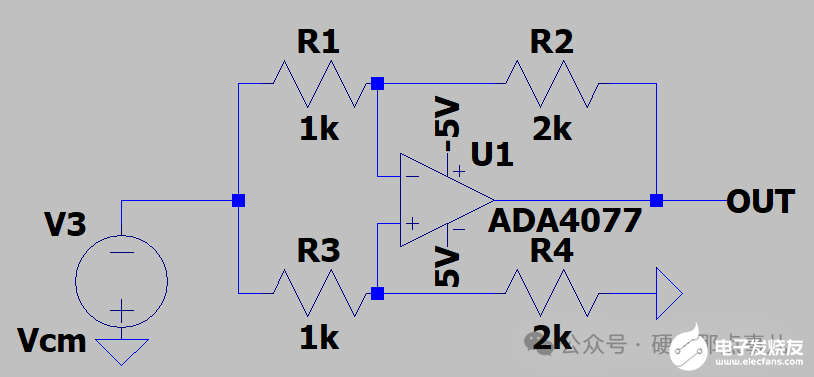

2.共模增益Acm推导: Acm=Vout/Vcm

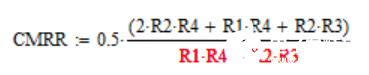

3.CMRR推导: CMRR=Ad/Acm

理想情况下,当R1=R3,R2=R4时,可以看到分母为0,CMRR为无穷大,但是实际的电阻是有误差的,所以即便我们选择的R1=R3,R2=R4,但实际上R1≠R3,R2≠R4,所以CMRR不会是无穷大,那么问题来了,电阻的精度对CMRR的影响有多大呢?

Part 03

电阻精度对CMRR的影响评估

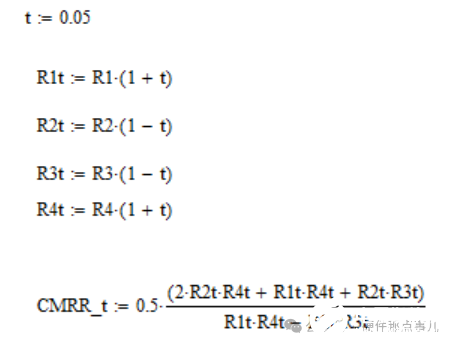

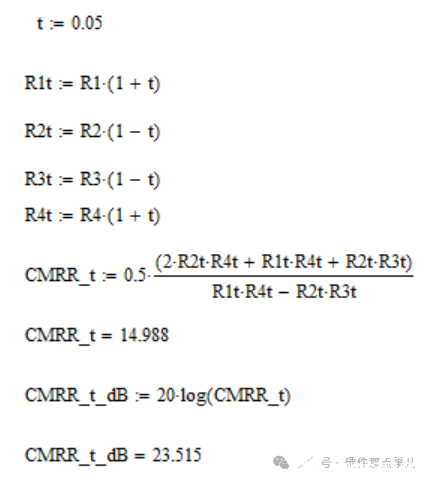

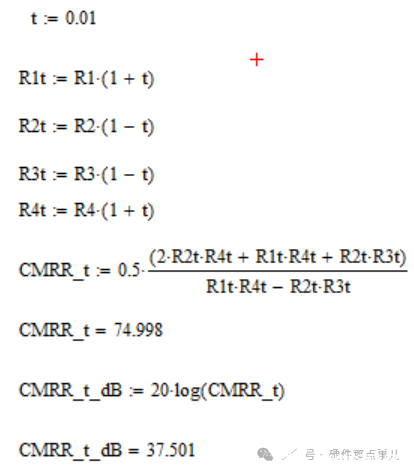

我们假定电阻的精度为t,进而可以推导出考虑电阻偏差后的CMRR:

当电阻精度为5%时,电路的共模抑制比为:23.5dB

当电阻精度为1%时,电路的共模抑制比为:37.5dB

当电阻精度为0.1%时,电路的共模抑制比为:57.5dB

Part 04

总结

通过以上分析可知,差分放大电路的共模抑制比只看运放的规格书是不够的,而是和外围电阻的精度有关,单看规格书中的CMRR可能高达100多dB,但是考虑外围电路的电阻精度后可能只有20多dB,此时共模电压对于输出的精度影响可能就无法忽略了,并且采用5%精度和0.1%精度的电阻对共模抑制比(单位为dB)的影响直接翻倍了。 而输入端偏移:偏移电压=Vcm/CMRR(单位为V/V) CMRR=20dB -> Vcm/Vos=10V/V CMRR=40dB -> Vcm/Vos=100V/V

这意味着采用采用5%精度和0.1%精度的电阻,共模电压在运放输入端产生的偏移电压差了100倍之多,所以设计差分放大电路无比要考虑电阻精度对CMRR的影响。

-

运放

+关注

关注

48文章

1181浏览量

53564 -

硬件

+关注

关注

11文章

3416浏览量

66663 -

共模抑制比

+关注

关注

3文章

82浏览量

16023 -

差分放大电路

+关注

关注

18文章

161浏览量

50154 -

差分电路

+关注

关注

2文章

59浏览量

23539

发布评论请先 登录

相关推荐

硬件面试难题:差分电路的共模抑制比只看运放规格书中的参数就够了吗?

硬件面试难题:差分电路的共模抑制比只看运放规格书中的参数就够了吗?

评论