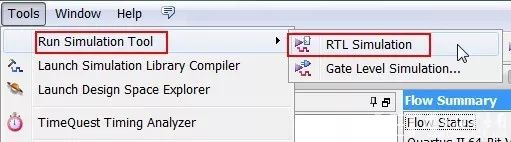

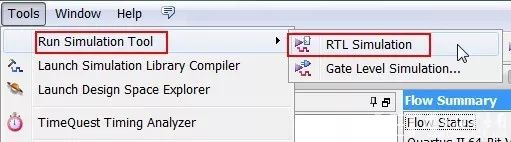

仿真测试的所有准备工作就绪了,下面我们就可以一键完成仿真工作。如图6.18所示,点击菜单栏的“ToolsàRun Simulation ToolàRTL Simulation”。

图6.18 运行仿真菜单

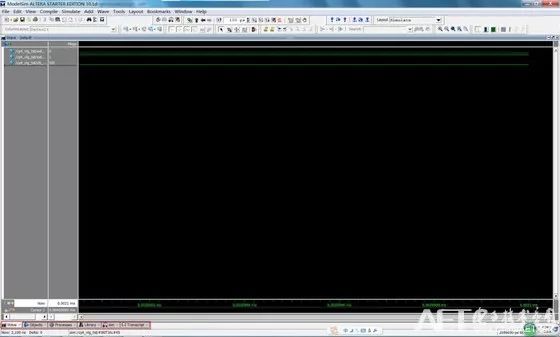

随后ModelSim-Altera便启动,如图6.19所示,这是ModelSim-Altera软件的工作界面。

图6.19 波形界面

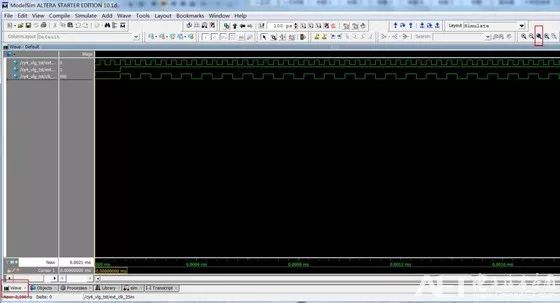

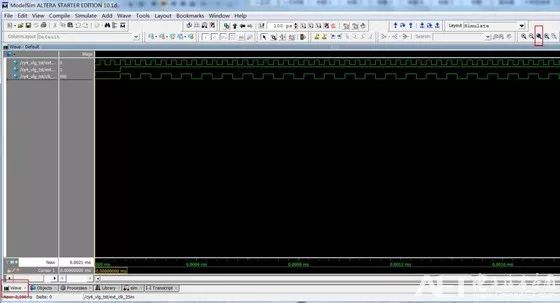

弹出Modelsim后,如图6.20所示,我们可以打开Wave查看,同时点击右上角的“Zoom Full”按钮,整个有效的波形将展开显示。Modelsim的使用并不难,大家要多动手,所有的菜单按钮都简单易懂,有些地方右键菜单也有很多功能,如果这里一一介绍恐怕需要一本书,所以大家自动动手,贵在尝试,很快就会上手。

图6.20 仿真波形

如图6.21所示,这便是我们设计的二分频效果。

图6.21 放大的仿真波形

怎么样,通过这个简单的工程,大家是不是掌握了使用Quartus II进行工程创建、设计文本创建和编辑、测试脚本创建和编辑、使用Modelsim进行仿真等基本的技能。当然了,这只是刚刚把您领进门,让您熟悉一下工具的一些基本操作。这个例程就到这里,我们不往下进行板级的实验,大家继续跟着教程往下,该掌握的都会掌握滴。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:【精彩博文】基于仿真的第一个工程实例之调用Modelsim仿真

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

相关推荐

云的官方网站,这个背后就是域名解析的过程。 域名解析换一种说法就是把域名转换为IP地址。当我们对一个网站进行访问的时候,实际上就是与一个IP地址通信,但一般来说所有的IP地址都是一串数字,v4还好,v6的字符会更长,所以我们才会

![的头像]() 发表于

发表于 11-22 10:12

•204次阅读

仿真对于FPGA设计来说至关重要,我们经常使用modelsim来进行功能仿真或者时序仿真,这样就需要将m

![的头像]() 发表于

发表于 10-24 18:15

•316次阅读

今天给大侠带来在FPGA设计应用中如何在ModelSim中添加Xilinx仿真库,话不多说,上货。

注意:ModelSim一定要安装在不带空格的目录下,即不要安装在“Program

发表于 07-03 18:16

的LMP进行解析,带大家一起了解LMP的工作原理。 1 什么是LMP? LMP是 controller中的一层,用于控制和协商两个设备之间蓝牙连接的所有操作,这包括了逻辑传输和逻辑链路的建立和控制,以及物理链路的控制,比如蓝牙连

![的头像]() 发表于

发表于 06-12 09:01

•2161次阅读

在编写完HDL代码后,往往需要通过仿真软件Modelsim或者Vivadao自带的仿真功能对HDL代码功能进行验证,此时我们需要编写Testbench文件对HDL功能

发表于 04-29 10:43

•2151次阅读

Multisim(是美国国家仪器有限公司推出的仿真工具)的工作原理主要基于电路元件的建模与仿真分析。

![的头像]() 发表于

发表于 03-29 15:24

•1374次阅读

Simulink是MATLAB的一个模块,它采用图形化的方式来创建动态系统模型并进行仿真分析。Simulink的工作原理主要基于模块化的建模和仿真方式。

![的头像]() 发表于

发表于 03-29 15:21

•1791次阅读

在两者之间即可,然后保存。

第三步,打开ISE,在菜单Edit-Preferences…,调出设置窗口。

设置好之后就到了最后一步,在新建工程时,选择对应的modelsim即可,在看仿真时正常打开就行了。

发表于 03-22 18:55

Quartus II建立工程时,设置 modelsim 作为仿真软件,或者是在Assignments——>EDA Tool Settings进行设置。

三、 Modelsim

发表于 03-19 16:40

首先,你需要选择一个FPGA仿真软件,如ModelSim、Vivado、Quartus II等。这些软件都提供了强大的仿真功能,可以帮助你验证FPGA设计的正确性。

![的头像]() 发表于

发表于 03-15 14:00

•840次阅读

后仿真也称为时序仿真或者布局布线后仿真,是指电路已经映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,是否存在时序违规。

![的头像]() 发表于

发表于 03-06 09:58

•9470次阅读

的界面点击Finish后,会自动进入ModelSim软件中进行模块仿真。在仿真界面中,可以将模块的输入输出添加到监视界面,便于进行模块的程序

发表于 02-29 08:25

在使用紫光同创PDS和Modelsim联合仿真时,modelsim报错不会解决,如下图

发表于 02-18 10:26

#2024,为FPGA生态加油,为FPGA社区点赞#...使用IP核时如何进行modelsim仿真

发表于 02-02 20:22

ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程 序进行仿真,支持IEEE常见的各种硬件描述语言标准。可以

发表于 01-14 09:47

•0次下载

图文解析使用Modelsim进行仿真工作

图文解析使用Modelsim进行仿真工作

评论