电子行业的工程师经常会遇到阻抗匹配问题。什么是阻抗匹配?为什么要进行阻抗匹配?本文带您一探究竟!

一、什么是阻抗

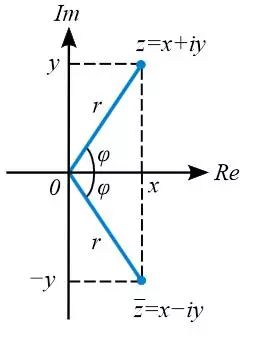

在电学中,常把对电路中电流所起的阻碍作用叫做阻抗。阻抗单位为欧姆,常用Z表示,是一个复数Z= R+i( ωL–1/(ωC))。具体说来阻抗可分为两个部分,电阻(实部)和电抗(虚部)。其中电抗又包括容抗和感抗,由电容引起的电流阻碍称为容抗,由电感引起的电流阻碍称为感抗。

图1 复数表示方法

二、阻抗匹配的重要性

阻抗匹配是指信号源或者传输线跟负载之间达到一种适合的搭配。阻抗匹配主要有两点作用,调整负载功率和抑制信号反射。

1、调整负载功率

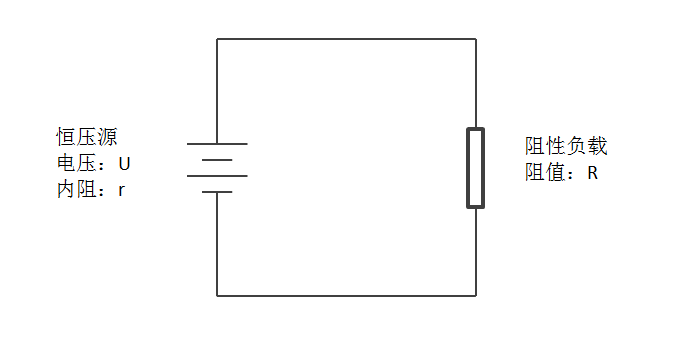

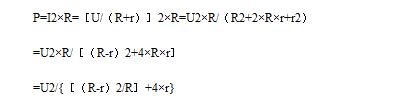

假定激励源已定,那么负载的功率由两者的阻抗匹配度决定。对于一个理想化的纯电阻电路或者低频电路,由电感、电容引起的电抗值基本可以忽略,此时电路的阻抗来源主要为电阻。如图2所示,电路中电流I=U/(r+R),负载功率P=I*I*R。由以上两个方程可得当R=r时P取得最大值,Pmax=U*U/(4*r)。

图2 负载功率调整

2、抑制信号反射

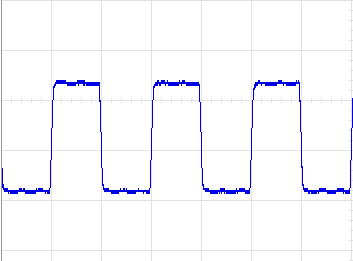

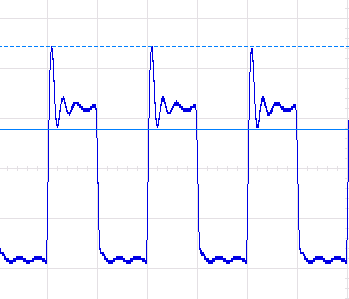

当一束光从空气射向水中时会发生反射,这是因为光和水的光导特性不同。同样,当信号传输中如果传输线上发生特性阻抗突变也会发生反射。波长与频率成反比,低频信号的波长远远大于传输线的长度,因此一般不用考虑反射问题。高频领域,当信号的波长与传输线长出于相同量级时反射的信号易与原信号混叠,影响信号质量。通过阻抗匹配可有效减少、消除高频信号反射。

图3 正常信号

图4 异常信号(反射引起超调)

三、阻抗匹配的方法

阻抗匹配的方法主要有两个,一是改变组抗力,二是调整传输线。

改变阻抗力就是通过电容、电感与负载的串并联调整负载阻抗值,以达到源和负载阻抗匹配。

调整传输线是加长源和负载间的距离,配合电容和电感把阻抗力调整为零。此时信号不会发生发射,能量都能被负载吸收。高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆。一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线(差分)为85-100欧姆。

四、阻抗匹配的应用

1、功放与音箱

无论是定阻抗式还是定电压式输出的功放,只有喇叭的总功率和功放的总功率相等时才能得到最佳的工作状态。音箱系统若要完全达到匹配是非常困难的,它的音频成分总是在不停的变化,好在音箱系统对阻抗匹配度要求并不高。最常见到的喇叭阻抗的标示值是8欧姆,它表示当输入1KHz的正弦波信号,它呈现的阻抗值是八欧姆;或者是在喇叭的工作频率响应范围内,平均阻抗为8欧姆。

图5 音箱

2、PCB走线

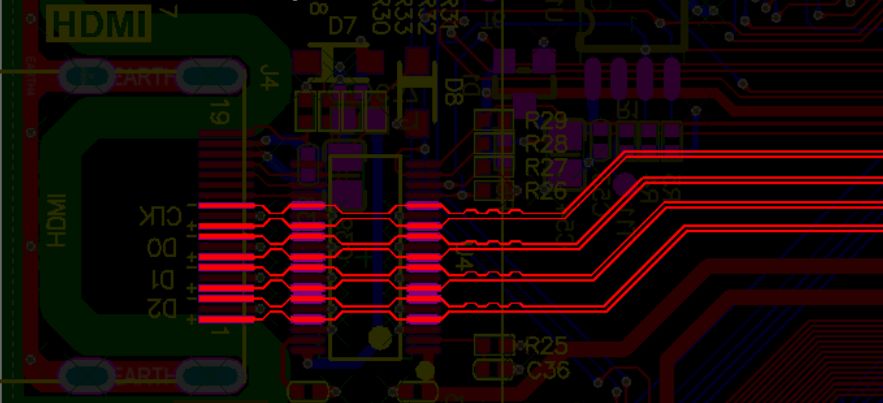

高频领域中,信号频率对PCB走线的阻抗值影响非常大。一般来说当数字信号边沿时间小于1ns或者模拟信号频率超过300M时就要考虑阻抗问题。PCB走线阻抗主要来自寄生的电容、电阻、电感系数,主要因素有材料介电常数、线宽、线厚乃至焊盘的厚度等。PCB 阻抗的范围是 25 至120 欧姆,USB、 LVDS、 HDMI、 SATA等一般要做85-100欧姆阻抗控制。

图6 走线匹配阻抗

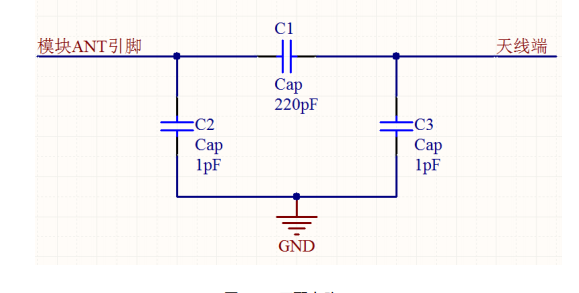

3、天线设计

研究天线阻抗的主要目的是为实现天线和馈线间的匹配。发射信号时应使发射天线与馈线的特性阻抗相等,以获得最好的信号增益。接收信号时天线与负载应做共轭匹配,接收机(负载)阻抗一般认为只有实数部分,因此需要用匹配网络来除去天线的电抗部分并使它们的电阻部分相等。图7为天线阻抗匹配时常用的π型网络,使用网络分析仪测量阻抗以确定 C1、C2、C3 的取值,完成阻抗匹配。

图7 π型电路

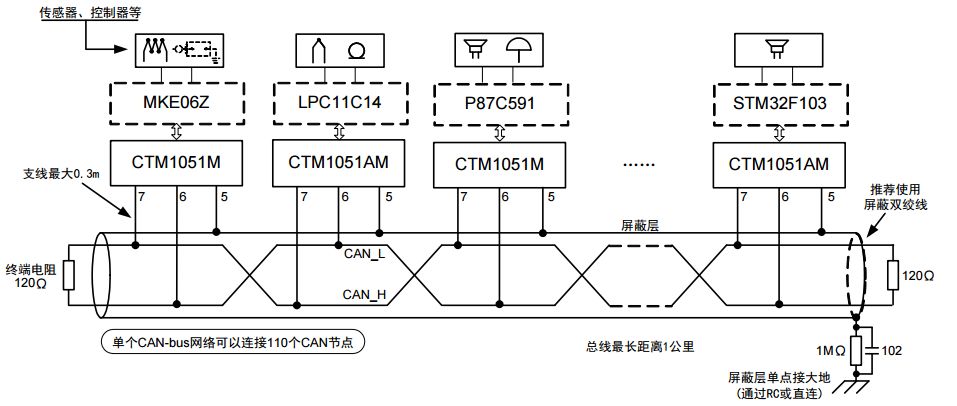

4、终端匹配电阻

在设计CAN总线、485总线时常需要在差分线两端加终端电阻(匹配电阻),以减少由特性阻抗突变造成的信号反射。如下图CAN总线网络,双绞线特性阻抗为120欧姆,若不加终端电阻两端直接悬空,空气的特性阻抗为无穷大。此时,极易出现图4所示的信号反射。

图8 CAN总线网络

对于CAN总线来说,由于收发器对信号电平判断的采样点位置普遍靠后,因此信号反射一般不会影响通信错误率。反射会影响产品的EMI特性,最直接的表现就是眼图实验效果差,存在两个异常凸起。

图9 CAN总线眼图

致远电子的 M6G2C-256LI 核心板,主要器件由 MPU、 DDR、 Flash、 power 四部分构成,看似简单的架构又是如何保证核心板的稳定性呢?差分蛇形走线、等长控制、阻抗匹配、 PCB 分层设计、高速信号参考地等设计来保证产品的设计合理性,再配合信号完整性、信号眼图、信号脉冲等等仪器测试为产品稳定性保驾护航。

图10 M6G2C-256LI工业级核心板

-

阻抗匹配

+关注

关注

14文章

355浏览量

31023 -

容抗

+关注

关注

0文章

16浏览量

10137 -

感抗

+关注

关注

0文章

12浏览量

8763

原文标题:为什么要阻抗匹配?

文章出处:【微信号:ZLG_zhiyuan,微信公众号:ZLG致远电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

浅析阻抗匹配及其应用

PCB阻抗匹配的方法

阻抗匹配总结

深度剖析阻抗匹配

怎样理解阻抗匹配_pcb阻抗匹配如何计算

深度剖析阻抗匹配

深度剖析阻抗匹配

评论