Cadence Allegro系统互连平台能够跨集成电路、封装和PCB协同设计高性能互连。应用平台的协同设计方法,工程师可以迅速优化I/O缓冲器之间和跨集成电路、封装和PCB的系统互联。该方法能避免硬件返工并降低硬件成本和缩短设计周期。约束驱动的Allegro流程包括高级功能用于设计捕捉、信号完整性和物理实现。由于它还得到Cadence Encounter与Virtuoso平台的支持,Allegro协同设计方法使得高效的设计链协同成为现实。

工程师的巨大福利,首款P_C_B分析软件,点击免费领取

allegro快速设置栅格点方法

第一步:

新建文档:xxxxx.txt 写入代码:

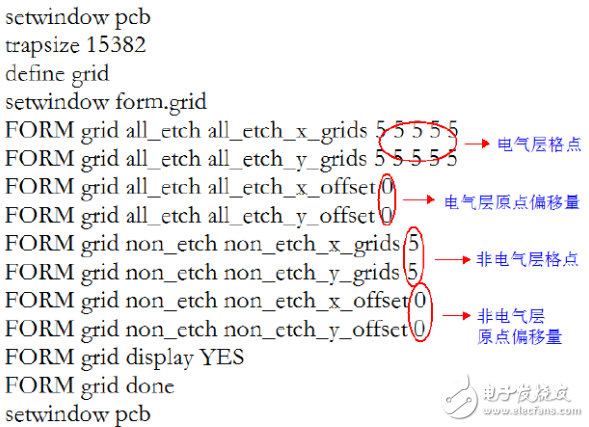

setwindow pcb

trapsize 15382

define grid

setwindow form.grid

FORM grid all_etch all_etch_x_grids 5 5 5 5 5

FORM grid all_etch all_etch_y_grids 5 5 5 5 5

FORM grid all_etch all_etch_x_offset 0

FORM grid all_etch all_etch_y_offset 0

FORM grid non_etch non_etch_x_grids 5

FORM grid non_etch non_etch_y_grids 5

FORM grid non_etch non_etch_x_offset 0

FORM grid non_etch non_etch_y_offset 0

FORM grid display YES

FORM grid done

setwindow pcb

第二步:

将txt文档保存为逻辑文件:xxxxx.lgc

第三步:

在env文件中写入调用命令:

alias ~2 replay xxxxx.lgc

第四步:

将xxxxx.lgc文件放入brd文件目录下

第五步:

按Ctrl+2键使用快捷方式实现格点切换

注:

上述格点及切换格点快捷键可根据自己习惯任意设置!

-

pcb

+关注

关注

4420文章

24022浏览量

426966 -

Cadence

+关注

关注

68文章

1039浏览量

147469 -

PCB设计

+关注

关注

396文章

4944浏览量

96028 -

allegro

+关注

关注

42文章

775浏览量

150669 -

可制造性设计

+关注

关注

10文章

2066浏览量

16544 -

华秋DFM

+关注

关注

20文章

3516浏览量

6612

发布评论请先 登录

Allegro Skill布局功能之快速切换格点介绍

Protel封装库转换到Allegro的方法及步骤

Protel到Allegro格式转换方法及步骤

Allegro生成钻孔文件的步骤

DXP设置PCB板中背景栅格的两种方法

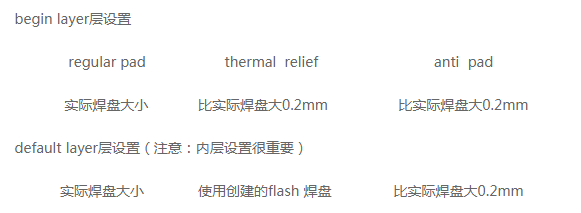

allegro建立焊盘的方法和操作步骤

allegro快速设置栅格点方法步骤介绍

allegro快速设置栅格点方法步骤介绍

评论