时钟芯片的测试工作需细致入微,涵盖从时钟生成过程到芯片内部关键模块的全面评估。其核心功能在于产生稳定且准确的频率输出,并能根据系统需求灵活调整。因此,测试的重点在于验证芯片内部各个环节的稳定性和精确性。

时钟生成机制解析:时钟芯片的生成过程可类比为精密调控的水流灌溉系统。外部输入的参考时钟作为“水源”,进入芯片后,通过多个相位锁定环(PLL)模块进行频率的倍频或分频,最终输出多种频率的时钟信号。测试中,需确保PLL模块的锁定性能和稳定性,以及倍频、分频后的频率准确性。

相位与频率调控机制:相位鉴频器(PFD)如同“流量计”,负责检测输入时钟与反馈时钟间的相位差异。任何微小的相位偏差都可能导致输出时钟的不准确。PFD将相位差传递给电荷泵,电荷泵再与低通滤波器协同工作,将相位差转换为控制电压信号,以稳定VCO的输出频率。测试需验证PFD能否精确捕捉相位差,以及电荷泵和滤波器能否稳定生成相应的控制信号。

压控振荡器(VCO)的验证:VCO如同“可调水流速的水泵”,根据输入电压生成对应频率的信号。测试中,需验证VCO能否根据不同控制电压产生所需频率,并关注其输出的相位噪声和频率抖动,这些参数直接影响系统的精度和稳定性。

分频与输出端口评估:时钟芯片将高频信号通过分频器降低至所需频率,再通过输出端口提供给系统。测试中,需确认分频器的准确性及输出端口的信号质量,包括占空比、上升/下降时间及抖动等。

综合测试内容:为确保时钟芯片的稳定性和准确性,测试内容涵盖以下方面:

DC测试:验证芯片各节点的电平,确保电路工作在设计的电平范围内。

频率输出验证:在PLL闭环和开环状态下,确认输出频率的准确性。

动态响应测试:在不同负载和温度条件下,测试芯片的响应,确保输出频率稳定。

功耗测量:测量芯片的静态和动态功耗,确保其符合设计要求。

综上所述,时钟芯片的测试流程既严谨又复杂,需全面关注信号在芯片内部的流转过程,确保每一步都在设计范围内。通过系统化的测试流程,可确保时钟芯片在各种应用场景下提供准确、稳定的频率输出。

-

芯片

+关注

关注

455文章

50714浏览量

423154 -

测试

+关注

关注

8文章

5269浏览量

126599 -

时钟

+关注

关注

10文章

1733浏览量

131451

发布评论请先 登录

相关推荐

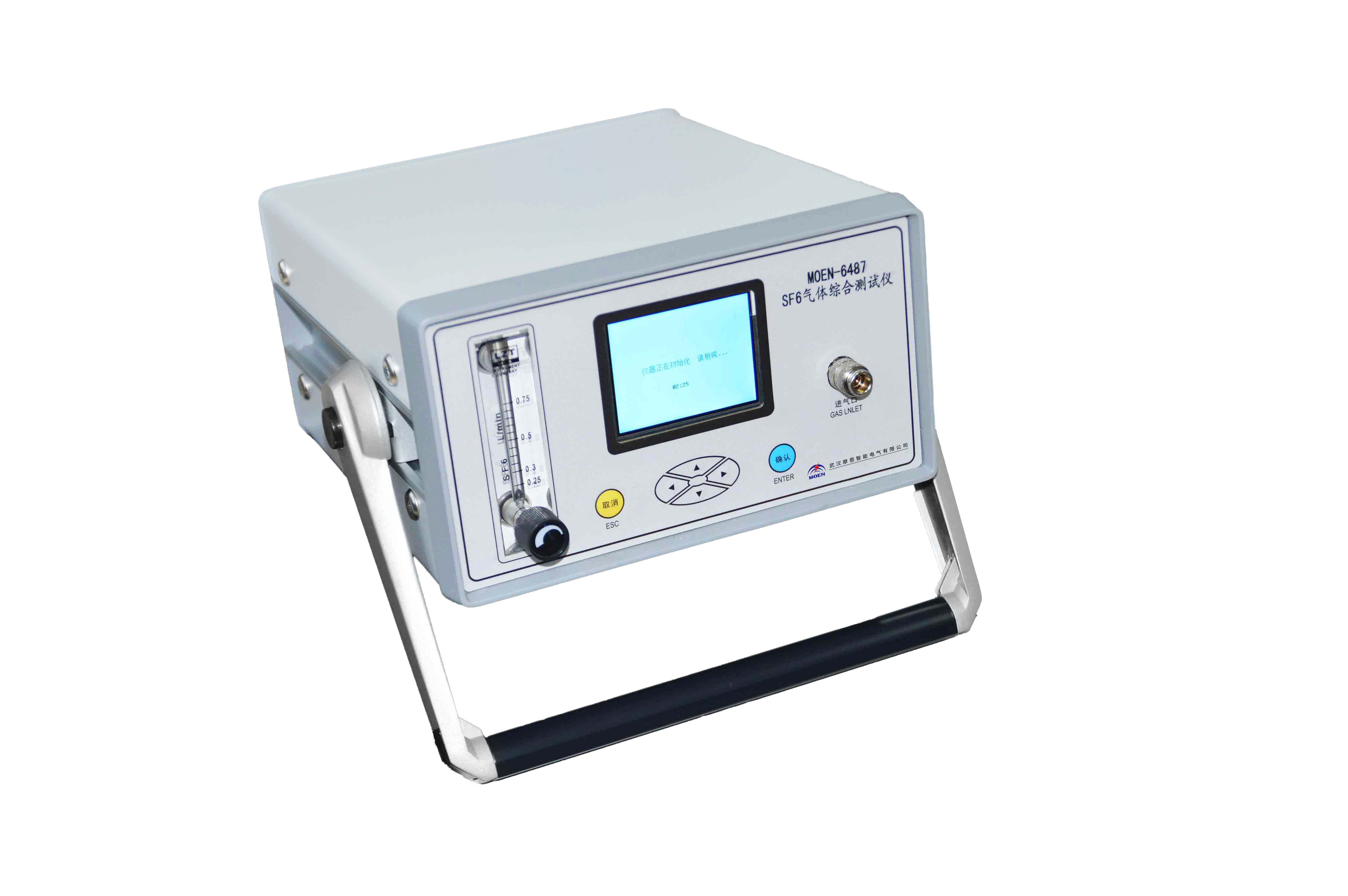

直流充电桩(机)综合测试仪:确保直流充电桩高效安全运行的关键设备

艾法斯 Aeroflex 3920 综合测试仪

4957系列射频微波综合测试仪

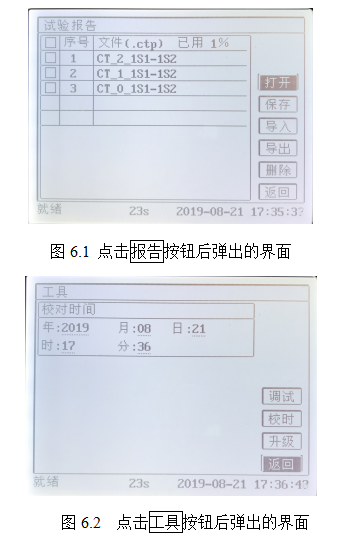

SF6综合测试仪操作步骤——每日了解电力知识

SF6气体综合测试仪如何测量——每日了解电力知识

计量装置综合测试系统的接线方式——每日了解电力知识

互感器综合测试仪的按钮功能——每日了解电力知识

EV4000新能源汽车动力系统综合测试仪

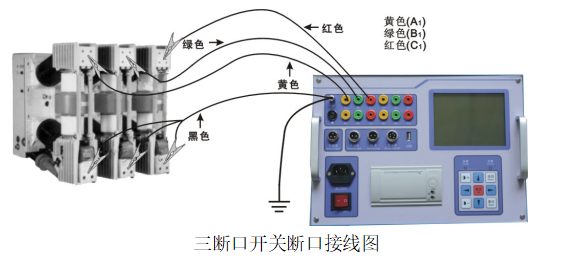

开关特性回路电阻综合测试仪接线操作——每日了解电力知识

无线电综合测试仪

光伏逆变器综合测试仪是什么

精密力学检测设备 | 美能电池片拉脱力综合测试仪

时钟芯片综合测试策略:从生成过程到关键模块

时钟芯片综合测试策略:从生成过程到关键模块

评论