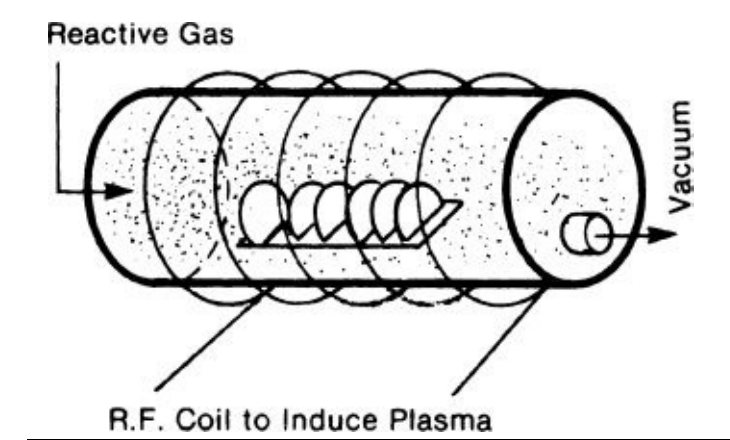

等离子体蚀刻机需要与湿法蚀刻相同的元素:化学蚀刻剂和能量源。从物理上讲,等离子体蚀刻机由室、真空系统、气体供应、终点检测器和电源组成(如下图所示)。晶圆被装入室中,室内的压力被真空系统降低。真空建立后,室中充满反应气体。对于硅二氧化物的蚀刻,气体通常是与氧气混合的CF4。电源在室内的电极上产生射频(RF)场。该领域激发气体混合物进入等离子体态。在激发状态下,氟攻击硅二氧化物,将其转化为挥发性成分,由真空系统从系统中移除。

平面等离子体蚀刻

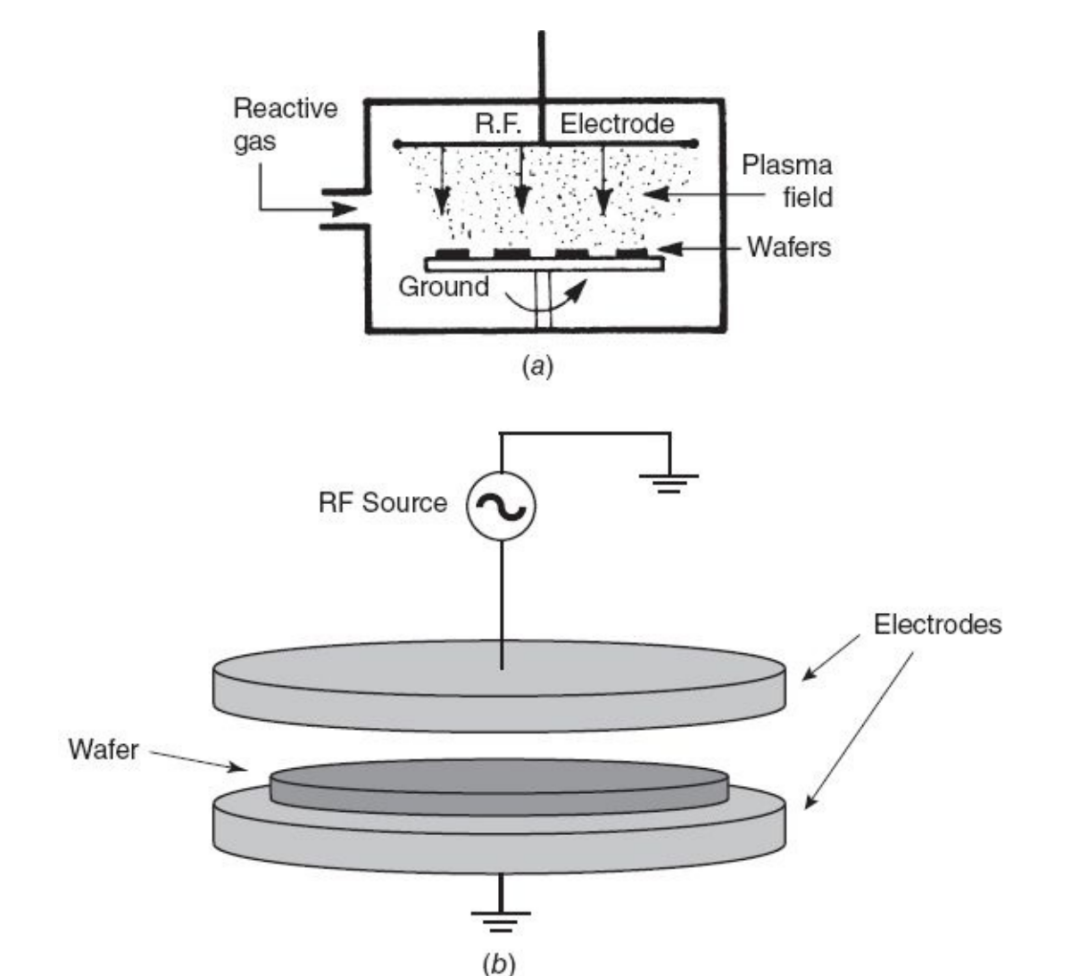

对于更精确的蚀刻,使用平面等离子体系统。这些系统包含桶系统的基本信息,但晶圆放置在RF电极下的接地托盘上(如下图所示)。蚀刻是在晶圆实际上在等离子体场中进行的。蚀刻离子比桶系统中的离子更具方向性,导致更各向异性的蚀刻。几乎垂直的侧壁可以通过等离子体蚀刻实现。通过在系统中旋转晶圆托盘来增加蚀刻均匀性。

平面等离子体蚀刻系统设计为批量和单晶圆室配置。单晶圆系统因其能够紧密控制蚀刻参数以实现均匀蚀刻而受欢迎。此外,带有装载锁室的单晶圆系统可以保持高生产率,并且适合基于轨道的联机自动化。

RF产生的平行板等离子体源正在让位于0.35微米处理的新来源。

正在考虑的高密度、低压力等离子体源包括电子回旋共振(ECR)、高密度反射电子、螺旋波、感应耦合等离子体(ICP)和变压器耦合等离子体(TCP)。

干法蚀刻的优劣包括:蚀刻速率、辐射损伤、选择性、颗粒产生、蚀刻后腐蚀和所有权成本。

蚀刻速率

等离子体系统的蚀刻速率由许多因素决定。系统设计和化学是其中两个。其他是离子密度和系统压力。离子密度(离子数/立方厘米)是供电量到电极的函数。(电源配置在后面章节中描述。)增加功率会产生更多离子,进而增加蚀刻速率。离子密度类似于增加液体化学蚀刻溶液的强度。离子密度在3×10^10到3×10^12范围内。

系统压力通过称为平均自由路径的现象影响蚀刻速率和均匀性。这是气体原子或分子在与另一粒子碰撞之前平均会行进的距离。在较高压力下,有许多碰撞使粒子具有许多方向,这反过来会导致边缘轮廓控制的丧失。低压力更受欢迎,但存在与等离子体损伤的权衡,如下所述。系统压力通常在0.4到50毫托的范围内。

蚀刻速率在600到2000埃/分钟之间变化。

辐射损伤

似乎高密度源与低压力是首选的系统设计。然而,存在对晶圆的辐射或等离子体损伤的相反过程。等离子体场内存在能量原子、自由基、离子、电子和光子。

这些物种,根据它们的浓度和能量水平,会在半导体中引起各种损伤。损伤包括表面泄漏、电气参数变化、膜层退化(尤其是氧化物)以及对硅的损伤等。有两种损伤机制。一种是简单地过度暴露于等离子体中的高能物种。另一种是介电损耗,来自在蚀刻周期中跨介电材料流动的电流。

-

半导体

+关注

关注

334文章

27382浏览量

218967 -

等离子体

+关注

关注

0文章

122浏览量

14229 -

蚀刻机

+关注

关注

0文章

24浏览量

3419

原文标题:半导体工艺之从显影到最终检查(九)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

光刻工艺的基本步骤

简述半导体超纯水设备工艺流程及标准参考分析

PCB蚀刻工艺原理_pcb蚀刻工艺流程详解

功率半导体分立器件工艺流程

半导体图案化工艺流程之刻蚀(一)

什么是光刻工艺?光刻的基本原理

光刻工艺的基本知识

半导体光刻工艺流程分析

半导体光刻工艺流程分析

评论