以下文章来源于ICPMS冷知识,作者gz07apple

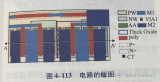

集成电路(IC)是由数亿甚至数十亿个晶体管组成,这些晶体管在硅晶圆上并行工作。但是这些晶体管若不能相互导通,它们就不能实现指定功能。而这些金属互连(Metal Interconnect)电路像是血管,确保电子信号在不同组件之间的顺利传输。金属互连中介质层(Dielectric layer)的作用,是防止不同金属层间的电子迁移,将不同金属层相互隔离,避免物质之间的扩散或渗透等。

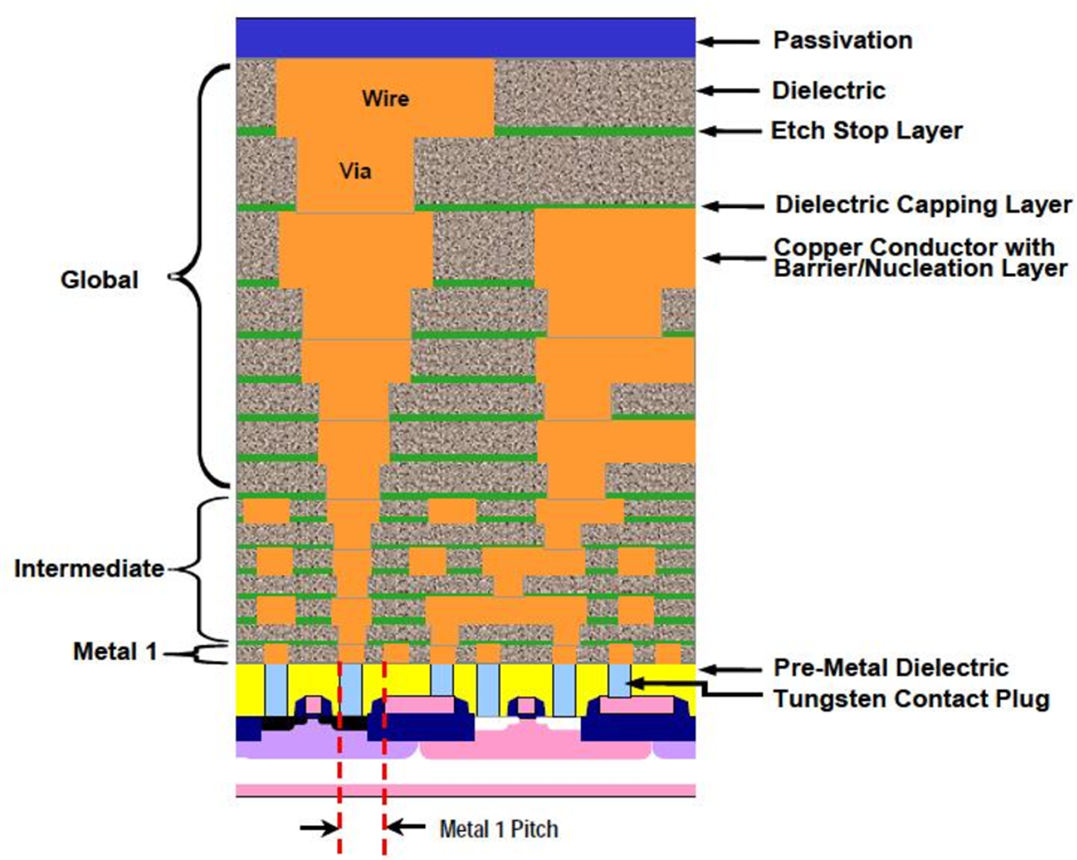

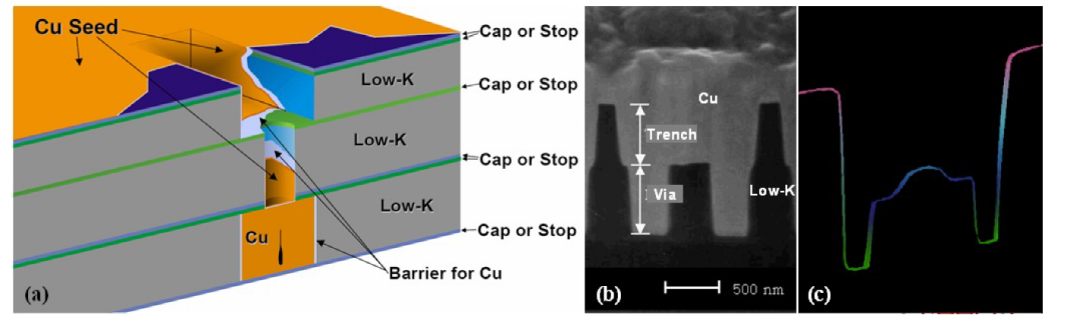

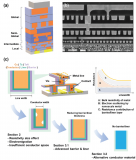

先来看一张金属互连剖面图:

一、金属前介质层

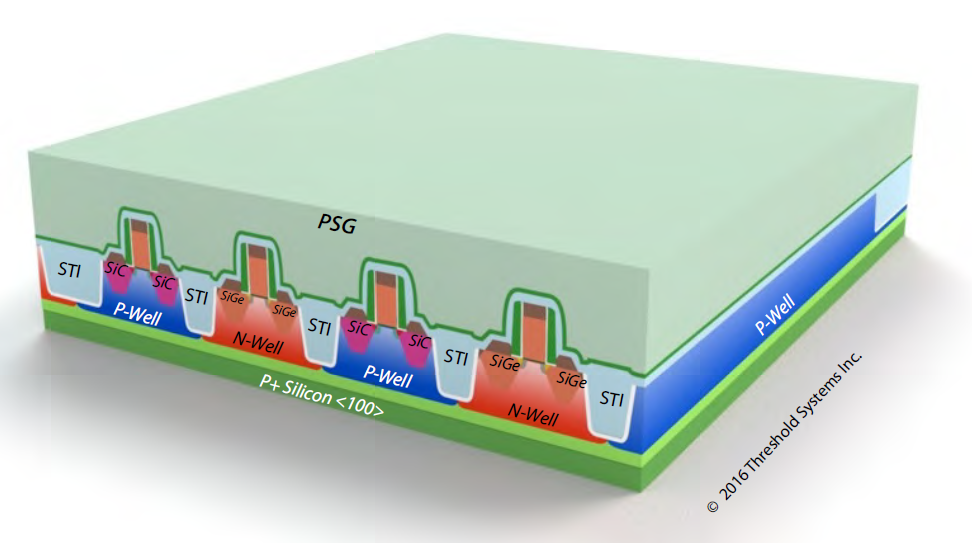

剖面图中黄色区域为金属前介质层,即PMD(Pre-MetalDielectric)。它位于衬底与第一金属层(Metal 1)之间,是保护有源区免受杂质粒子污染的绝缘介质层,其沉积效果的好坏直接影响器件的性能。

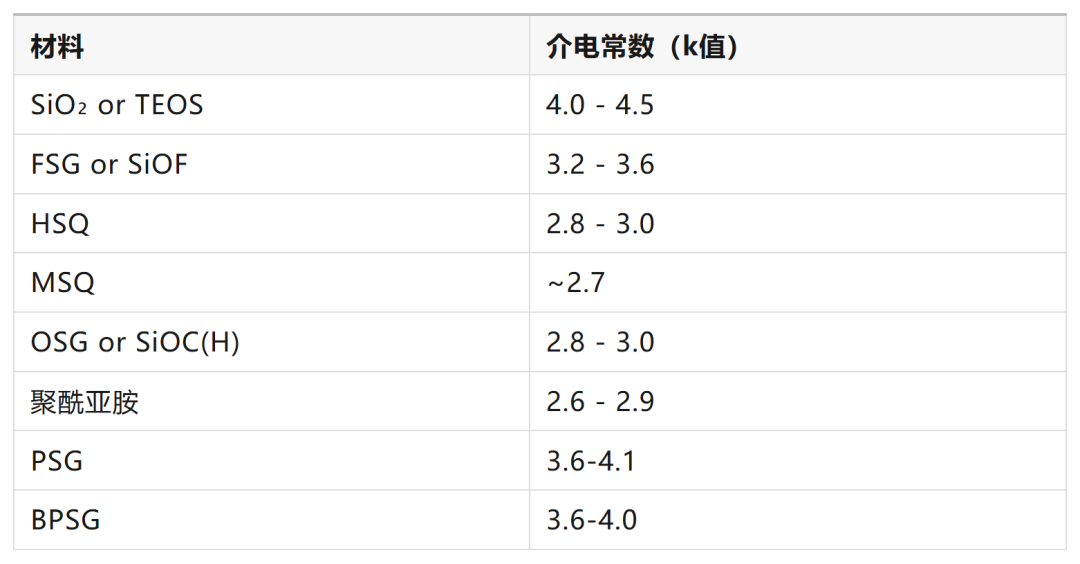

随着半导体器件尺寸的逐渐减小,沉积金属前介质层时所要填充的线缝宽度也越来越小,深宽比越来越大,填孔能力成为沉积工艺优化的首要目标。工艺通常选择TEOS(正硅酸乙酯)、PSG(磷硅玻璃)或BPSG(硼磷硅玻璃)等材料进行填充,利用高密度等离子体化学气相沉积(HDPCVD)或次大气压化学气相沉积(SACVD)工艺来制备金属前介质层。

二、金属间介质层

剖面图中灰色区域为金属间介质层,即IMD(Inter MetalDielectric)。注意,无论金属前介质层还是金属间介质层,都属于层间介质层,即ILD(Inter Layer Dielectric)。两者区分在于,金属前介质层位于衬底和第一层金属之间,而金属间介质层则是位于两层金属之间。

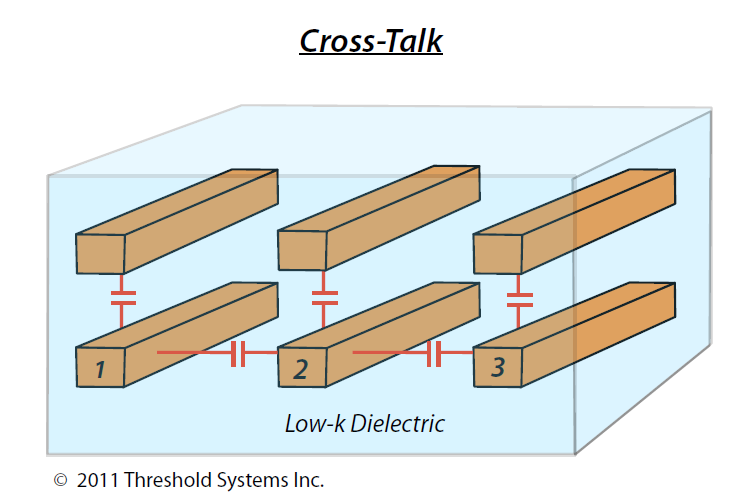

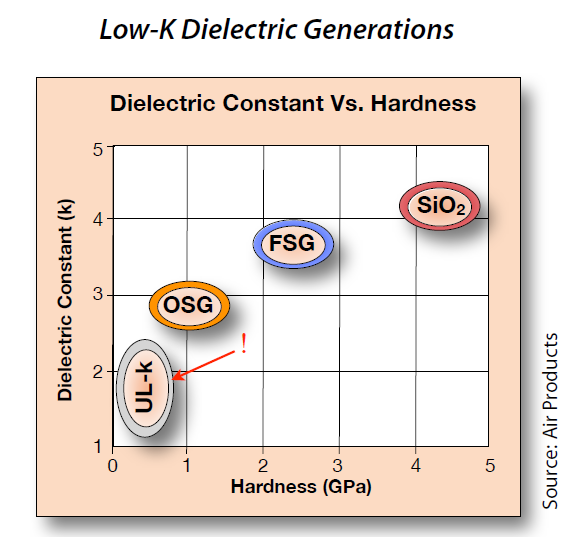

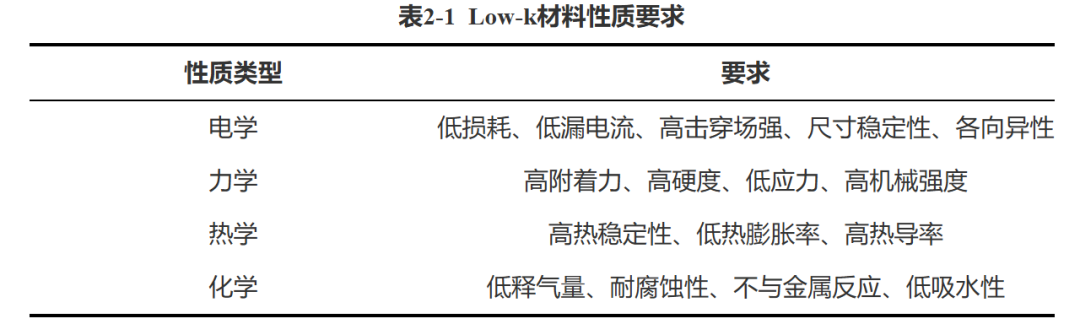

金属间介质层能够确保每个金属互联结构的相互独立,防止串扰(Cross-Talk)。工艺通常选择采用二氧化硅或其它低 k 材料,如FSG(氟硅玻璃)、OSG(有机硅玻璃)等进行填充。比如将硅基前驱体OMCTS(八甲基环四硅氧烷)送入等离子体增强化学气相沉积(PECVD)反应腔,与氧气反应制备SiCO(H)低 k 材料薄膜。

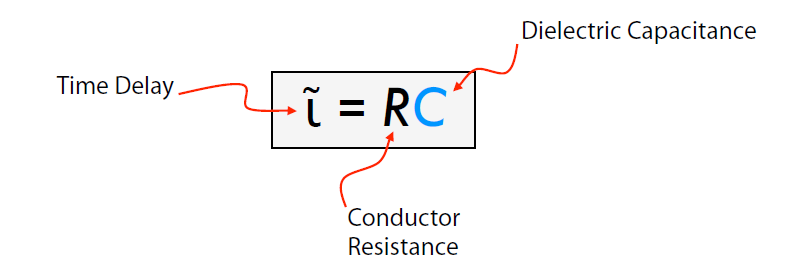

电路导线电阻用R表示,寄生电容用C表示,由于R与导体的横截面积呈反比,C与电容极板的距离呈反比,因此随着制程微缩,布线之间的距离减小,电容与电阻均变大,产生RC延迟造成信号失真,影响芯片工作速度。

降低R与C,R=ρL/S,ρ是电阻率,L是导线长度,S是横截面积,由于增大导体横截面积不利于制程微缩,因此降低R的办法是选取电阻率更低的导体,比如用铜替换铝,然而在采用铜布线之后,短时间很难选择其他导体完全取代铜来继续降低电阻。

C=kA/d,A是横截面积,d是介质层厚度,降低横截面积会导致电阻R增加,增加介质层厚度会导致间隙填充更加困难,因此降低C的办法通常是降低k值,采用低k 材料替代SiO2。低k材料的工艺壁垒在于保证薄膜较薄同时实现足够的机械强度、高均匀性等。

三、刻蚀停止层

铜互连工艺需采用大马士革结构与化学机械抛光(CMP)技术,通过刻蚀低k材料获得沟槽和通孔来完成双大马士革图形化工艺。为了对RC延迟的影响缩至最小,除了前面提到金属间介质层采用低 k 材料外,刻蚀停止层(Etch Stop Layer,ESL)材料的k 值也应尽可能的低,从而降低金属互连的整体介电常数值。刻蚀停止层还可作为其下方金属导线的覆盖层(Capping Layer),也是金属扩散的阻挡层(Barrier Layer)。

过去刻蚀停止层材料通常选择Si3N4(k值约为7~8),其厚度必须尽可能薄。近年来也有采用SiCN(k值约为4~5)作为刻蚀停止层。SiCN(硅碳氮)是兼具宽禁带半导体SiC和绝缘体Si3N4两者优点的新型材料,不仅具有高热导率、高热稳定性、抗压、抗辐射等特点,而且表面致密,对硅和二氧化硅都具有很好的附着性。SiCN薄膜通常使用 4MS(四甲基硅烷)作为硅源、氨气作为氮源,通过 PECVD 工艺制备。

-

集成电路

+关注

关注

5391文章

11618浏览量

363041 -

半导体

+关注

关注

334文章

27693浏览量

222268 -

晶体管

+关注

关注

77文章

9744浏览量

138827

原文标题:【推荐】一文了解金属互连中介质层

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

互连中的信号畸变(信号完整性揭秘)

光互连技术发展面临的难点

【我是电子发烧友】了解以太网术语 – 数据速率、互连介质和物理层

片式叠层陶瓷介质电容器基础介绍

车载互连中的TI技术

电子封装微互连中的电迁移

电子连接器互连中产生微动腐蚀的影响

电子连接器互连中产生微动腐蚀的影响

芯片金属互连中电镀添加剂的理论与实验研究

一文了解金属互连中阻挡层

详解金属互连中介质层

详解金属互连中介质层

评论