DDR作为一种内存技术正朝着更高性能、更低功耗的方向发展。应用前景广阔,将对半导体、计算机、汽车、新能源及各行业发展产生影响巨大。

在相同技术下,除了提高存储密度、水平方向增加芯片数量以外,一种多层存储(3D堆叠)技术被大量优化采用。

堆叠封装可以在更小的空间内提供更多的功能。堆叠封装可以开发具有不同功能的多芯片封装,或者将多个存储芯片放在一个容量增加的封装中。

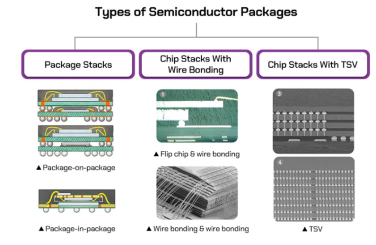

堆叠封装根据不同的开发技术分为三种类型:

PiP(Package In Package)封装

引线键合(Wire Bonding)封装

硅穿孔(TSV)封装;

堆叠封装工艺优点

封装体的尺寸小,质量轻;

顶层封装模块和底层封装模块的电子元件可以在组装前进行测试并替换,使得瑕疵率大大降低、良品比率升高,成本也大度下降;

在采取垂直互连的方式对上层和下层进行连接,大大的减小了引线长度,减少了寄生电容、寄生电感,电源损耗减小,信号的传输速度更快;

模块中的存储芯片和逻辑芯片可以由不同的商家提供,使产品的生产时问缩短,效率提高。

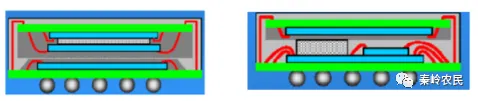

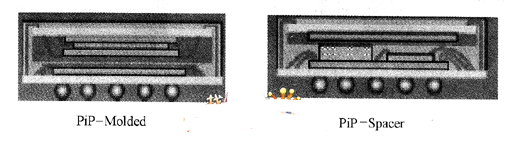

PiP(Package In Package)封装

一般称堆叠封装又称封装内的封装,还称器件内置器件,是在同一个封装腔体内堆叠多个芯片形成3D 封装的一种技术方案。封装内芯片通过金线键合堆叠到基板上,同样的堆叠,通过金线再将两个堆叠之间的基板键合,然后整个封装成一个元件便是PiP(器件内置器件)。

PiP技术整合了PCB基板组装及半导体封装制作流程,可以将小型存储卡所需要的零部件(控制器、闪存集成电路、基础材质、无源计算组件)直接封装,制成功能完整的Flash存储卡产品。PiP一体化封装技术具有下列技术优势:超大容量、高读写速度、坚固耐用、强防水、防静电、耐高温等,因此常运用于SD卡、XD卡、MM卡等系列数码存储卡上。

技术优势

外形高度较低;

可以采用标准的SMT电路板装配工艺;

单个器件的装配成本较低。

PiP封装结构

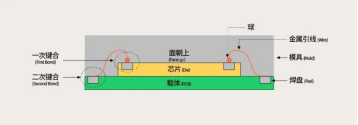

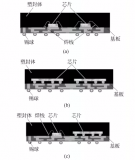

引线键合(Wire Bonding)封装

引线键合是一种将金属引线连接到焊盘上的技术,用于连接内部和外部芯片的方法。在结构上,金属引线在芯片的焊盘(一次键合)和载体的焊盘(二次键合)之间起到桥梁的作用。在早期,引线框架(lead frame)被用作载体基板,但随着技术的不断进步,如今越来越多地使用PCB作为基板。连接两个独立焊盘的引线键合涉及引线的材料、键合条件、键合位置(不仅连接芯片和基板,还可能连接两个芯片或两个基板)等方面的显著差异。

引线键合的结构(载体为印刷电路板(PCB)时)

技术优势

灵活性高:线键合堆叠封装允许在单个封装内集成不同功能和工艺的芯片,具有较高的设计灵活性。

适应性强:该技术能够适应不同尺寸和形状的芯片堆叠需求,为定制化设计提供了可能。

成本可控:与垂直堆叠封装相比,线键合堆叠封装的制造成本相对较低,适合大规模生产和应用。

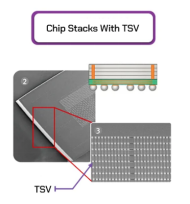

硅穿孔(TSV)封装

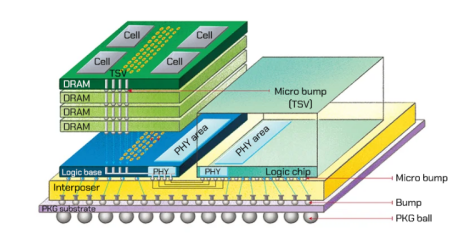

TSV是一种芯片堆叠技术,通过在硅上钻孔来连接电路。TSV不是使用传统的布线方法连接芯片到芯片或芯片到衬底,而是通过在芯片上钻孔并填充导电材料(如金属)来垂直连接芯片。虽然在与TSV堆叠时使用芯片级工艺,但在芯片正面和背面形成TSV和焊接凸起时使用晶圆级工艺。因此,TSV被归类为晶圆级封装技术。

使用TSV封装的主要优点是高水平的性能和更小的封装尺寸。如上图所示,采用线键合的芯片堆叠封装在每个堆叠芯片的侧面都有导线连接。由于堆叠的芯片和连接的引脚越来越多,布线变得越来越复杂,需要更多的空间来连接它们。相比之下,采用TSV的芯片堆栈不需要复杂的布线,因此可以减小封装尺寸。

TSV具有短的电信号传输路径,这赋予TSV封装强大的电气性能。相反,如果使用线键合,信号传输路径会变得更长,因为信号在到达芯片之前必须先到达基板,而且还不能在芯片中心进行布线连接。相比之下,TSV封装允许在芯片中心钻孔,并且可以显著增加引脚的数量。

目前量产的将TSV应用于DRAM的存储器产品包括HBM和3D堆叠存储器(3DS)。前者用于图形、网络和高性能计算(HPC)应用,而后者主要用作DRAM内存模块。

技术优势

高性能:TSV技术能够大幅缩短信号路径,降低信号传输的延迟和功耗,提升系统性能。

小型化:通过垂直堆叠和TSV互连,可以显著减小封装尺寸和重量,满足电子产品小型化、轻量化的需求。

高集成度:TSV技术能够实现多层芯片堆叠和高度集成的封装结构,提高芯片的集成密度和系统功能。

综上所述,DDR芯片的堆叠封装工艺技术作为一种先进的封装方式,在提升内存性能、集成度及降低功耗方面具有重要意义。虽然堆叠封装技术面临技术成熟度、成本问题和标准化等挑战,但随着技术的不断进步和市场需求的不断增长,其应用前景依然广阔。未来,随着半导体工艺的不断进步和封装技术的不断创新,堆叠封装技术将在更多领域发挥重要作用,推动电子产品的性能和功能不断提升。

-

芯片

+关注

关注

463文章

54473浏览量

469771 -

半导体

+关注

关注

339文章

31292浏览量

266839 -

封装

+关注

关注

128文章

9341浏览量

149090 -

内存技术

+关注

关注

0文章

29浏览量

10046

原文标题:堆叠封装的三种主要类型

文章出处:【微信号:封装与高速技术前沿,微信公众号:封装与高速技术前沿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

元器件PIP(堆叠封装)和PoP(堆叠组装)的比较

晶圆级多层堆叠技术及其封装过程

元器件堆叠封装结构

堆叠封装的安装工艺流程与核心技术介绍

一文解析多芯片堆叠封装技术(上)

芯片堆叠技术在系统级封装SiP中的应用存?

元器件PIP(堆叠封装)和PoP(堆叠组装)的比较

什么是CoWoS封装技术?

真空共晶炉/真空焊接炉——堆叠封装

堆叠封装技术的类型解析

堆叠封装技术的类型解析

评论