芯片的封装设计中,引脚宽度的设计和框架引脚的整形设计是两个关键的方面,它们直接影响到元件的键合质量和可靠性,本文对其进行介绍,分述如下:

引脚宽度设计

框架内部设计

框架外部设计

1.引脚宽度设计

引脚宽度设计的经验值主要根据线径(金线或铝线)和焊点数量来确定。以下是一些具体的设计原则:

金线单点键合

当线径小于1.5mil时,引脚宽度的最小值设计经验值为8mil。

当线径大于或等于1.5mil时,引脚宽度的最小值设计经验值为4倍的线径加2.0mil,再减去冲压精度的影响。

金线多点键合

对于线径小于1.5mil的金线多点键合,引脚宽度的最小值设计经验值为焊点数量乘以4.5再加2mil。

对于线径大于或等于1.5mil的金线多点键合,引脚宽度的最小值设计经验值为焊点数量乘以6.0再加2mil。

铝线键合

当线径小于6.0mil时,引脚宽度的最小值设计经验值为15mil。

当线径大于或等于6.0mil时,引脚宽度的最小值设计经验值为2.5倍的线径加2.0mil再减去冲压精度的影响,并额外加上5mil的切刀距离。

在叠层键合技术(BSOB)的情况下,引脚宽度的最小值设计原则略有不同,但总体趋势相似。对于金线单点键合,引脚宽度的最小值设计经验值可以降低到6.5mil;而对于金线多点键合,则与上述原则一致。

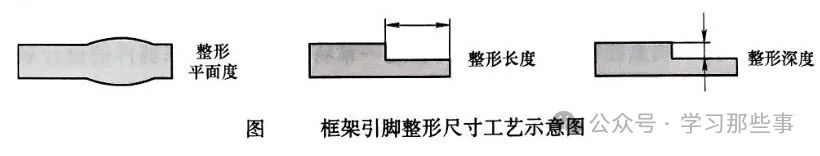

除此之外,框架的引脚整形设计还需要保证键合质量并锁住塑封料。整形尺寸的设计需要遵循以下原则:

整形深度(Coin depth)

整形深度应控制在0.2~2.0mil之间。这个深度范围可以确保引脚在整形过程中不会受到过度的损伤,同时又能达到预期的整形效果。

整形长度(Coin length)

整形长度应至少达到引脚边最小20mil,或在某些情况下为最小30mil。这是为了确保引脚在整形后能够保持足够的强度和稳定性。同时,如果制造过程中宽度方向的整形平面度(Coin flatness)经过80%的整形,那么整形长度的要求可能更为严格。

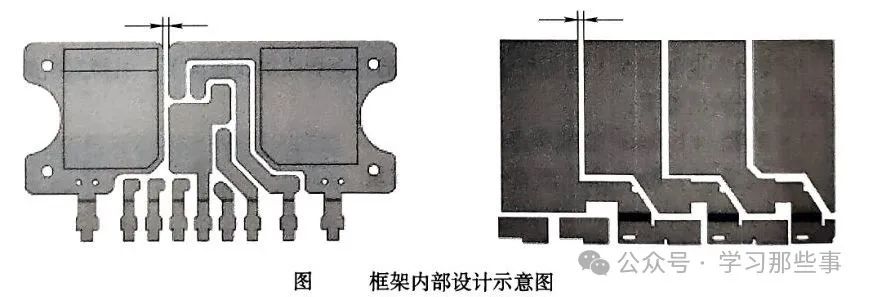

2.框架内部设计

框架内部设计需综合考虑基岛形状、引脚锁孔、引脚及基岛间距、封装体外部距离、支撑筋、沟槽、酒窝、下沉距离、电镀处理区域以及第一脚等多个方面,以确保封装质量和性能。

基岛形状及间距设计

基岛形状需根据具体封装需求进行设计。表面平整和电镀后,金属基岛间距的最小值需根据框架厚度确定:框架厚度小于0.127mm时,间距为0.10mm;框架厚度大于或等于0.127mm时,间距为框架厚度的0.8倍。

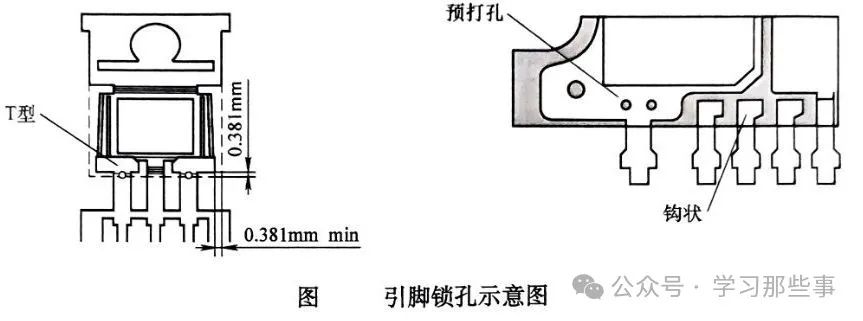

引脚锁孔设计

引脚锁孔用于锁住塑封料以防止湿气进入。引脚锁孔边缘到封装体边缘的距离通常设计为8mil(0.2032mm),特殊情况下可调整为5mil(0.127mm),10mil(0.254mm)更佳。

引脚锁孔的设计

角上的引脚必须保证最小值为0.254mm。锁孔形状可以是T形或钩状,以保证良好的锁定功能。

引脚及基岛间距设计

引脚可以设计成圆弧状态,圆弧的中心线位于基岛,但不适用于多芯片多基岛封装框架;框架引脚到基岛的最小距离通常是框架厚度的1倍以上,特殊情况下可放宽至0.8倍;封装体外部到引脚的距离需参考引脚锁孔到封装体边缘的设计准则,引脚边缘到封装体外沿距离设计不小于0.254mm。

封装体外部距离定义

没有设计引脚的基岛边缘到封装体边缘最小距离为0.305mm。设计引脚间距时,需考虑键合时夹具压板的空间分布。

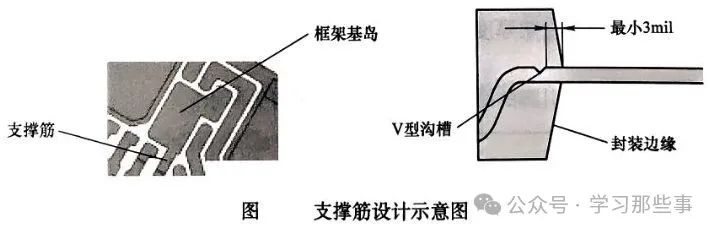

支撑筋设计

支撑筋用于在封装过程中支撑整条框架;支撑筋的宽度最小值不得小于1.5倍的框架厚度,典型经验值是0.254mm以上。

支撑筋的设计

支撑筋末端应设计V型沟槽,以便脱模过程中封装体稳定,并锁定塑封料,防止湿气进入。

V型沟槽与U型沟槽设计

V型沟槽设计在框架的表面和底面,开槽位置需避开引脚薄弱点。

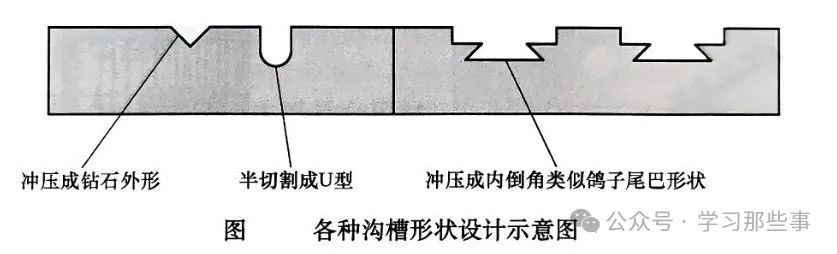

沟槽形状设计

深度设计范围是0.05~0.5mm、开槽倒角角度设计为90°、距离引脚平整区至少0.125mm,同时距离封装体外沿0.075mm(封装引脚上沟槽中心最小间距0.2mm的情况下)。U型沟槽设计在基岛上,用于防止焊料溢出基岛。

酒窝设计

酒窝设计用于在基岛上更好地锁定塑封料。常见酒窝形状包括直接冲压成钻石外形、半切割成U型和冲压成内倒角类似鸽子尾巴形状。

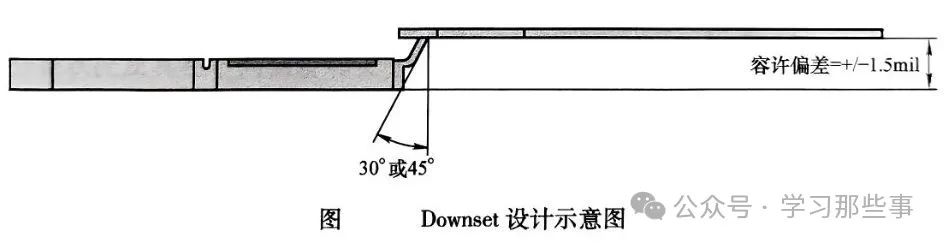

下沉距离设计

支撑筋上的下沉设计需在原始引脚和基岛之间,用于避开加热块。

下沉设计

Downset角度设计通常为30°或45°,以避免框架折弯导致的封装工艺质量问题。

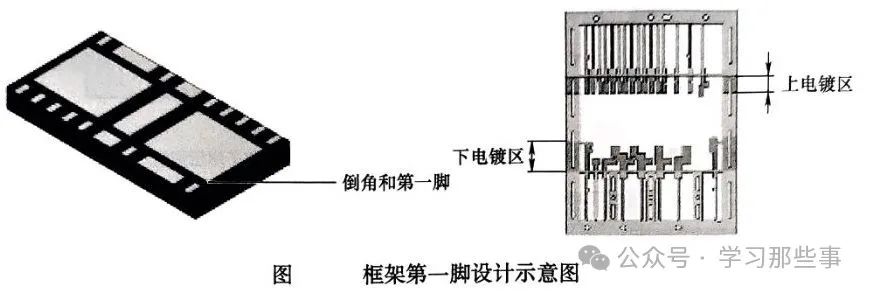

电镀处理区域设计

从框架基岛到引脚内互联区需做电镀处理的区域设计,通常是基岛中心线到封装体边缘减去0.0635mm(根据塑封模具设计的最大边缘错位允许偏差而定)。

第一脚设计

封装元件的第一脚位对电路组装起到决定性作用。第一脚必须设计在封装体的边角位置,便于肉眼识别。

第一脚设计

在多排框架的情况下,第一脚设计在基岛拐角的倒角处,应尽量和基岛的倒角接近。

3.框架外部设计

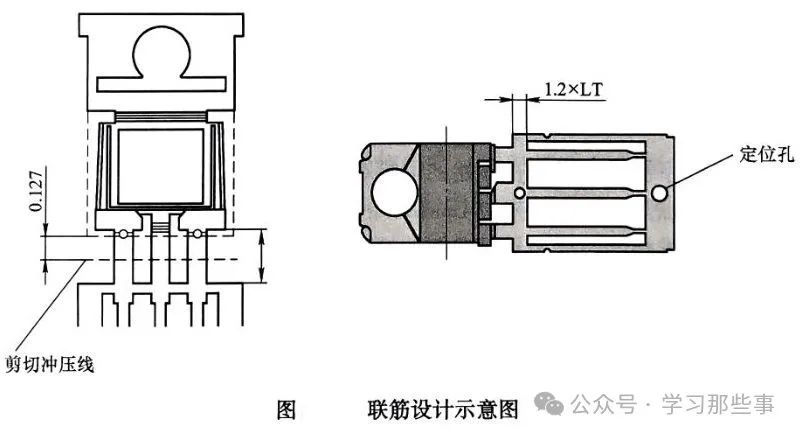

联筋(Dambar)设计

联筋在封装过程中起着至关重要的作用,它不仅阻止塑封料的流动,还保持外引脚的形状直至切筋工序。为了确保其有效性,最小的联筋宽度通常设计为框架厚度的1.2倍。联筋过薄可能会导致塑封料溢出,影响封装质量。

联筋设计

同时,从封装体边缘到联筋区的最小距离应保持在0.127mm,以确保切筋时冲压模具的制造能力。

假脚(False Leads)设计

假脚设计旨在提供引脚支撑,特别是在需要锚定引脚位置的场合。在切筋成型过程中,当最后一个功能引脚被分离成型时,假脚能够保持封装体的稳定性。然而,对于一体成型切割,假脚可能并不必要,反而会增加框架材料和制造费用。因此,假脚设计是一个可选项,而非必选项。

-

框架

+关注

关注

0文章

404浏览量

18491 -

引脚

+关注

关注

16文章

2119浏览量

56009 -

芯片封装

+关注

关注

14文章

620浏览量

32390

原文标题:芯片封装——引脚设计

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

4029芯片引脚图及功能

芯片封装知识介绍-很全面的!

芯片封装设计中的wire_bonding知识介绍

请问为什么布线要设置宽,最后又变细了,和芯片引脚相接?直接把布线宽度最大和芯片引脚一样宽不行吗?

请问S29GL128P10TFI01的封装引脚宽度是多少

芯片封装详细介绍

25引脚倒装芯片四平面无引脚封装(FCQFN)包装外形图

芯片封装设计引脚宽度和框架引脚的设计介绍

芯片封装设计引脚宽度和框架引脚的设计介绍

评论