大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天给大侠带来PCI-Express transaction Layer specification(处理层协议),本次PCIE TLP 学习经验分享分为三篇,今天带来第一篇TLP概况(四种空间、三种处理类型、两种属性、主要包格式、TLP通用包头)和TLP打包地址和路由导向方式(Address寻址、ID寻址方式、处理层描述符),话不多说,上货。 为了方便各位大侠浏览,下面列出三篇分享的大概内容目录介绍:

- 一、TLP概况

- 1. 四种空间

- 2. 三种处理类型

- 3. 两种属性

- 4. 主要包格式

- 5. TLP通用包头

- 二、TLP打包地址和路由导向方式

- 1. Address寻址

- 2. ID寻址方式

- 3. 处理层描述符(transaction Descriptor)

- 三、I/O,Memory,Configuration,Message Request、Completetion详解

- 1. Memory Request Package

- 2. I/O Request 包

- 3. Configuration Request包

- 4. Message

- 5. Completion Rules(应答机制)

- 四、请求和应答处理机制

- 1. Request Handling Rules

- 2. Completion Handling

- 五、virtual channel(vc)Mechanism虚拟通道机制

- 1. TC/VC映射

- 2. Flow Control

- 六、Data Integrity数据完整性

一、TLP概况

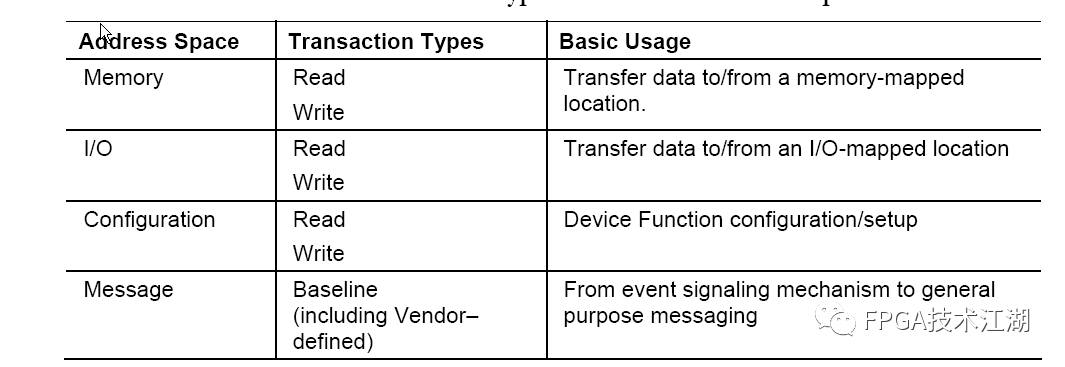

处理层(transaction Layer specification)是请求和响应信息形成的基础。包括四种地址空间,三种处理类型,从下图可以看出在transaction Layer 中形成的包的基本概括。

1. 四种空间:

2. 三种处理类型

i/o口和memory的读写包(TLPS:transaction Layers packages)

配置寄存器的读写设置包

信息包,描述通信状态。

作为事件的信号告知用户。

对memory的读写包分为读请求包和响应包、写请求包(不需要存储器的响应包)。而i/o类型的读写请求都需要返回I/O口的响应包,configuration包对配置寄存器的读写请求也有响应包。这些请求包还可以按属性来分类。

3.两种属性

Non Posted:即请求需要返回completion的响应包;

Posted:即不需要completion返回响应包。例如上面的存储器写入请求包和Message包都隶属于posted包。

4. 主要包格式

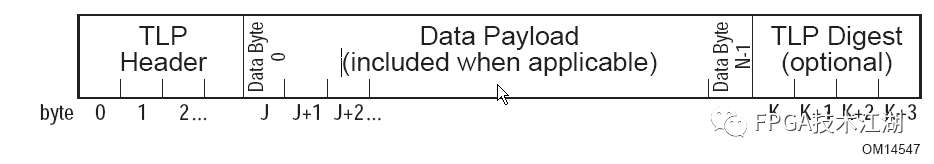

每种类型的包都有一定格式的包头(Tlp Header),根据不同的包的特性,还包括有效数据负荷(Data Payload)和tlp开销块(Tlp Digest)。包头中的数据用于对包的管理和控制。有效数据负荷域存放有效数据信息。具有数据的TLP传递是有一定规则的:以DW为长度单位,发送端数据承载量不得超过“Device Control Register”中的“Max_Payload_Size”数值,接收端中,所接收到的数据量也不能超过接收端“Device Control Register”中的“Max_Payload_Size”数值。TLp Digest域是32位的ECRC校验。具体的包结构图如下:

由此图可看出数据从低字节的高位先发送,从左到右。以下详细介绍TLPS的每个成分。

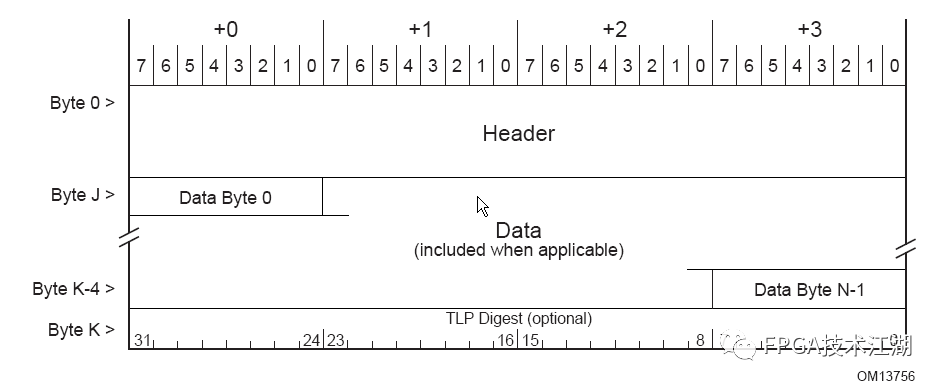

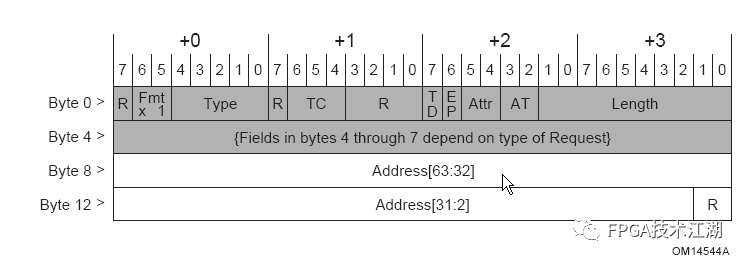

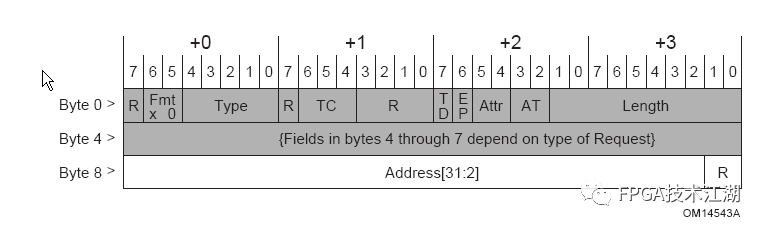

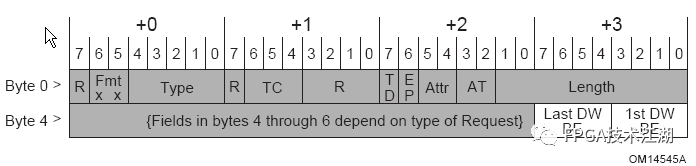

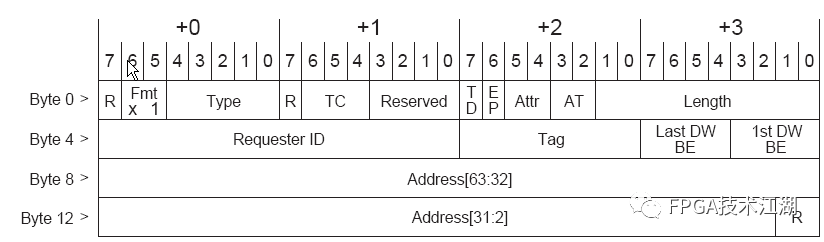

5.TLP通用包头

R为保留信息位,应设为0,路由器switch对此位不做修改,接收器应该忽略此位。

Fmt[1:0]:Format of TLP (see Table 2-2) – bits 6:5 of byte0。

Type[4:0]:Type of TLP – bits 4:0 of byte 0。

TC[2:0]: Traffic Class – bits [6:4] of byte1,关于TC的作用将在下文说明。

Attr[1:0]: Attributes – bits [5:4] of byte 2,详细介绍见下文。

TD:1b indicates presence of TLP digest in the form of a single DW at the end of the TLP标志TLPDigest域的有无。

EP: indicates the TLP is poisoned – bit 6 of byte 2有效数据中毒(出错)机制。

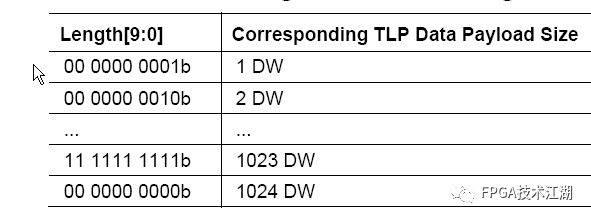

Length[9:0]:Length of data payload in DW。

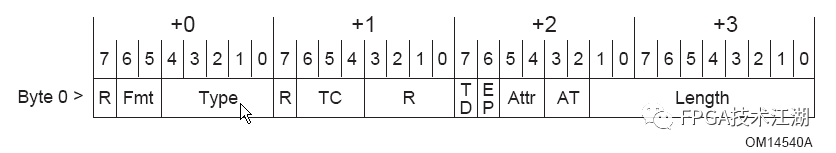

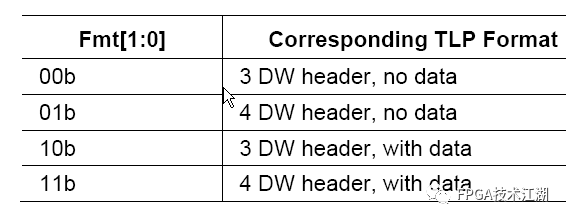

Fmt开销位说明TLP Header的长度和TLP是否包含数据,如下图:

Fmt[1:0]=00b,代表3DW的包头,没有数据。

Fmt[1:0]=01b,代表4DW的包头,没有数据。

Fmt[1:0]=10b,代表3DW的包头,有数据。

Fmt[1:0]=11b,代表4DW的包头,有数据。

Fmt [0] 表示包头格式是3长字还是4长字,Fmt[1] 表示包头是否包含数据。

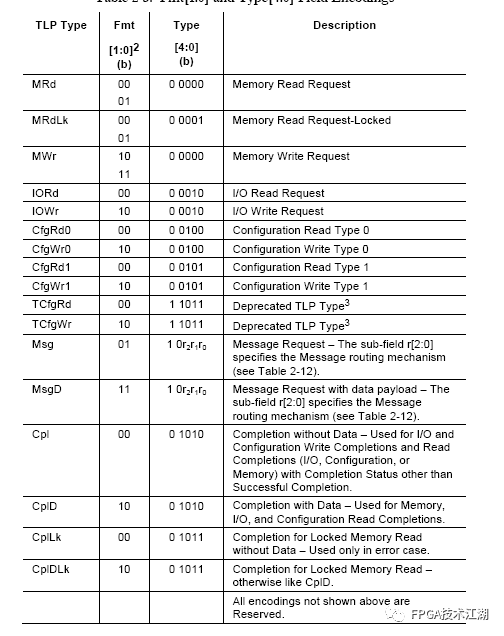

Fmt和Type开销组合定义了包(TLP)的类型如下:

上图定义了各种类型的包,图中的r[2:0]用于定义Message包的隐含寻址方式,在下文中更为详细。 Length域定义了有效负荷的DW长度如下:

在不包含data payload块的包中Length的值应被设置为保留值R,并被接收端忽略。余下的各个开销位将在后文提到。

二、TLP打包地址和路由导向方式

地址路由(address)

ID识别路由

间接路由(implicit) 下面主要介绍address和ID寻址方式,间接寻址将在后面提及。

1.Address寻址

主要用于memory和i/o request请求包

memory读写请求包支持64位地址和32位地址,

i/o读写请求只支持32位地址

64位地址寻址的TLP Header有4DW(16字节),

32位地址寻址的TLP Header有3DW长。

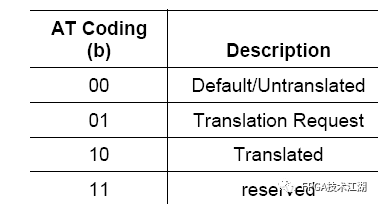

上图就是64位地址的4DW的包头和32位地址的3DW的包头。对于memory读写request包,AT(address Type field)有如下的编码。

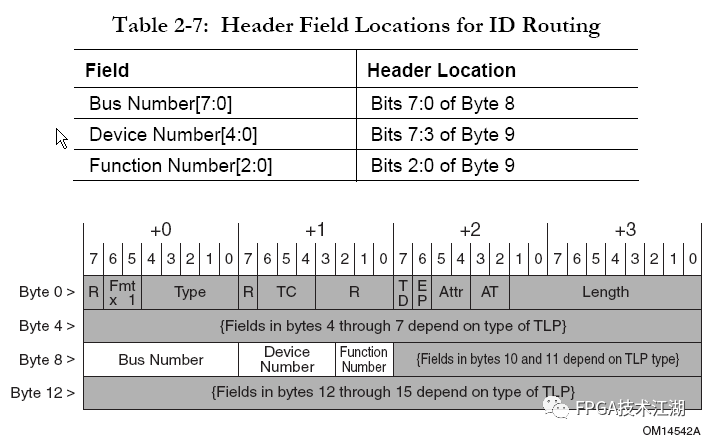

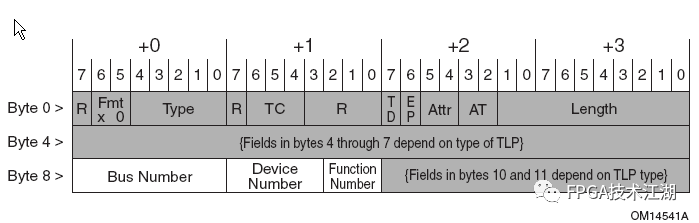

2.ID寻址方式

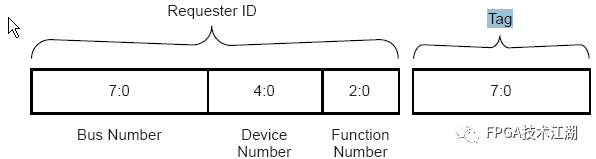

主要用在configuration 请求包、部分message包、响应包中。ID包括Bus number、Divce number、function number为TLP定位目标接收器。ID寻址的TLP包头长度也有4DW和3DW两种,ID在TLP中位置见下图。

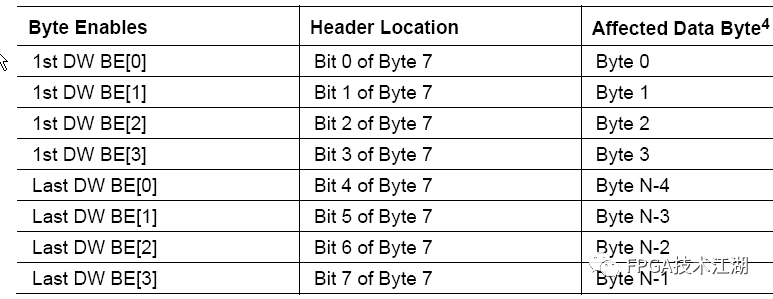

第七个Byte(Byte7)是第一个DW数据负荷和最后一个DW数据负荷使能位(Byte Enables),Byte Enables在于memory,i/o,configuration 请求包中有效,如图。

对于last DW BE和1st DW BE中的每一个位,为0表示相应的数据字节不被读或写,为1表示相应的数据字节有效。每个使能位相对应的字节如下。

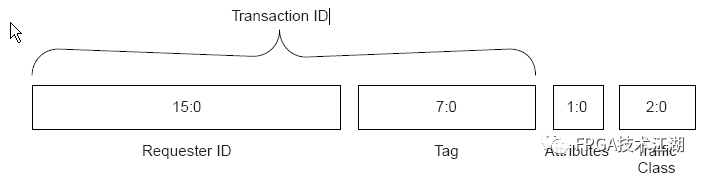

3.处理层描述符(transaction Descriptor)

对于两种路由方式来说是通用的。

用于请求器件和应答器件间转送处理层信息,包括三部分,Transaciton ID、Attributes、Traffic class(TC),如下图。

其中Transaction ID包括: Requester ID、Tag,如图。

Tag[7:0]是由产生请求包的器件生成的,如果请求器件需要应答,则每个Tag[7:0]和Function Number是独一无二的。Transaction ID是一个全局标识符用于响应包寻址请求器件。

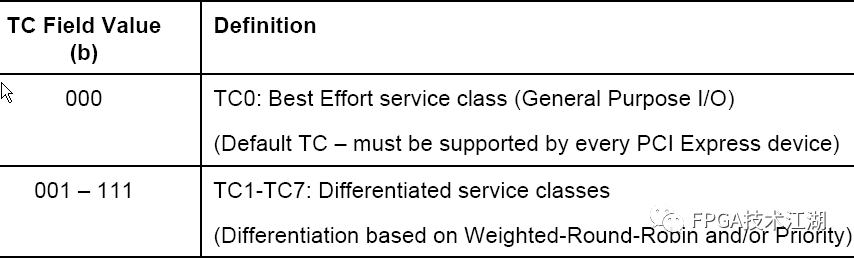

TC的规定如下,描述服务的层次和用于映射虚拟通道:

处理层描述符在请求包中第二个DW:

从图中看出,描述字符放在第二个DW的前三个字节中。

第一篇到此结束,下次金带来第二篇,i/o,memory,configuration,message request、completetion(Memory Request Package、I/O Request 包、Configuration Request包、Message、Completion Rules(应答机制))等。

-

FPGA

+关注

关注

1630文章

21796浏览量

605546 -

寄存器

+关注

关注

31文章

5363浏览量

121030 -

PCI

+关注

关注

4文章

671浏览量

130439 -

TLP

+关注

关注

0文章

32浏览量

15661

原文标题:PCI-E TLP(处理层协议)学习经验分享 I

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在FPGA上设计PCI-e Gen2.0和PCI-e Gen3.0有什么不同

解决台式机PCI-E 1X不够难题 :乐扩PCI-E 1X转2口PCI-E 1X扩展卡

PCI PCI-X PCI-E介绍 精选资料分享

PCI-e总线FPGA开发板资料说明

浅谈显卡PCI/AGP/PCI-E接口的区别

Intel的核显真的占用了CPU的4根PCI-E通道吗

pci-e插槽的规格有哪些 各个版本的pci-e的规范区别

PCI-E TLP学习笔记(2)

PCI-E TLP学习笔记(3)

PCI-E TLP学习笔记(1)

PCI-E TLP学习笔记(1)

评论