以下文章来源于ICPMS冷知识,作者gz07apple

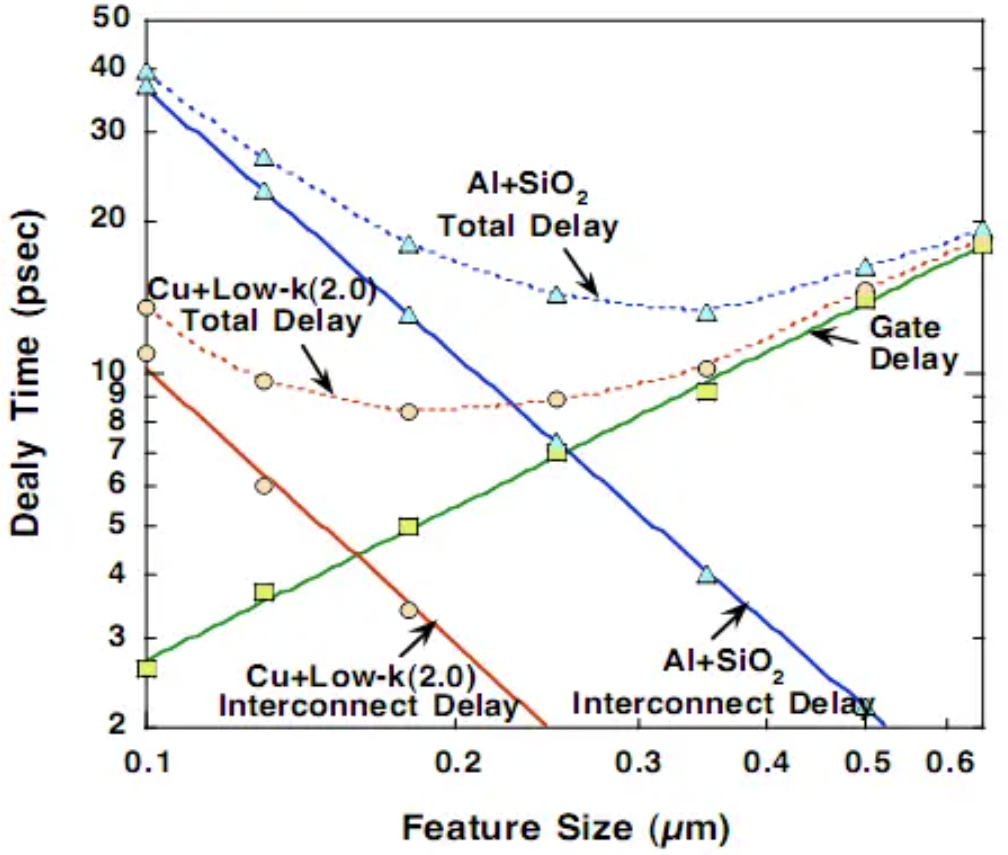

半导体永远都是在围绕摩尔定律(Moore's Law),不仅有器件物理尺寸以及制程工艺上的微缩,还有后段金属互连。对于下游应用来说,影响芯片主要性能之一就是功耗,还有就是速度。功耗当然就是要靠降低电压和漏电流来解决,那速度呢?要么靠器件的驱动能力,要么靠减小 RC 延迟。尤其到了采用纳米制程的 CPU 以及 AP 处理器时代,功耗和速度将是各家 Fab 的卖点。

传统提高速度的方法就是集成,把多个芯片结合在一起减少芯片之间的互连电阻,同样的道理,到了纳米制程的互连越来越复杂,导致了互连的电阻以及电容将会成为处理器的主要杀手。所以如果要提高速度或运算频率,就必须降低RC(Resistance - Capacitance)延迟,其中 R 主要来自金属互连导线的电阻,而 C 主要来自金属间介质电容。

一、氟硅玻璃

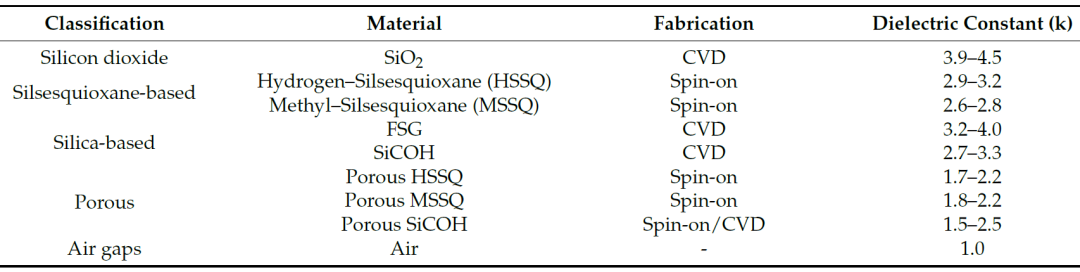

在传统的微米制程时代,互连工艺使用的还是铝和二氧化硅。当半导体进入0.18 μm制程节点,要想更快降低“电容” ,就要求材料的介电常数(k值)变得更小,因此二氧化硅(k值为3.9)注定要被其它低介电常数材料(Low k)所取代。

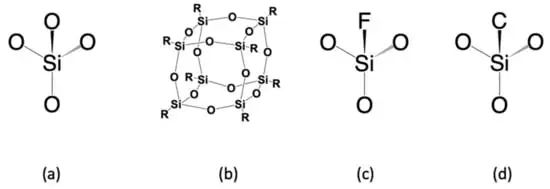

半导体行业首次对低介电常数材料的尝试是考虑用硅倍半氧烷(SSQ) 取代二氧化硅。SSQ是一种有机硅,通常为八角笼几何结构。从上表中可以看到,甲基SSQ和氢基SSQ的介电常数都比较低。在工艺上,SSQ比较适合用旋涂(Spin-on)方法来制备薄膜。不过SSQ 最终还是被人们排除在外,主要还是由于后续工艺整合难度拖了后腿(SSQ热稳定性太差、机械强度低)。研发人员考虑再三,在不改变现有工艺的前提下,最简单的就是掺入“氟” 将二氧化硅变成氟硅玻璃(FSG),于是第一代低介电常数材料问世了。

a) 二氧化硅; (b) 硅倍半氧烷 (SSQ);(c) 氟硅玻璃 (FSG);(d) 碳掺杂氧化硅(SiCOH)

由于氟硅玻璃含有极化率较弱的硅氟(Si-F)键,因此介电常数可以降到3.2,这也符合当时的思路,通过引入极化率比较低的化学键来降低材料的介电常数。不过也正是由于硅氟键,氟硅玻璃在高温下热稳定性并不好,同样不利于后续的工艺整合。

二、碳掺杂氧化硅

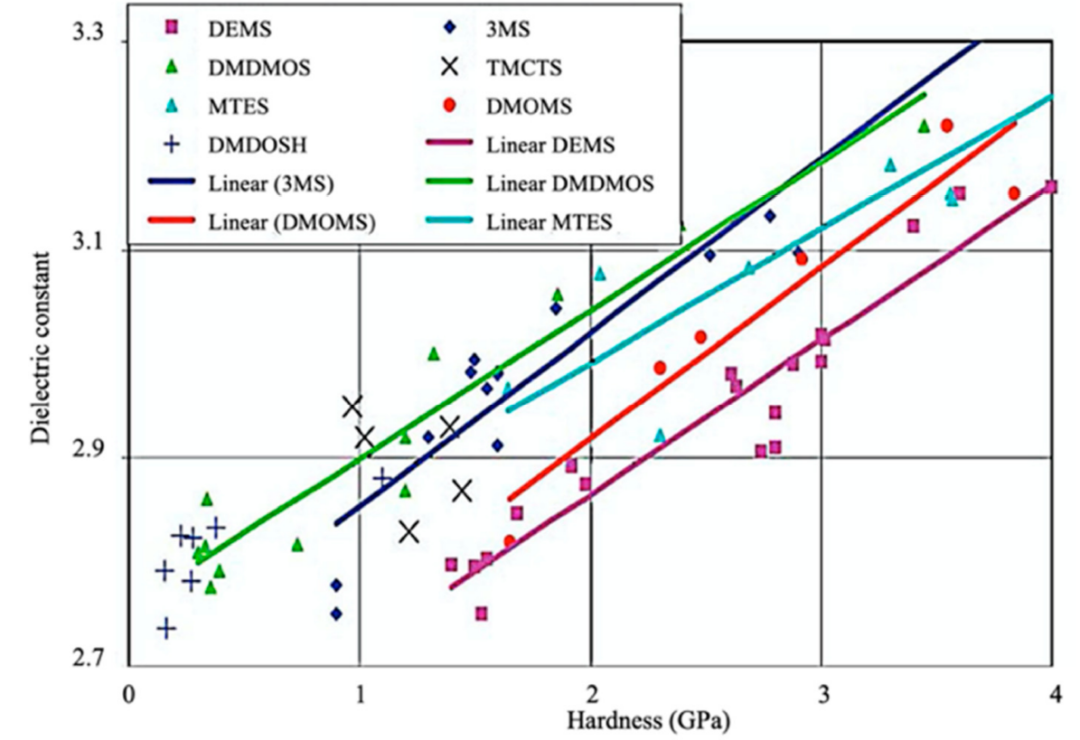

当半导体进入90 nm制程节点,第二代低介电常数材料,即碳掺杂氧化硅(SiCOH)开始规模化应用。碳掺杂氧化硅是通过引入低极性硅碳(Si-C)键来实现低介电常数(k值为2.7~3.3)。思路还是过去的老思路,只不过对象材料变了。相比于硅氧(Si-O)键和硅氢(Si-H)键,硅碳键可以产生更大的空间体积和更低的极化率,因此碳掺杂氧化硅拥有更低的介电常数和更好的机械性能。相比于SSQ使用的旋涂工艺,碳掺杂氧化硅可以使用与二氧化硅或氟硅玻璃相同的沉积工艺,这点对于工艺整合来说还是非常友好的。

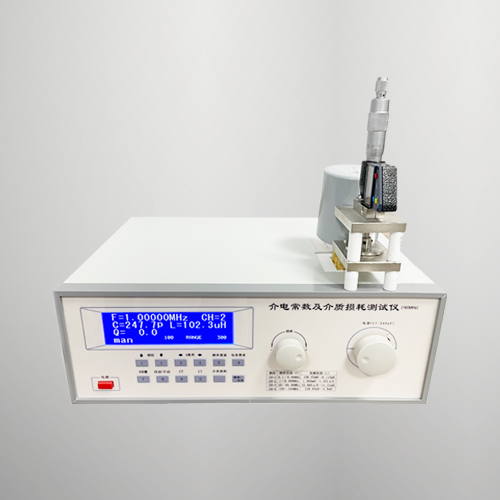

从上图可以看到,DEMS(二乙氧基甲基硅烷)表现出优于其他前驱体的性能指标(更低的介电常数和更高的硬度)。工艺上通常会以惰性气体为载气将烷基硅氧前驱体(如DEMS、3MS、TMCTS 等)与氧化剂(如氧气、臭氧、 氧化亚氮)注入腔体,反应形成一层包含硅碳、硅氧和硅氢键的薄膜。在实际应用中,各种烷基硅氧前驱体分子中上述三种化学键与硅原子的摩尔比,最终会影响碳掺杂氧化硅薄膜的性能。对于工艺人员来说,选择哪种前驱体沉积低介电常数薄膜,还是应该针对电学、力学、热学、化学性能以及低成本做综合考量。

这里讲一个小故事:台积电和联电在0.13 μm制程节点还曾有过低介电常数材料的路线之争。当年台积电使用的是应用材料(AMAT)提供材料(SiCOH,k值约为2.9),使用化学气相沉积方法制备薄膜。应材的碳掺杂氧化硅材料还有个商业名字叫作黑钻石(Black Diamond)。

联电使用的是陶氏化学(DOW)生产的一种旋涂介质(Spin On Dielectric,SOD)材料制备薄膜。该介质材料的商业名字叫作SiLK(结构至今保密,k值约为2.7)。对比介电常数,看似联电稍胜一筹,实际上在RC延迟性能上大家并没有太大差别。

不过当迈入90 nm 制程节点,介质材料的性能变得愈发重要。这个时候台积电才告诉人们当初为什么选择碳掺杂氧化硅,因为它制备的薄膜热稳定性和应力都得到了比较好的控制,而陶氏化学SiLK 制备的薄膜则很容易出现裂纹并且偶尔会剥落。

三、多孔超低介电常数材料

尽管第二代材料在后续工艺整合中具有出色的机械强度,但它的介电常数下限是2.7。为了突破该瓶颈,研发人员又有了新思路。通过在介质材料中引入孔隙来降低其介电常数,因为孔隙中会充满空气(k值为1)。当半导体制程工艺进入 45 nm,行业迫切需要介电常数低于 2.6 的介质材料,也就是超低介电常数材料(Ultra Low k,ULK)。

前面提到,进一步降低介电常数需要在材料中引入多孔(Porous),而这种多孔结构可以通过本构法或减法来获得。简单来说,本构多孔就是指在薄膜沉积过程中产生的孔隙,后期无需任何处理,孔隙结构取决于原始的沉积态排列。

而减法多孔则是从预制的薄膜中选择性再去除部分材料。换句话说,就是在沉积过程中加入额外的致孔剂来产生孔隙。致孔剂会在后续的固化过程(使用热处理或使用电子束或紫外线)中被去除。

多孔材料的孔径对薄膜性能有着极其重要的影响。当孔径过大时,在双大马士革工艺中沉积的其他薄膜(比如金属阻挡层)很容易穿透层间介质层并破坏其介电性能。此外,大孔也会导致其机械硬度和应力变差,这将为后期工艺整合带来困难。当孔径变得太小时,孔隙将不足以有效降低介电常数。总之,减法多孔薄膜比本构薄膜具有更好的力学和电学性能,而本构薄膜保留了较高的碳含量,对抗等离子体诱导损伤(PID)能力会更出色一些。

当半导体制程工艺来到28 nm,多孔结构的超低介电常数材料(pULK)已成长为当仁不让的主角。不过,pULK 薄膜的机械强度低、热稳定性和粘合强度差,多孔结构又容易捕获其它化学物质,以上这些都大大增加了后端互连结构集成的复杂性。有人曾做过形象地比喻,pULK的工艺整合难度就相当于用海绵而不是混凝土来建造一面完美的防火墙。

四、工艺整合挑战及展望

制备介电常数低于2.6的多孔薄膜相对容易,实际上真正的挑战是,如何成功地将薄膜制备方法集成到芯片工艺中,这也是为什么需要对低介电常数材料持续进行改性。在此之前我们先了解下薄膜的制备方法。

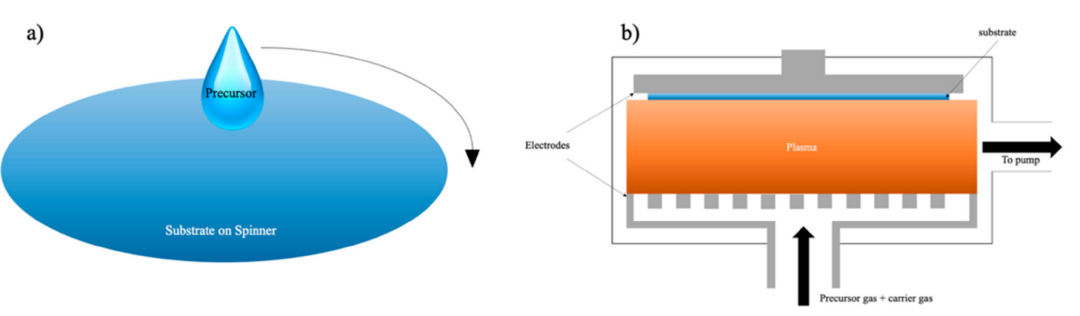

在半导体制造中,低介电常数薄膜的两种最常见制备方法是:旋涂和化学气相沉积(CVD)。旋涂优点是简单、成本低,容易从分子聚合物工程学中受益。但缺点也非常明显,它不是一种适合规模化生产的方法。在双大马士革工艺中,由于许多不同材料层会相互叠加,选择旋涂工艺需要跟各种CVD 腔室之间来回切换,这种工程设计会使生产变得极其复杂且昂贵。此外,旋涂的高温热退火将给后续工艺整合带来麻烦。

相比之下,CVD(通常为 PECVD)作为介质薄膜沉积的传统方法,往往是 Fab 的首选。首先,PECVD 制备的薄膜具有很好的保形性,间隙填充性能也不错。其次,可以实现低于 20 nm 级别的薄膜厚度,从而提高布线密度。最后,很容易地适应规模化生产,而无需对现有产线做过多修改。

不过,随着第三代材料的规模化应用,它们所存在的力学、热学性能问题也为工艺整合带来了许多新的挑战。因此,在过去的几十年里,人们对工艺整合过程进行了重新设计,以最大限度地保持 pULK 薄膜的介电性能。比如,通过在初始沉积阶段应用氧等离子体以产生氧化状态来改善粘附力,后续研发了包括增加碳含量、氨等离子体表面处理和致孔后等离子体保护处理等方法,以最大限度地减少工艺相关的等离子体诱导损伤。

相信在不久的将来,随着介质薄膜尺寸将不断缩小,甚至到几纳米,并且相关材料的电学、力学和热学性能的要求将越来越高,迫切需要新型的有机-无机纳米复合材料、3D 多孔材料以及相应的工程改进方法,为下一代 IC 封装铺平道路。

-

半导体

+关注

关注

339文章

31459浏览量

267472 -

cpu

+关注

关注

68文章

11364浏览量

226320 -

低介电常数

+关注

关注

0文章

4浏览量

5417 -

制程工艺

+关注

关注

0文章

47浏览量

9841

原文标题:【强烈推荐】低介电常数材料的发展历程简介

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

介电常数怎么测试_介电常数测试方法

相对介电常数和介电常数的关系

介电常数的定义及应用 不同材料的介电常数比较

介电常数对电子设备的影响

介电常数在无线通信中的应用

如何选择适合的材料以满足介电常数要求

如何测量材料的相对介电常数

不同材料的相对介电常数比较

材料介电常数会影响电子元器件哪些性能

为什么芯片需要低介电常数材料

低介电常数与高介电常数的高分子材料:从机理、结构到应用的全面解析

低介电常数材料的发展历程

低介电常数材料的发展历程

评论