Salicide 工艺是指在没有氧化物覆盖的衬底硅和多晶硅上形成金属硅化物,从而得到低阻的有源区和多晶硅。

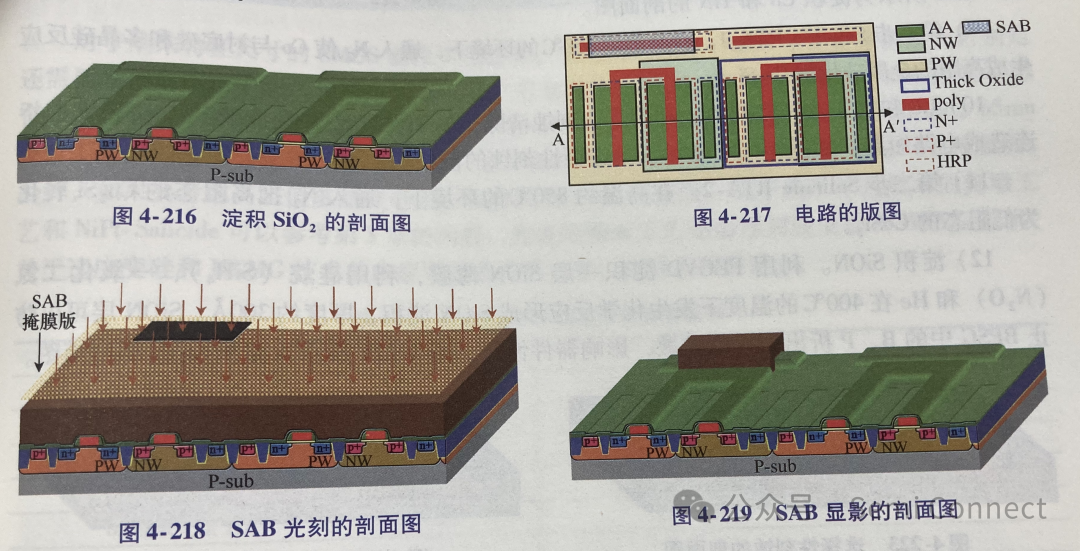

1)淀积 SAB(Salicide Block,金属硅化物阻挡层)。利用PECVD淀积一层 SiO2,目的是形成 SiO2把不需要形成金属硅化物(Salicide)的衬底硅和多晶硅覆盖住,防止形成 Salicide。图4-216所示为淀积 SiO2的剖面图。

2) SAB光刻处理。通过微影技术将SAB掩膜版上的图形转移到晶圆上,形成SAB 的光刻胶图案,非SAB区域上保留光刻胶。AA作为SAB光刻曝光对准。图4-217所示为电路的版图,工艺的剖面图是沿 AA'方向,图4-218所示为SAB 光刻的剖面图,图4-219所示为SAB显影的剖面图。

3)测量SAB 光刻套刻,收集曝光之后的SAB光刻与 AA的套刻数据。

4)检查显影后曝光的图形。

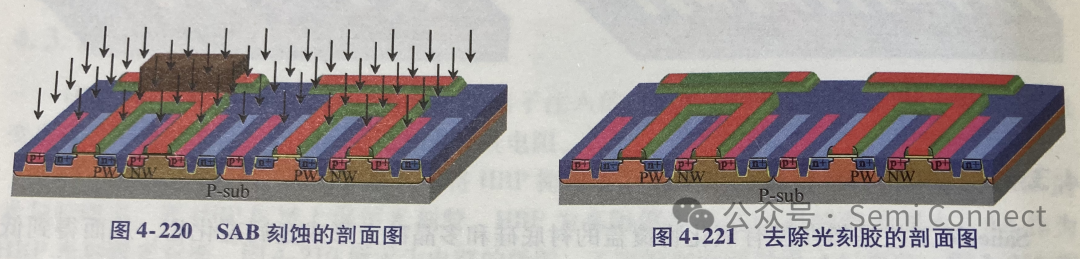

5) SAB 刻蚀处理。干法刻蚀和湿法刻蚀结合,把没有被光刻胶覆盖的SiO2清除,裸露出需要形成 Salicide 的衬底硅和多晶硅,为下一步形成 Salicide 做准备。图4-220所示为SAB刻蚀的剖面图。

6)去除光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶。图4-221 所示为去除光刻胶的剖面图。

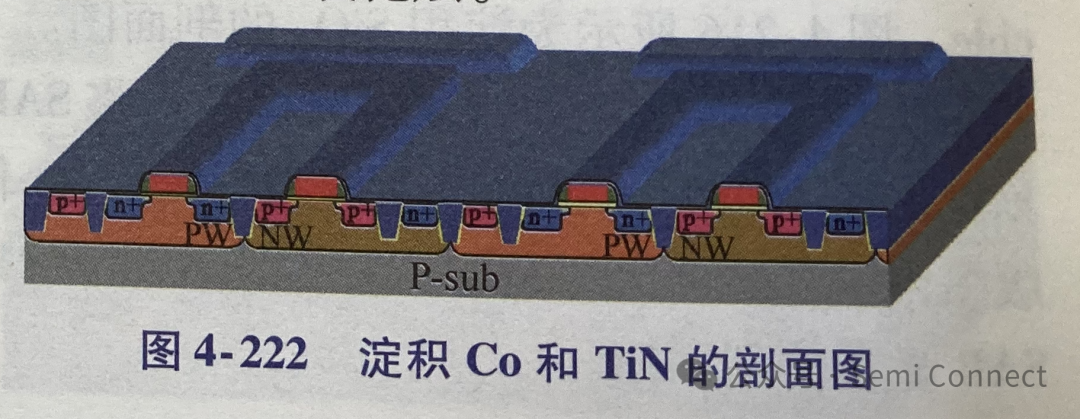

7)清洗自然氧化层。利用化学溶液NH4OH和 HF 清除自然氧化层,因后面一道工艺是淀积Co,把硅表面的氧化物清除的更干净,使Co跟衬底硅和多晶硅的清清表面接触,更易的形成金属硅化物,所以淀积 Co前再过一道酸槽清除自然氧化层。

8)淀积Co和TiN。利用PVD 溅射工艺淀积一层厚度约100A 的Co和厚度约250A 的TiN,TiN的作用是防止Co在 RTA 阶段流动导致金属硅化物厚度不一,电阻值局部不均匀。图4-222淀积 Co和 TiN 的剖面图

9)第一步 Salicide RTA-1。在高温约550°C的环境下,通入N2使Co与衬底硅和多晶硅反应生成高阻的金属硅化物Co2Si。

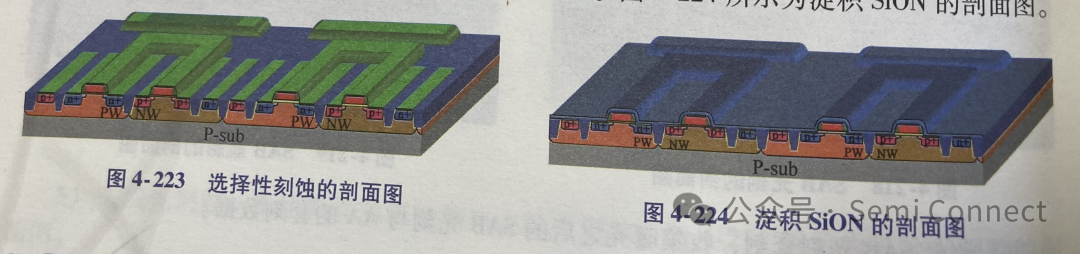

10)Co 和TiN选择性刻蚀。利用湿法刻蚀清除 TiN 和没有与Si反应的Co,防止它们桥连造成电路短路。如图4-223所示,是选择性刻蚀的剖面图。

11)第二步 Salicide RTA-2。在高温约850°C的环境下,通入N2把高阻态的Co2Si转化为低阻态的CoSi2。

12)淀积 SiON。利用 PECVD淀积一层SiON 薄膜,利用硅烷(SiH4)、一氧化二氮(N2O)和He在400°C的温度下发生化学反应形成SiON淀积,厚度约300A。SiON 层可以防止 BPSG中的B,P析出向衬底扩散,影响器件性能。图4-224所示为淀积 SiON的剖面图。

-

晶圆

+关注

关注

52文章

4917浏览量

128014 -

工艺

+关注

关注

4文章

593浏览量

28804 -

刻蚀

+关注

关注

2文章

186浏览量

13112

原文标题:Salicide 工艺-----《集成电路制造工艺与工程应用》 温德通 编著

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

双面柔性PCB板制造工艺及流程

电动汽车电机制造工艺流程图解

液晶显示器制造工艺流程基础技术

双面印制电路板制造工艺流程

芯片制造工艺流程步骤

MEMS芯片制造工艺流程

阐述电解电容制造工艺流程

Salicide工艺的制造流程

Salicide工艺的制造流程

评论