产品简述

MS5583N 是一款高分辨率模数转换器,内部集

路输入选择器和多种内部数字滤波器。其转换速率

从 250SPS 到 4kSPS。此外,芯片内部集成失调校准

寄存器和增益校准寄存器。

MS5583N 采用 QFN24 封装,其额定工作温度为

-40°C 至+85°C, 最 大 工 作 温 度 范 围 为 -40°C 至

+125°C。

主要特点

◼SNR:122dB (@250SPS, PGA=1)

◼THD:-118dB

◼正常工作功耗:21mW (PGA=1,2,4,8)

◼掉电模式功耗:10μW

◼低噪声 PGA:5 nV/ Hz

◼集成双通道多路输入选择器

◼可配置数字滤波器

◼数据转换速率:250SPS 至 4kSPS

◼失调和增益校准

◼同步 SYNC 输入控制

◼数字电源电压:1.8V 至 3.3V

◼最大工作温度范围:-40°C 至 125°C

应用

◼能量检测

◼地震波检测

产品规格分类

内部框图

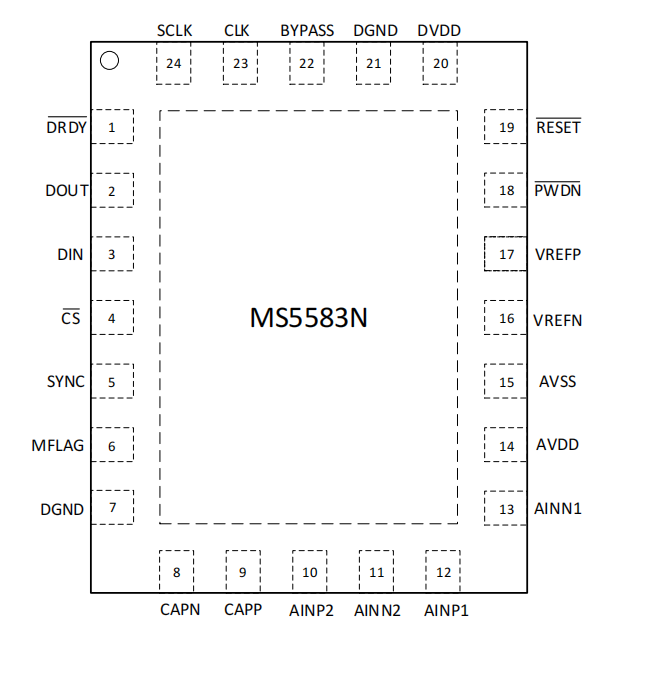

管脚图

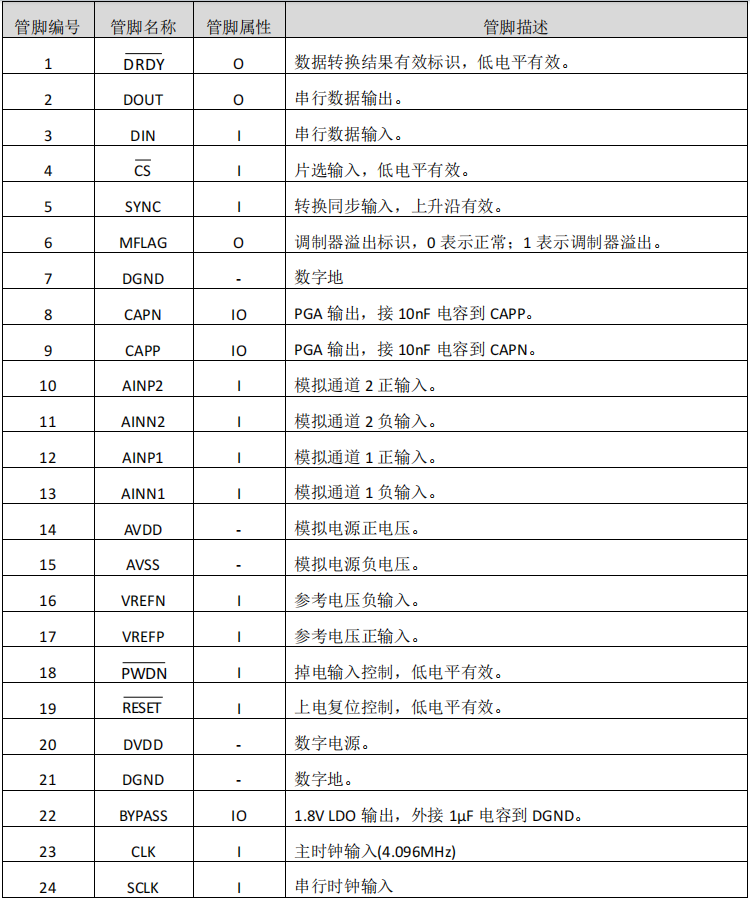

管脚说明

如有需求请联系——三亚微科技 王子文(16620966594)

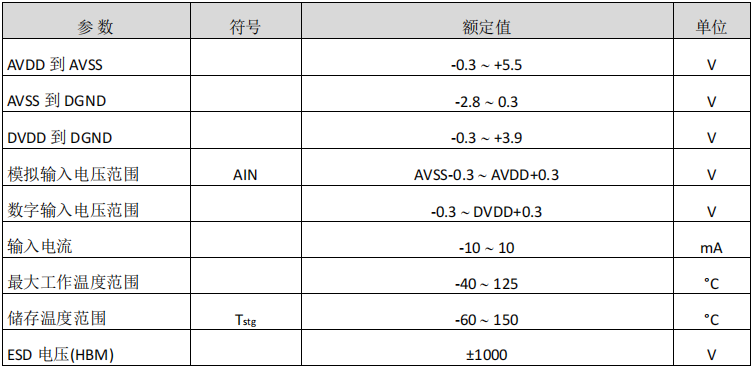

极限参数

芯片使用中,任何超过极限参数的应用方式会对器件造成永久的损坏,芯片长时间处于极限工作

状态可能会影响器件的可靠性。极限参数只是由一系列极端测试得出,并不代表芯片可以正常工作在

此极限条件下。

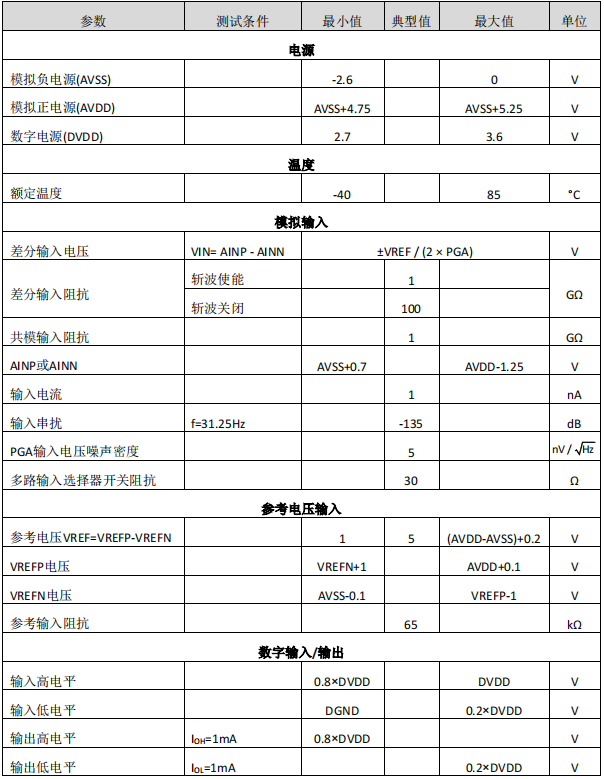

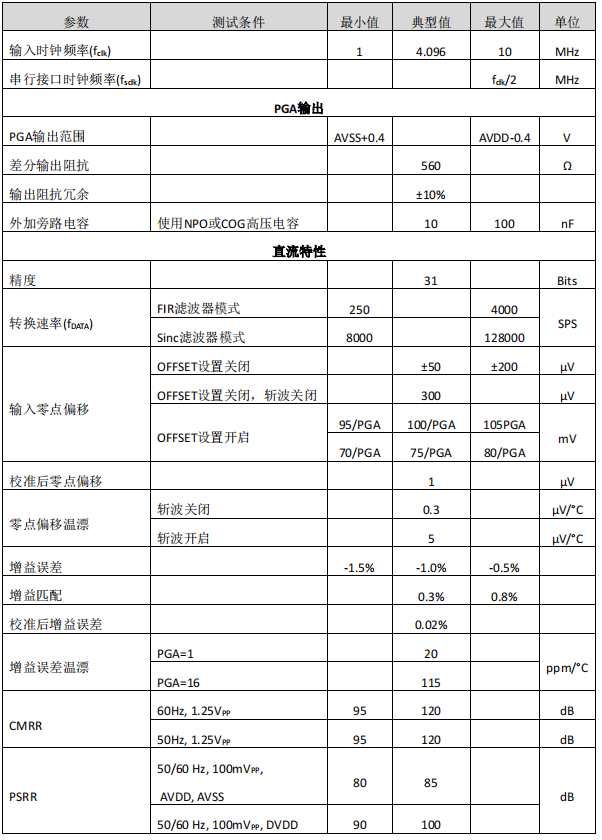

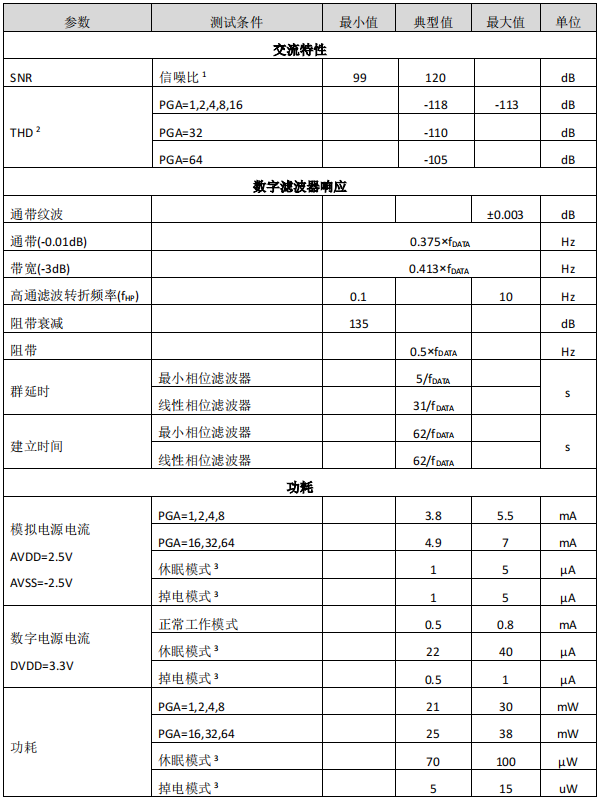

电气参数

额 定 温 度-40°C到 +85°C; 典 型 温 度25°C,AVDD=2.5V,AVSS=-2.5V;DVDD=3.3V,VREFP=2.5V,

VREFN=-2.5V,PGA=1,fclk=4.096MHz,OFFSET bit=1(使能),CHOP bit=1(使能)和fDATA=

1000SPS(除非另外标注)。

如有需求请联系——三亚微科技 王子文(16620966594)

注:1. 设置为内部 400Ω 短路,参考“模拟输入通道”说明。

2. 输入信号=31.25Hz,-0.5dBFS。

3. 关闭时钟 CLK 输入。

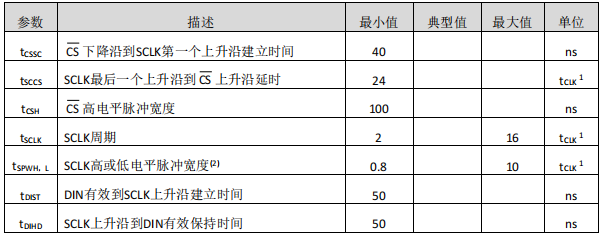

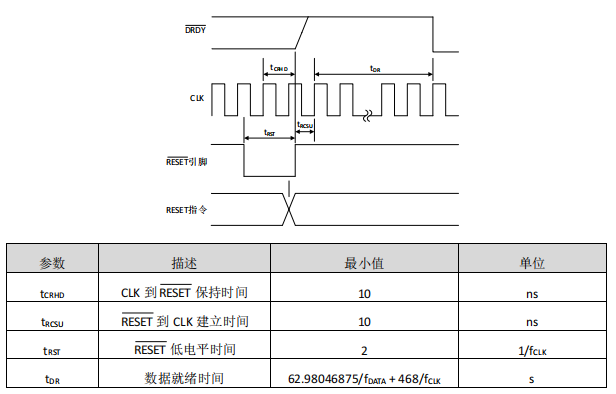

时序参数

DVDD=1.65V 到 3.6V,DGND=0V。除非另外标注,参数为全温度范围。

注:1. 系统时钟 tCLK= 1 / fCLK,默认时钟频率 fCLK= 4.096 MHz。

2. 保持 SCLK 为低电平,并经过 64 个 DRDY 下降沿后重置串行接口。

开关参数

除非另外标注,参数为全温度范围。

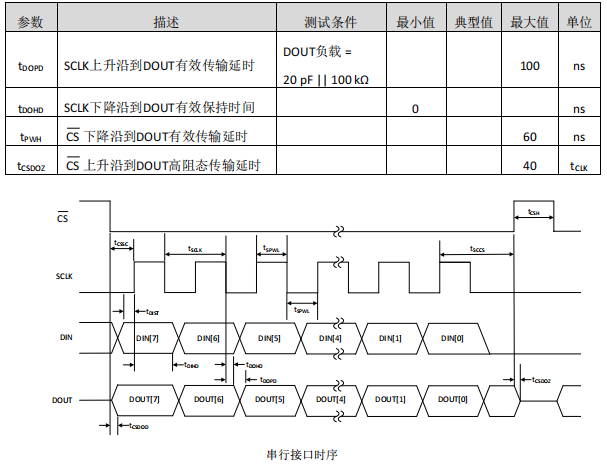

输入等效噪声和信噪比

下表给出一些转换速率和 PGA 增益设置下的 MS5583N 的信噪比和输入等效均方根噪声。

注 1: 在典型温度 25°C 和 VREF=5V。ADC 噪声积分的带宽为 0.1Hz 至 0.413X 转换速率。

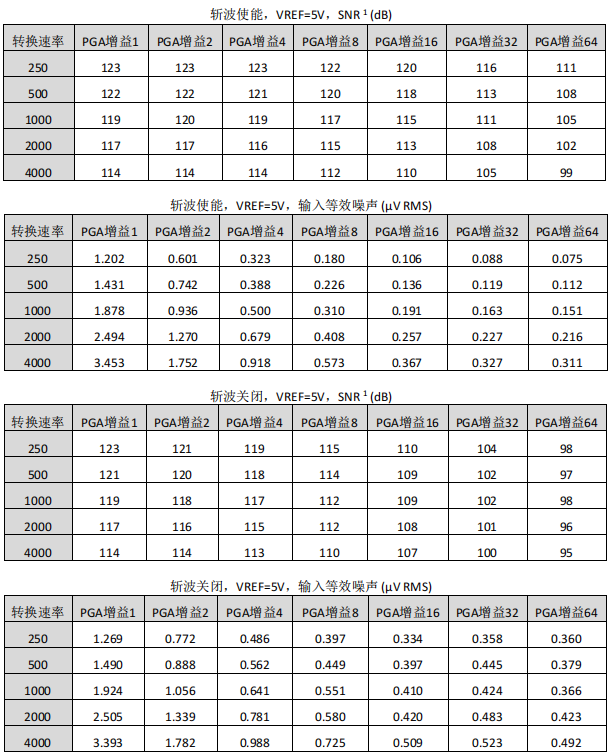

典型图表

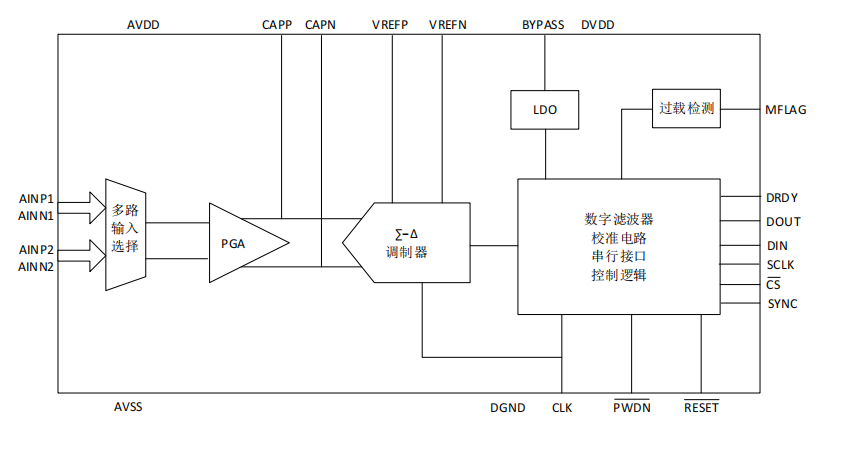

功能描述

概述

MS5583N 是一款高分辨率、低功耗的模数转换器,可广泛应用于能量检测、地震波检测等环

境。在 250SPS 到 4kSPS 转换速率下,可提供 31bit 转换精度。器件集成低噪声、高输入阻抗可变

增益放大器、输入多路选择器∑-Δ 调制器、数字滤波器和 SPI 接口。

模拟输入通道

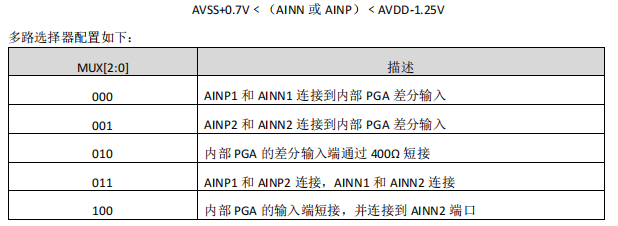

模数转换器的两路输入选择器输出到内部 PGA 的输入,通过寄存器 MUX[2:0]可以设计输入选择。

由于内部 PGA 的输入范围受限,所以外部模拟输入的输入范围如下:

模拟输入 PGA

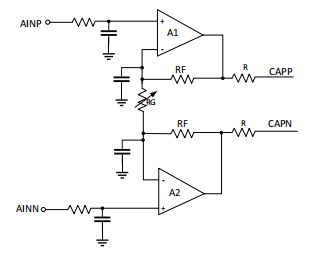

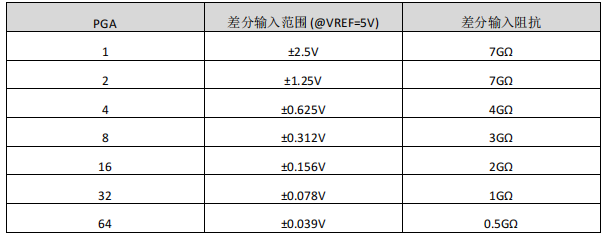

MS5583N 内部集成一个低漂移、低噪声、高输入阻抗的可编程放大器。通过寄存器 PGA[2:0],增

益可设置成 1、2、4、8、16、32 或 64 倍。

可以通过设置打开或关闭斩波,当斩波开启时,可以去除放大器的失调、失调漂移和 1/f 噪声,

PGA 输出到 CAPP 和 CAPN 端口,并连接到调制器的输入。必须连接一个 10nF 电容(或更大)到 CAPP

和 CAPN 端口,PGA 的内部示意图如下:

PGA 的输入阻抗和输入范围随着增益设置的变化而变化,具体如下:

时钟源

MS5583N 采用外部时钟。

调制器

MS5583N 内部集成 4 阶 Σ-Δ 调制器。当输入幅度过大,MFLAG 端口会输出高电平,表示调制器已

处于输入过驱状态,最小 MFLAG 信号持续时间为 fclk/8。

调制器通过开关电容采样 PGA 的输出电压,会导致一个平均输入电流和等效输入阻抗。在 CLK 时

钟为 4.096MHz 时,调制器等效输入阻抗约为 55kΩ。

偏移

MS5583N 可以通过内部寄存器 OFFSET1 和 OFFSET0,设置调制器的偏移电压为 100mV/PGA 或

75mV/PGA。

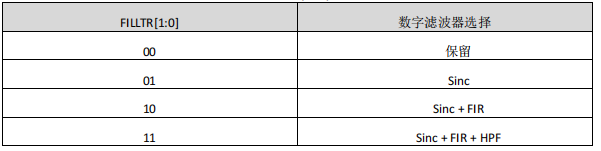

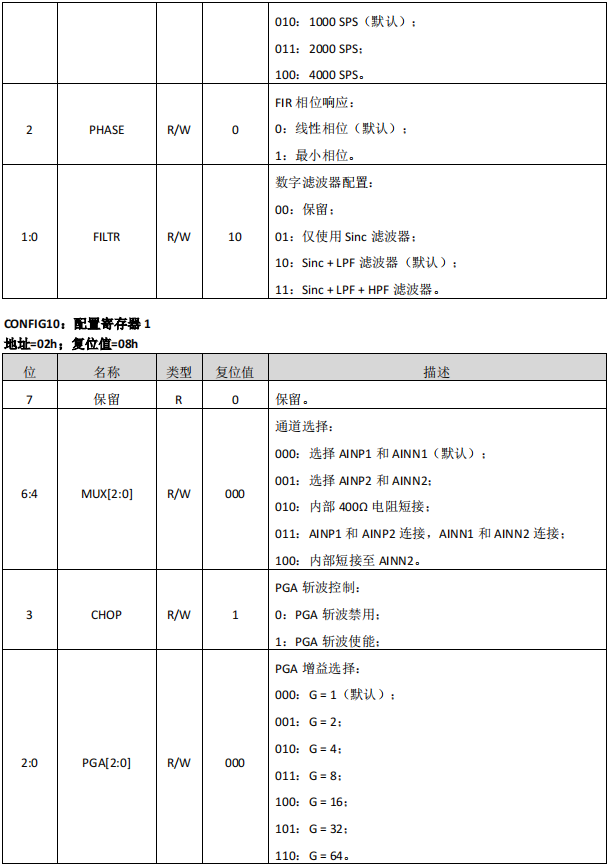

数字滤波器

可通过调整数字滤波器,权衡分辨率和转换速率。数字滤波器由三个级联滤波器组成:5 阶

Sinc 滤波器,FIR 低通滤波器以及一阶高通滤波器(HPF)。下表显示滤波器选项。

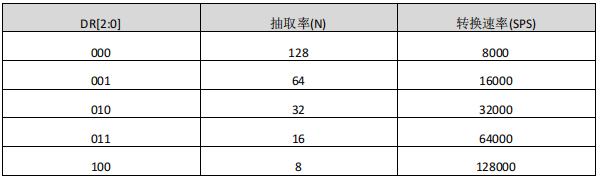

通过寄存器 DR[2:0]位,设置 Sinc 滤波器的抽取率,从而影响 ADC 数据转换速率,如下表显示。

FIR 低通滤波器可选线性相位和最小相位两种相位响应模式。在线性相位模式下,滤波器对不同频

率输入信号的延迟时间是恒定的,但是延迟和稳定时间较大。在最小相位模式下,延迟时间较小,但

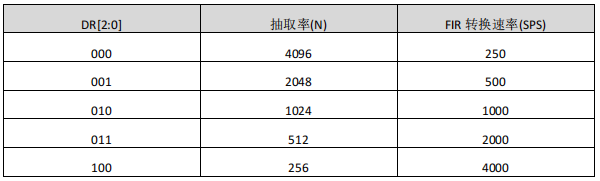

在不同频率下的延迟时间不恒定。下表列出 FIR 低通滤波器的抽取率与转换速率的关系。

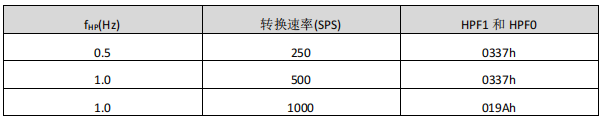

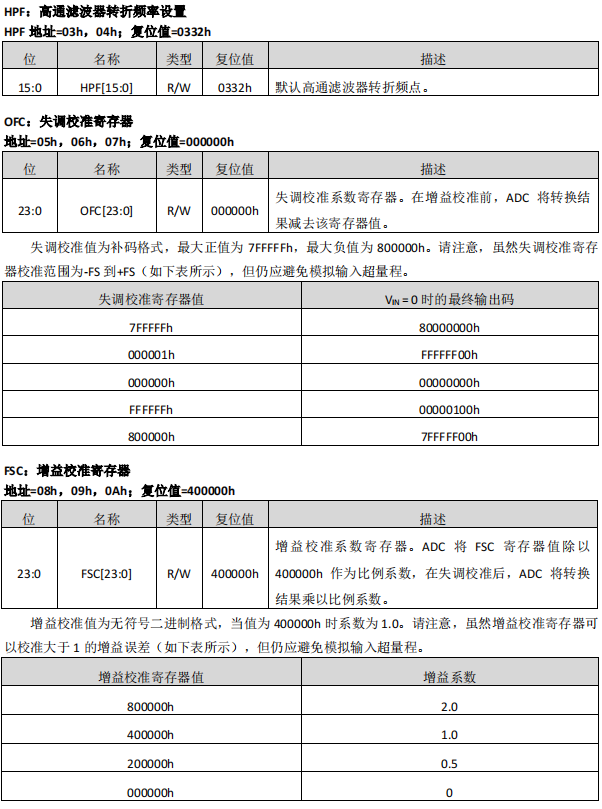

高通滤波器转折频点由寄存器 HPF1 和 HPF0 以十六进制编程。

下表列出示例值。

主时钟输入 CLK

MS5583N 外部主时钟典型输入为 4.096MHz,ADC 的转换速率随着主时钟变化。

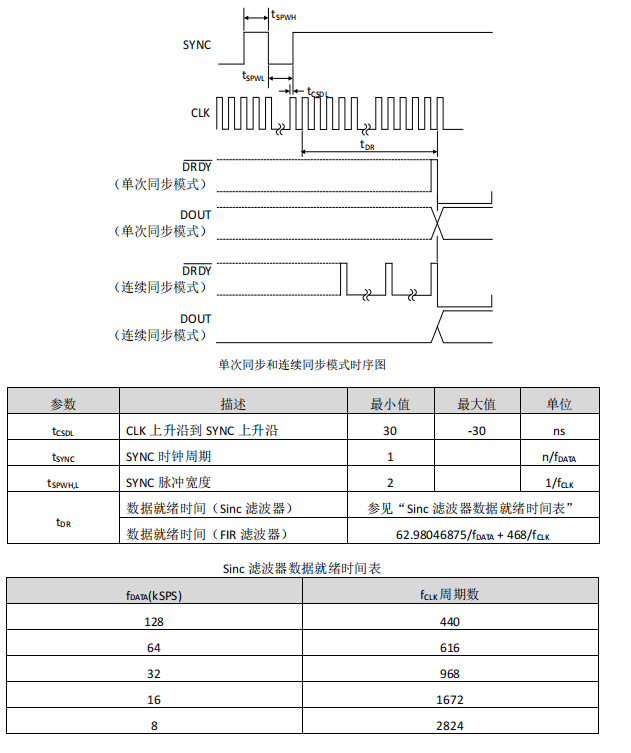

同步转换

MS5583N 可通过两种方式同步:SYNC 引脚和 SYNC 指令。芯片具有单次同步和连续同步两种模式。

在单次同步模式中,单个同步信号同步一次。在连续同步模式中,既可以通过单个同步信号进行同步,

也可以通过连续时钟输入 SYNC 引脚来同步转换,其频率为转换速率的整数倍。

单次同步模式

在单次同步模式中,当同步信号产生时,MS5583N 将停止并重启转换。新的转换数据就绪时间如

下图表所示:

连续同步模式

在连续同步模式中,可以使用单脉冲同步信号或连续时钟。当使用单脉冲同步信号时,芯片会像

单次同步模式一样重新同步。在连续同步模式下, DRDY 不受影响正常工作,DOUT 一直保持低电平,

直到 63 个 DRDY 周期后数据就绪。

输入 SYNC 引脚的连续时钟,其频率必须是转换速率的整数倍,否则芯片将重新同步。芯片将在

SYNC 第一个上升沿开始同步,在此期间,对 ADC 寄存器进行任何写操作会使芯片重新同步。重新同

步将使 SYNC 引脚上的同步控制失效。可通过在一个转换周期内,先后发送 STANDBY 和 WAKEUP 指令

来重新使能 SYNC 引脚的同步控制。

复位

MS5583N 可通过两种方式复位:将 RESET 引脚置低或发送 RESET 指令。将 RESET 引脚置低并保持

至少 2 个系统时钟周期可强制复位,在 RESET 置高前,芯片保持在复位状态。发送 RESET 指令后,芯

片将在第一个系统时钟的上升沿开始复位。

MS5583N 复位后,寄存器回到默认状态,并且芯片在系统时钟下个上升沿开始同步转换。具体时

序参见下列图表。

掉电

MS5583N 可通过将 PWDN 引脚置低且关闭 CLK 输入,进入掉电模式。当 PWDN 引脚置低时,芯片

回到默认状态,并禁用内部电路以最小化功耗。

在掉电模式中,芯片数字输入端口不允许悬空,同时输出仍然有效。

休眠

发送 STANDBY 指令且 CS 置低,发送 STANDBY 指令后,SPI 接口和寄存器仍保持活动状态。在 CS

置高后,芯片退出休眠模式。

上电

MS5583N 上电过程中,内部上电复位电路产生一个复位脉冲,可复位全部数字电路,复位时间为

2 16 个系统时钟周期。

数字接口

芯片提供兼容 SPI 的串行通信接口和数据就绪信号。

CS

CS 引脚用于激活 SPI 通信。 CS 必须在数据传输之前和 SPI 通信期间置低。当 CS 为高时,DOUT 引

脚进入高阻态,串行接口将被重置,并忽略此时的读取和写入。

将 CS 置高时,数据转换及数据就绪功能仍能继续工作。

SCLK

SCLK 用作串行通信的时钟。在 SCLK 上升沿从 DIN 输入数据,在 SCLK 下降沿从 DOUT 输出数据。

DIN

在 SCLK 上升沿从 DIN 输入数据,即使在数据被读出时,芯片也会识别写入的指令。因此,在读取

数据过程中,DIN 需要保持低电平。

DOUT

在 SCLK 下降沿从 DOUT 输出数据。

SPI 复位

可通过将 CS 引脚拉高来复位串行接口。若 SPI 空闲时间超过 64 个转换周期,芯片将会自动重置

接口。

DRDY

DRDY 引脚变低电平表示一次新的转换完成。在连续读取数据模式下,在 DRDY 下一次变低的 4 个

CLK 周期前完成读取,否则新的转换数据将会覆盖之前的数据。 DRDY 引脚变低电平后,在 SCLK 的第

一个下降沿被强制置高。即使 CS 为高时, DRDY 仍可指示新的转换已完成。

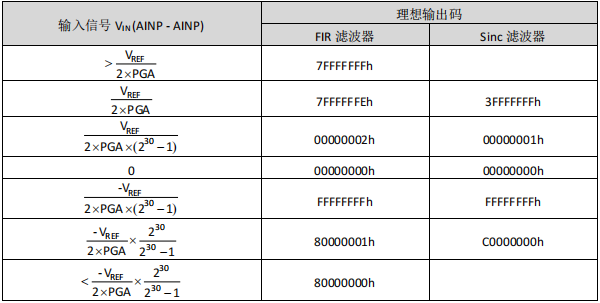

数据结构

芯片输出数据格式为 32 位二进制补码。下表为不同输入信号的理想输出码。注意在 Sinc 滤波器

模式下,输出数据缩放为 1/2。

单次转换操作

MS5583N 可使用 STANDBY 指令的软件控制方式来执行单次转换操作,以便大大降低功耗。首先,

发送 STANDBY 指令,使芯片进入休眠模式。然后,当需要转换时再发送 WAKEUP 指令,并等 DRDY 变

低,便可直接读取转换数据。最后,再发送 STANDBY 指令。每当需要转换时,即可重复上述操作。

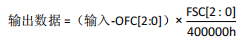

失调和增益校准寄存器

在产生最终输出码之前,可以对转换数据进行失调和增益校准。计算公式如下:

失调和增益校准寄存器的值既可以直接写入,也可以通过校准指令自动设置。不同的 PGA 设置对

应特定的失调和增益校准。因此 PGA 改变时,这些准寄存器需要重新校准。

失调校准指令

失调校准可以通过发送 OFSCAL 命令来触发。在发送指令前,需要将零输入信号施加于芯片。该

指令执行后,芯片会将 16 个转换数据平均后的值写入 OFC 寄存器。

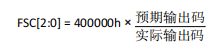

增益校准指令

增益校准可以通过发送 GANCAL 命令来触发。在发送指令前,需要将满幅输入信号施加于芯片。

该指令执行后,芯片会将 16 个转换数据平均后的值写入 FSC 寄存器。

用户校准

MS5583N 可外部计算校准值并写入校准寄存器中。步骤如下:

1. 设置 OFSCAL[2:0] = 0h,GANCAL[2:0] = 400000h。

2. 将零输入信号施加于芯片,待系统稳定后,将读取数据求平均,数据量越大越准确,然后将平均值

写入 OFC 寄存器。

3. 将满幅输入信号施加于芯片,待系统稳定后,将读取数据求平均,数据量越大越准确,而后将平均

值写入 FSC 寄存器。

增益校准值公式如下:

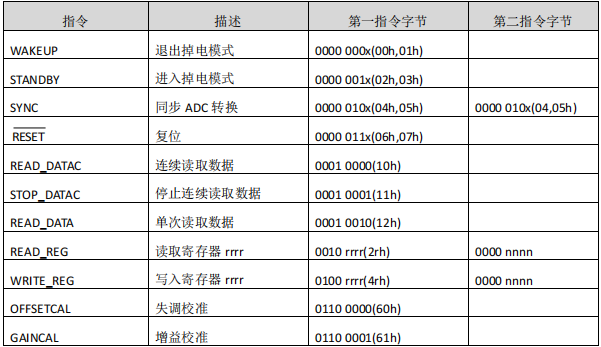

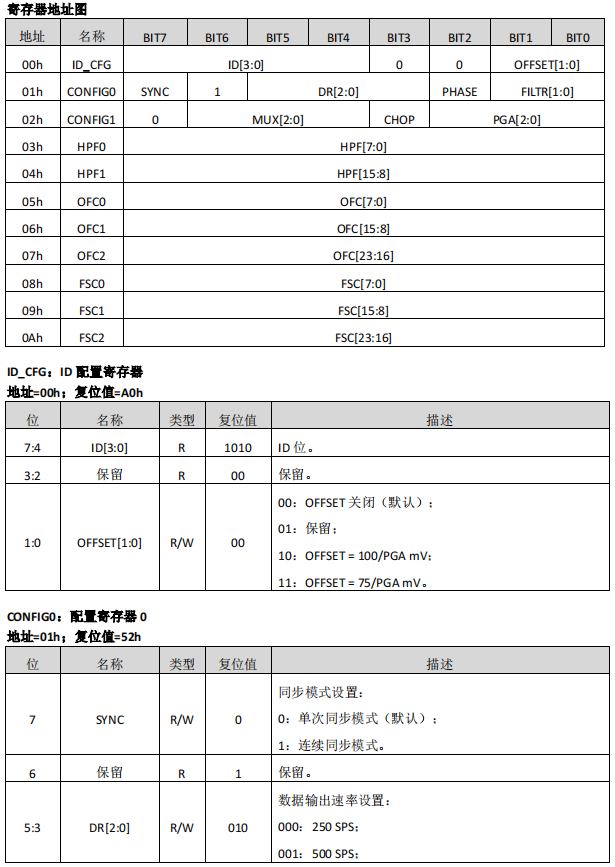

指令

可通过 13 个指令来控制芯片。其中对于芯片寄存器数据的读写指令(READ_REG 和 WRITE_REG),

需要额外的字节作为指令的一部分。发送指令期间, CS 必须保持低电平,两个指令字节之间必须间隔

24 个系统时钟周期。

1. n = 读写寄存器数 - 1;

2. r = 寄存器地址;

3. x = 任意值;

WAKEUP(0000 000x)

在执行 STANDBY 指令后,可通过 WAKEUP 指令使芯片上电。正常工作时该指令无效,因此在读取

数据时,DIN 可以保持低电平。

STANDBY(0000 001x)

发送 STANDBY 指令后,芯片进入掉电模式。 CS 置高或发送 WAKEUP 指令后,芯片退出掉电模式。

SYNC(0000 010x)

SYNC 指令会复位 ADC 并重启转换。为了同步多个 ADC,该指令必须同时发送至所有芯片。在此

命令期间,SYNC 引脚必须保持高电平。

RESET(0000 011x)

复位指令可复位所有寄存器和数字滤波器。该指令等效于 RESET 引脚。时序可参考“复位”章节。

READ_DATAC(0001 0000)

READ_DATAC 指令可使能连续读取数据模式(默认模式)。在该模式下,可直接从芯片读出转换

数据。当 DRDY 变低时,代表新数据已就绪,随后 MSB 出现在 DOUT 上,可以在 SCLK 上升沿读取数据。

DRDY 将在 SCLK 第一个下降沿回到高电平。32 位数据读取完成后,DOUT 将变低。

STOP_DATAC(0001 0001)

发送 STOP_DATAC 指令可退出连续读取数据模式,并同时进入单次读取数据模式。在该模式下,

需要通过发送 RDATA 指令来读取转换数据。发送该指令后,需等 DRDY 变为低电平,才能在 SCLK 上升

沿读取有效数据。

READ_DATA(0001 0010)

READ_DATA 指令可读取最近一次的转换结果至输出寄存器。可将 CS 置高来退出单次读取数据模

式。

READ_REG(0010 rrrr, 0000 nnnn)

通过 READ_REG 指令,可读取寄存器的数据。读取的寄存器的数量等于指令第二字节数+1。

READ_REG 指令的两字节结构如下:

1. 第一指令字节:2rh,其中 r 是第一个读取的寄存器地址;

2. 第二指令字节:0nh,其中 n = 待读取寄存器数-1。

WRITE_REG(0100 rrrr, 0000 nnnn)

通过 WRITE_REG 指令,可对寄存器写入数据。写入的寄存器的数量等于指令第二字节数+1。

WRITE_REG 指令两字节结构如下:

1.第一指令字节:2rh,其中 r 是第一个写入的寄存器地址;

2.第二指令字节:0nh,其中 n = 待写入寄存器数-1。

OFFSETCAL(0110 0000)

OFFSETCAL 指令启动失调校准。当失调校准时,模拟输入必须接至零电平。当该指令完成后,OFC

寄存器会自动更新。

GAINCAL(0110 0001)

GAINCAL 指令启动增益校准。当增益校准时,模拟输入必须设置为满幅。当该指令完成后,FSC

寄存器会自动更新。

如有需求请联系——三亚微科技 王子文(16620966594)

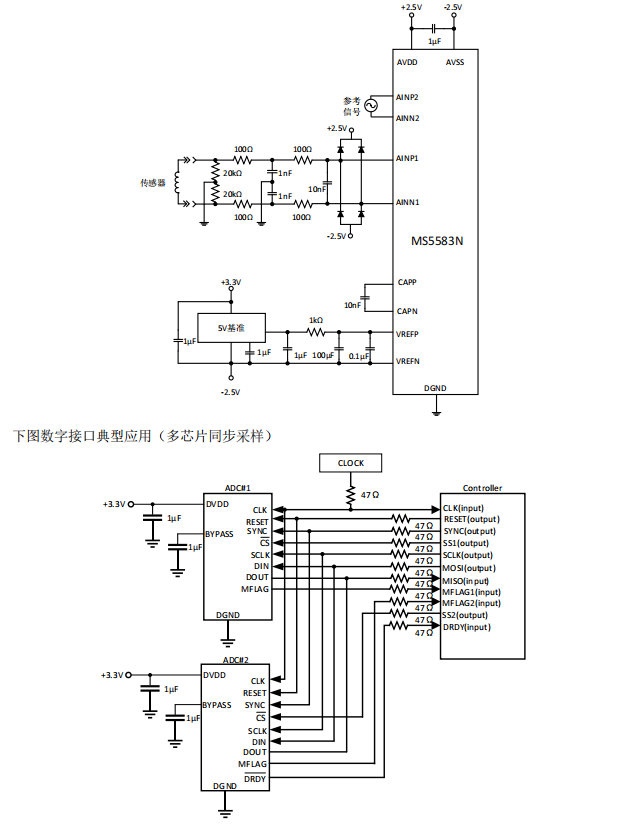

典型应用图

下图是 MS5583N 用作地震检波器应用的示意图。

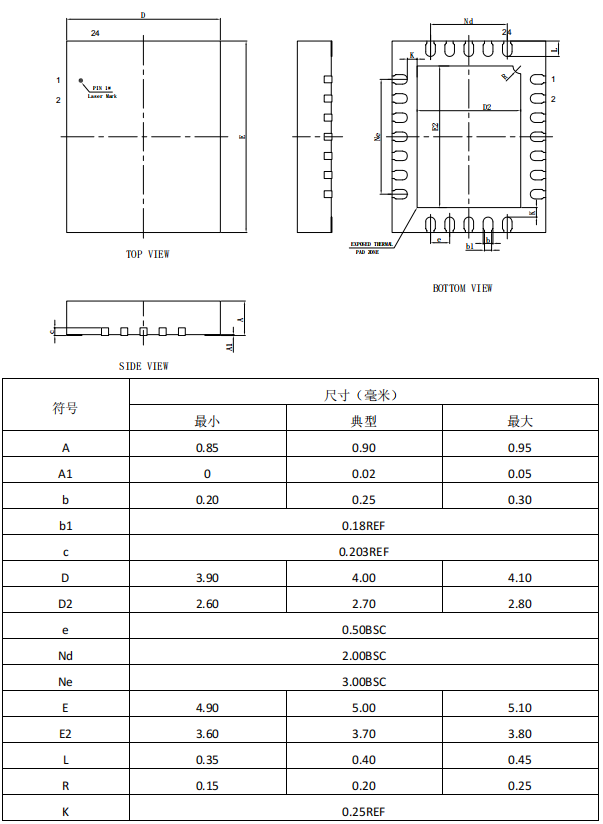

封装外形图

QFN24

——爱研究芯片的小王

审核编辑 黄宇

-

模数转换器

+关注

关注

26文章

3181浏览量

126799

发布评论请先 登录

相关推荐

MS1112——16-bit 多输入内置基准模数转换器

使用DM642 DSP和THS8200驱动器的高分辨率视频

LDC1101 1.8V高分辨率、高速电感数字转换器数据表

什么是高分辨率示波器?它有哪些优势?

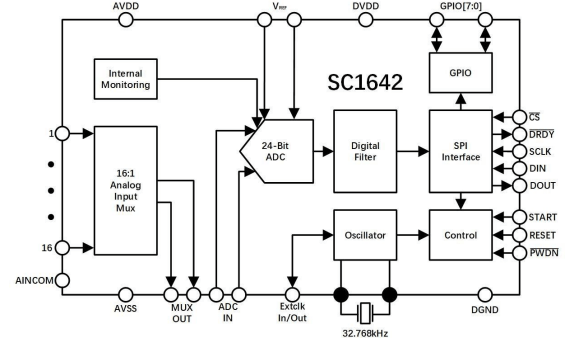

低噪声模数转换器 (ADC)SC1642,可用于温度测量系统

模数转换器的性能指标

高管洞察:高分辨率音乐需要高分辨率扬声器

高分辨率音频和普通音频之间的区别

MS5583N——高分辨率模数转换器介绍

MS5583N——高分辨率模数转换器介绍

评论