很多FPGA工程师都有这种困惑,Vivado每次编译的结果都一样吗?

在AMD官网上,有这样一个帖子:

Are Vivado results repeatable for identical tool inputs?

对大多数情况来说,Vivado编译的结果是一样的,但要保证下面的输入是一样的:

Design sources

Constraints

Tcl scripts and command sequences

Tool and command options

Vivado software version

Operating Systems

不同操作系统之间编译结果不能保证是相同的,尤其是Linux和Windows。

但下面的这些选项不能保证编译结果相同:

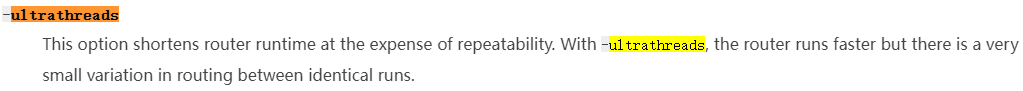

route_design -ultrathreads选项

plac_design -ultrathreads选项

使用一个routed design dcp,而且又重新跑了post-route和phys_opt_design

我们经常会设置set_param general.maxThreads,这个也是在使用ultrathreads选项时才会影响编译的repeatability。

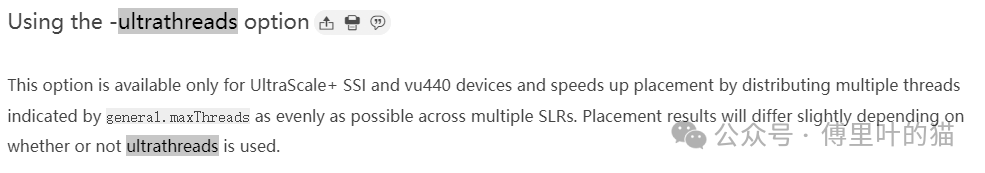

其中place_design的ultrathreads只对UltraScale+ SSI 和vu440 有效:

image-20240610145255204

route_design的ultrathreads解释如下,没有规定器件。

image-20240610145242925

定位repeatablity的问题

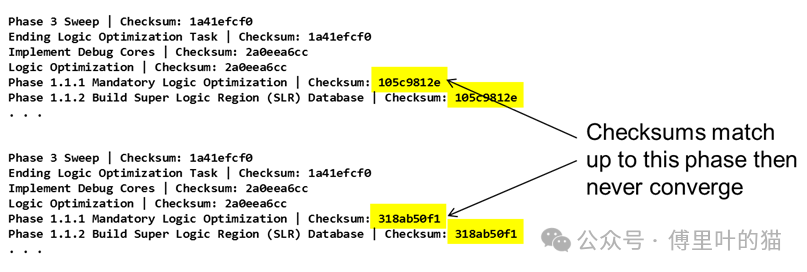

最常见的问题就是post-route结果是不一样的,我们可以通过下面的方式来确认哪一步出现是不一致。

Vivado在每个实现命令的中间阶段都会在日志中报告一个checksum,这是基于设计网表和物理数据的签名。

可以比较不同runs之间的校验和,校验和不匹配有助于确定结果在何处不一致。

image-20240610145309593

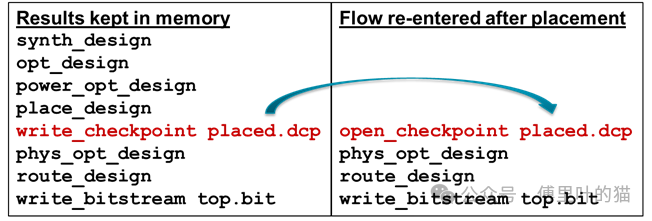

Checkpoints vs in-memory runs

对比下图中的两个流程,在place_design后,先存成dcp,另一个flow中是直接打开当前的dcp并进行后续的编译流程,这样的话,在open_checkpoint后,这两个网表的checksum可能会不同,但经过Phys_opt_design后,他们网表的checksum还是会一样的。

image-20240610145318561

总结一下,如果想让vivado的结果repeatablity,我们就只使用单线程编译:

set_paramgeneral.maxThreads1

而且保证输入的源文件、脚本、约束都是相同的。同时硬件环境也要一样,这样才能最大程度的保证结果的repeatablity。

-

编译

+关注

关注

0文章

696浏览量

35296 -

Vivado

+关注

关注

19文章

860浏览量

71428

原文标题:Vivado每次的编译结果是一样的吗?

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文详解SystemC仿真库的编译

使用Vivado 2018.2编译E203的mcs文件,遇到的问题求解

Vivado仿真之后没有出现仿真结果的解决方法

不一样的展会,不一样的精彩 2025湾芯展圆满收官

Windows系统下用vivado将电路烧写到MCU200T板载FLASH的方法

在VIVADO中对NICE进行波形仿真的小问题的解决

vcs和vivado联合仿真

FPGA开发板vivado综合、下载程序问题汇总

Nucleistudio+Vivado协同仿真教程

不一样的展会,不一样的精彩:2025湾芯展顺利收官

别蒙我,PCB板上这几对高速走线怎么看我都觉得一样!

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

想通过I2C访问闪存来测试对cy7c6541的访问,但是访问结果好像与datasheet不一样,怎么解决这个问题?

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

每次Vivado编译的结果都一样吗

每次Vivado编译的结果都一样吗

评论