高速先生成员--黄刚

Chris最近由于项目和培训都比较多,感觉每周为大家带来高速先生文档分享都有点儿力不从心了。这不在发布文章前的这个周末的下午还在发愁到底能给粉丝们带来什么有用的知识。热门而正常的高速理论感觉已经写得八九不离十了,再翻翻Chris之前做过的一些测试板后,突然找到一个不热门而很异常的理论,就趁现在吧,拿出来让大家一起品品哈!

相信大家也看过很多高速先生写的关于串扰方面的文章吧,PCB走线的串扰也是除了我们关心的损耗之外信号质量重要的影响因素,串扰的原理在以往的文章中已经描述很多了,这里就不再again and again的重复了。

可以从分立RLGC的角度来描述,请出我们的老演员1:

也可以从电磁场的角度来描述,继续请出我们的老演员2:

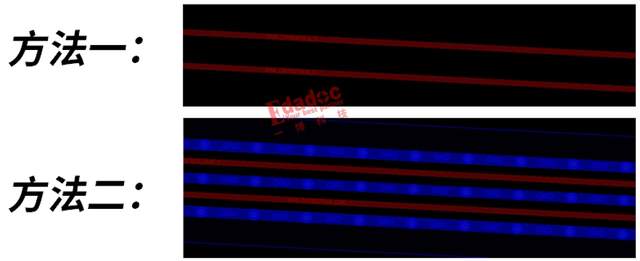

那怎么做好传输线之间串扰的PCB设计呢,尤其更加敏感的微带线串扰。参照之前写过的文章,一般会有非常有效的两个方法。那就是方法一的拉开两根信号线的间距,例如在表层的间距拉大到7H;或者方法二在两根信号线之间去做包地处理。当然也可以两个方法一起组合来用,既拉开间距又做包地处理。

当然Chris也分享了包地和不包地的串扰的差异,详细的参数可以翻翻以前这篇文章《微带线拉开7H你就觉得很稳了?》看看。

当然想做好包地设计的童鞋们还可以看看《包地就好好包,不要这么“抠门”好吗!》或者《论包地走线的定势思维》等等,在这些文章里Chris给出了包地设计的一些注意事项哈。总而言之,在间距拉开的情况下,如果还想把串扰做到极致低的话,包地设计就成为你们必须学会的点。

不知道Chris是不是一个强迫症患者,总觉得目前发现的改善串扰方法只有俩没有三,都称不上有“多种”解决方案。于是,Chris仔细端详这个串扰测试板的同时大脑飞速的运转,到底从理论上还有什么方法也可以达到在拉开一定间距的情况下进一步改善串扰的方法。从时域到频域,从路的研究方法到场的研究方法,更重要的是从上周到现在,终于想到了一个听起来有点违背SI理论,但是在Chris眼中能够圆得过去的方法。

于是二话不说,Chris立马把这个设计做到新的测试板里面去,然后回板后通过实测来验证。首先拉开间距(7H)不包地和进行包地这两个常驻嘉宾肯定要在里面了。

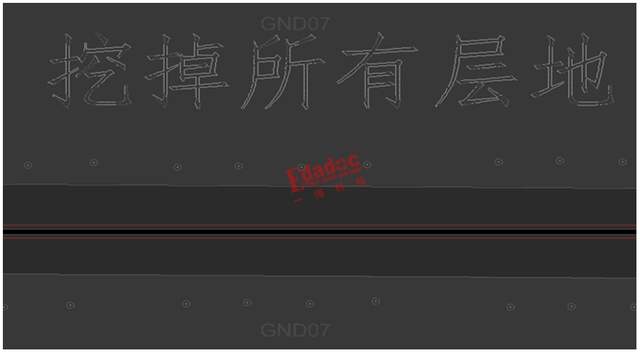

那么是不是很期待Chris想了很久的方法是怎么样的呢?不看具体设计,听起来相信大家都会觉得匪夷所思。那就是。。。把两根信号线之间的地平面挖掉不要了。

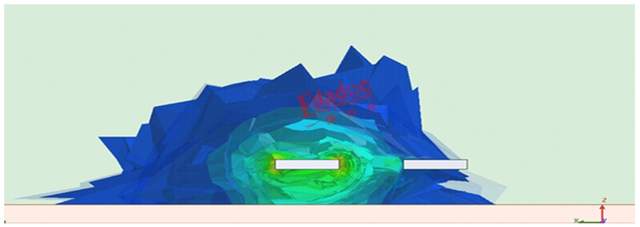

对,大家没听错,就是像下面一样,把两根信号线中间的地挖空,不要啦!

本来信号线就是要通过完整地平面的包裹才能达到回流顺畅和隔离串扰的目的,你居然还把之前完整的地平面破坏掉?这不乱搞嘛!

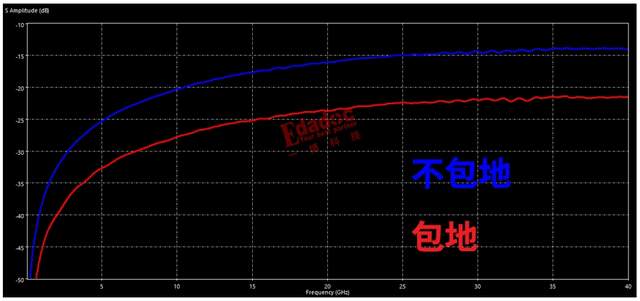

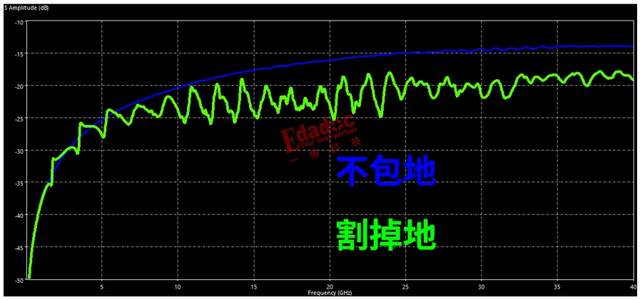

行,粉丝们倒是想看看测试结果是不是真的能把串扰减小!我们首先还是看看大家认可的包地方法和不包地之间的改善哈。

这个大家都没什么疑问,的确能看到包地后的串扰改善差不多有10个dB之多。

好啦,猪脚来了,到底Chris想了N久想出来的这种奇葩的设计方法有没有用呢?同样的,我们拿原始拉开间距不包地的设计和这个设计的实测串扰进行对比。

啊这?在比较高频居然还真有改善啊,而且改善的幅度还不止一丢丢啊!

当然,这个的确是一个非非非常规的思路,在拉开一定间距之后,然后通过一定挖空区域的设计,的确是有可能达到改善串扰的目标。值得注意的是,这个并不是真的违背SI理论的哈,它也是有一个相对比较冷门的理论去支撑的哦!

最后。。。大家想知道这个理论吗?

问题:那大家想到什么理论知识能解释这个居然能改善串扰的奇葩设计吗?欢迎大家发散思维哈!

审核编辑 黄宇

-

信号串扰

+关注

关注

0文章

15浏览量

8828 -

PCB

+关注

关注

1文章

2357浏览量

13204

发布评论请先 登录

博眼球还是真本事?参考平面不完整信号串扰反而好

QT解决串口数据接收不完整问题

怎样去解决stm32串口DMA数据接收不完整的问题呢

stm32串口DMA数据接收不完整问题说明

浅谈C语言中的三种不完整类型

如何获取ChatGPT回答不完整的内容

博眼球还是真本事?参考平面不完整信号串扰反而好

博眼球还是真本事?参考平面不完整信号串扰反而好

评论