Part 01

前言

在MOSFET中,dv/dt指的是MOSFET在开关瞬态期间,其漏源电压Vds的变化率,即漏极和源极之间电压随时间的变化速度。一般想到dv/dt,我们第一反应是高dv/dt会导致强烈的电磁干扰,影响周围的敏感电路,降低系统的信号完整性。除此之外高dv/dt还会产生另外一大危害,那就是如果dv/dt过高,漏源电压的快速变化会通过栅-漏电容Cgd耦合到栅极电压Vgs,导致栅极电压瞬时上升,从而使MOSFET在关闭的情况下误导通。接下来我们就介绍一下原因以及应对方法。

Part 02

MOS误导通的原因

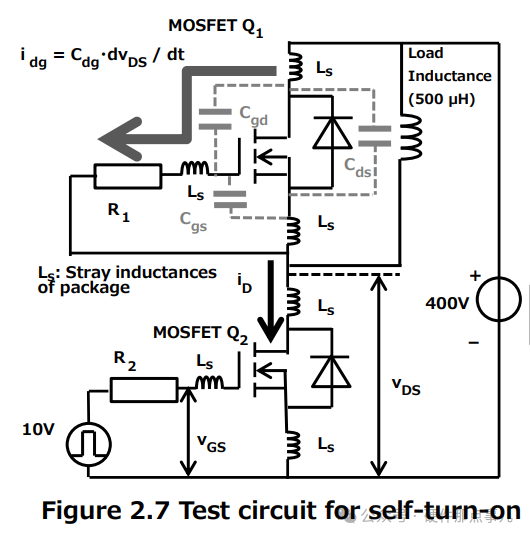

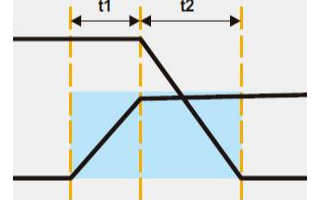

我们以DCDC电路为例,比如同步开关电源,其拓扑电路,一般是使用一组MOSFET作为上管和下管来分时开关实现稳压输出。当MOSFET高速开关时,MOSFET由导通切换到关断状态下,MOSFET的漏极和源极端子之间会产生快速上升的电压Vds。开关频率越高,对应的漏极和源极电压随时间的变化:dv/dt会越大,根据MOSFET的栅-漏极电容Cgd和栅-源极电容Cgs之间的比值会在MOS的G-S直接形成一个分压,或通过Cds流向栅极电阻R的电流会在栅极电阻两端形成一个分压,当此分压大于栅极开启电压时就会导致MOSFET自导通。

为了便于理解,我们分别分析以下两种MOS误导通模型:

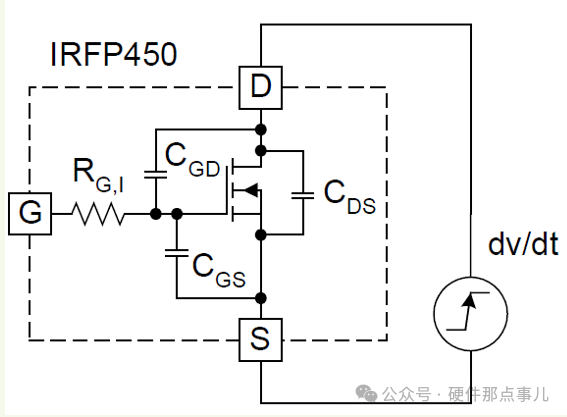

模型1:不考虑外部栅极电阻

此模型相当于MOS的栅极悬空

此时相当于Cgd和Cgs两个寄生电容串联接在Vds之间:

那么感应电压Vgs=Vds*Cgd/(Cgd+Cgs)

只有当Vds*Cgd/(Cgd+Cgs)

Vgth:MOS的开启电压

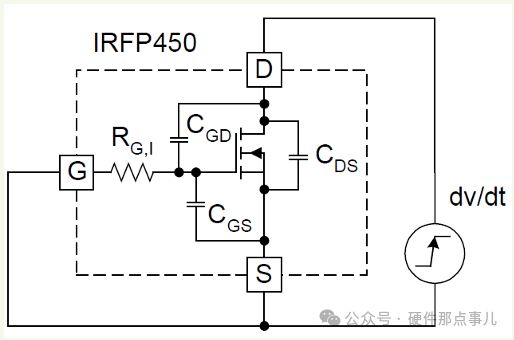

模型2:考虑外部栅极电阻

此模型相当于MOS的栅极接驱动器,驱动器输出低(我们假设驱动器输出低时的导通电阻为0)

此时相当于Cgd和Rg,i串联后接在Vds之间:

那么流经Cgd的电流为Igd=Cgd*dv/dt

栅极电压感应电压Vgs=Igd*Rg,i=Rg,i*Cgd*dv/dt

只有当Rg,i*Cgd*dv/dt

Vgth:MOS的开启电压

Part 03

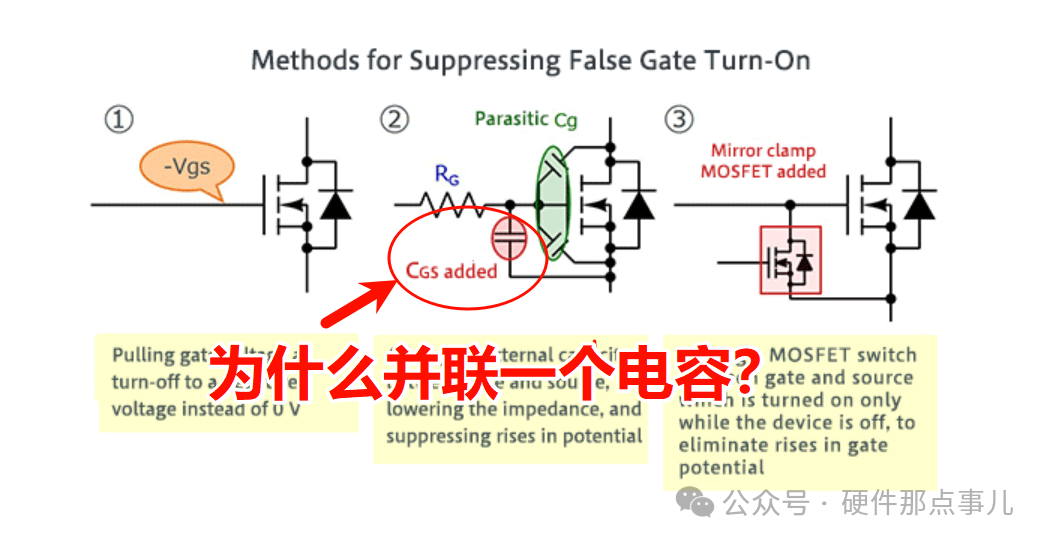

如何解决MOS误导通的问题?

基于模型1:感应电压Vgs=Vds*Cgd/(Cgd+Cgs)

我们可以通过在MOS栅源极并联电容来增大Cgs,这样相当于变相减小了Vgs,从而解决MOS误导通的问题。

2.基于模型2:感应电压Vgs=Rg,i*Cgd*dv/dt

可以通过限制dv/dt来解决此问题,如何限制dv/dt呢?可以在MOS栅极串联电阻Rg来降低MOSFET的开关速率,进而降低dv/dt。

有问题欢迎在评论区留言交流哦!

-

MOSFET

+关注

关注

147文章

7178浏览量

213386 -

电容

+关注

关注

100文章

6047浏览量

150385 -

MOS

+关注

关注

32文章

1271浏览量

93816 -

电磁干扰

+关注

关注

36文章

2316浏览量

105447

发布评论请先 登录

相关推荐

MOSFET电路栅源极GS之间为什么需要并联一个电容?居然能解决MOS误导通的问题?

MOSFET电路栅源极GS之间为什么需要并联一个电容?居然能解决MOS误导通的问题?

评论