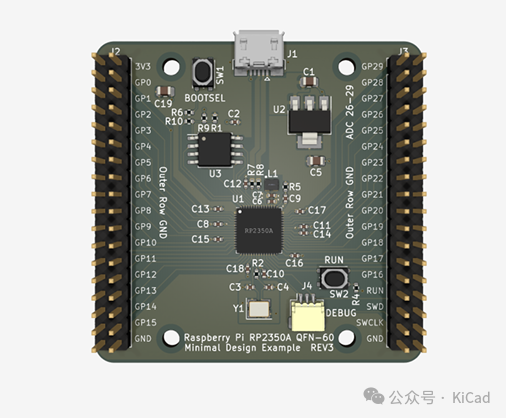

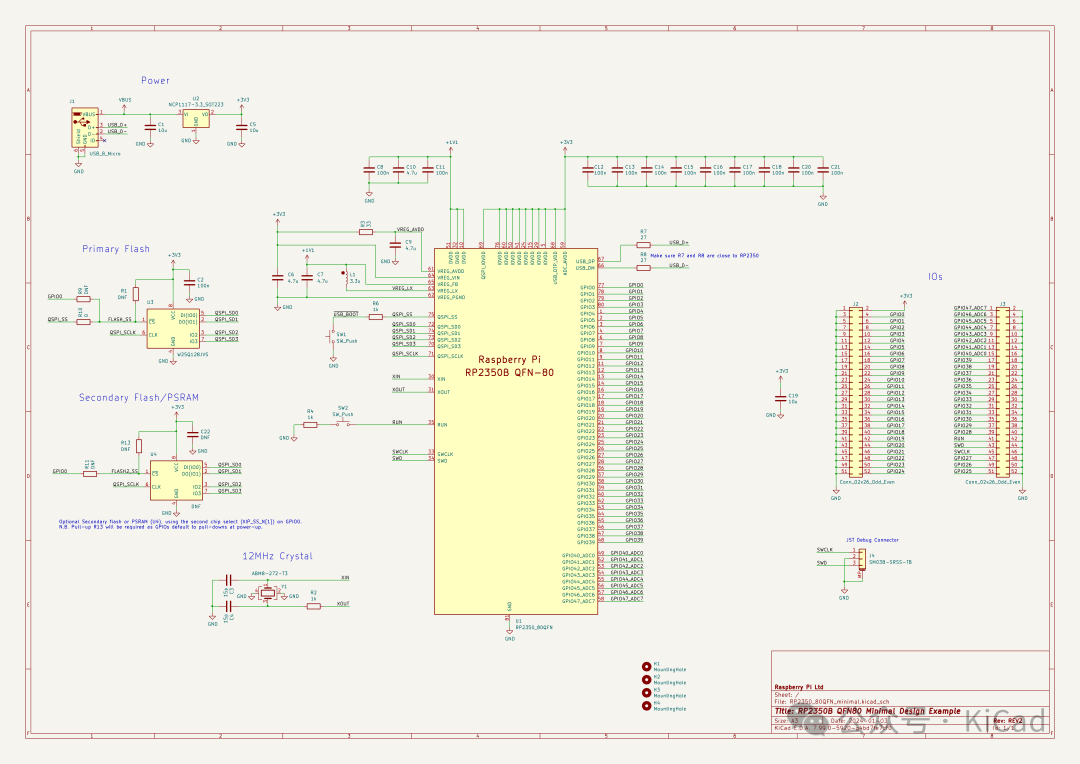

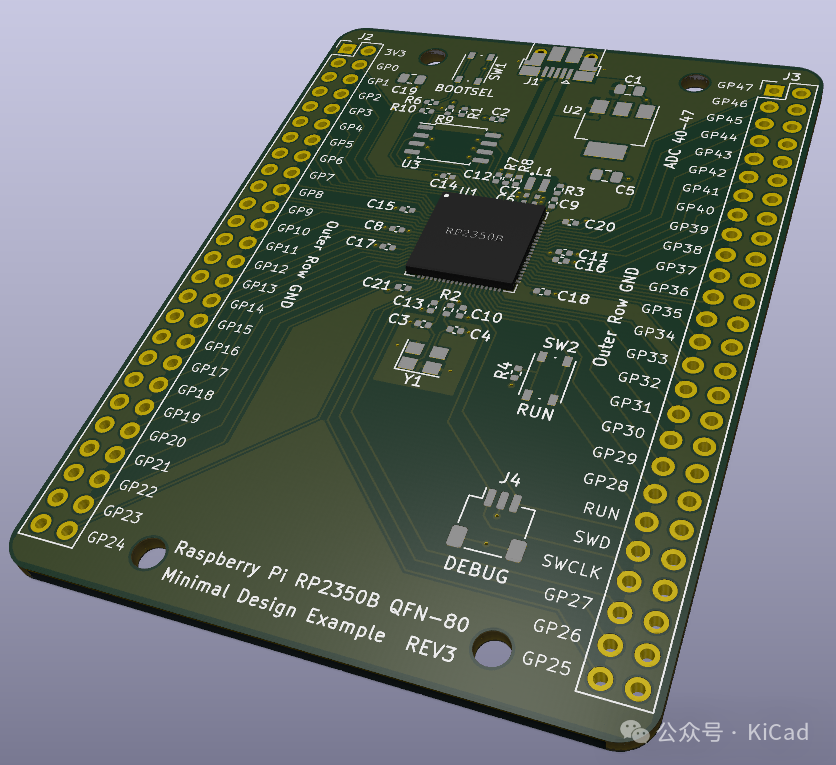

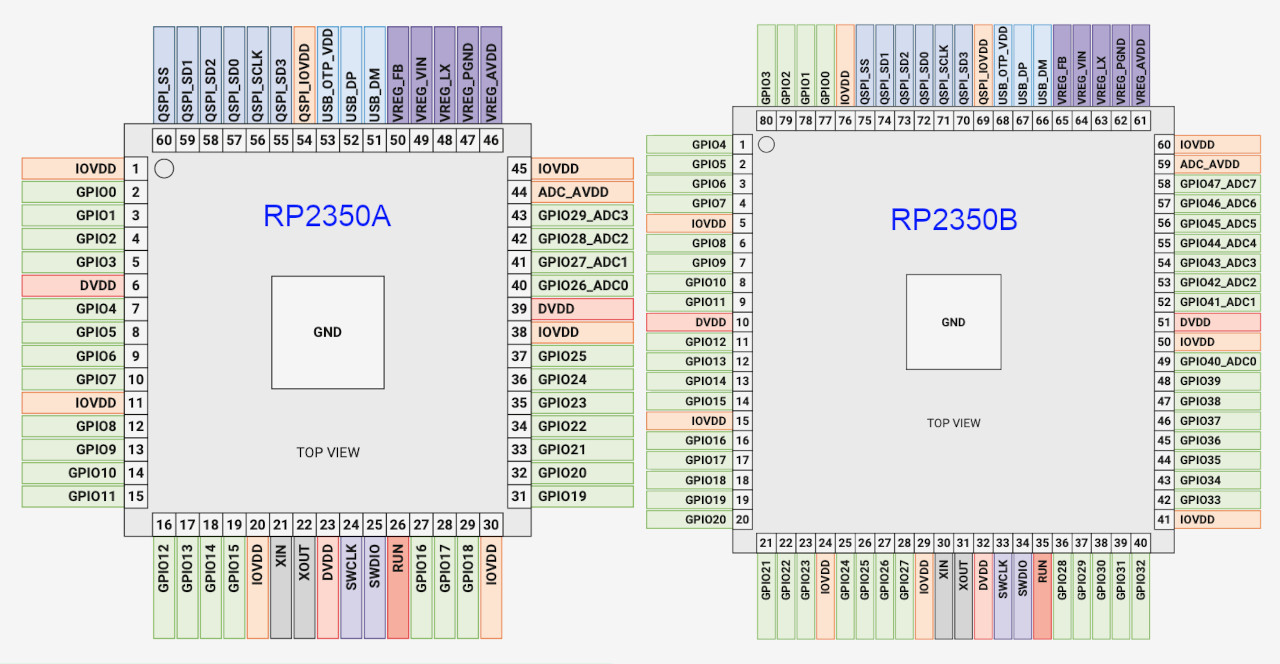

“基于 RP2350 的最小设计,有两种封装:RP2350A 采用 QFN-60 封装,RP2350B 采用 QFN-80 封装。”

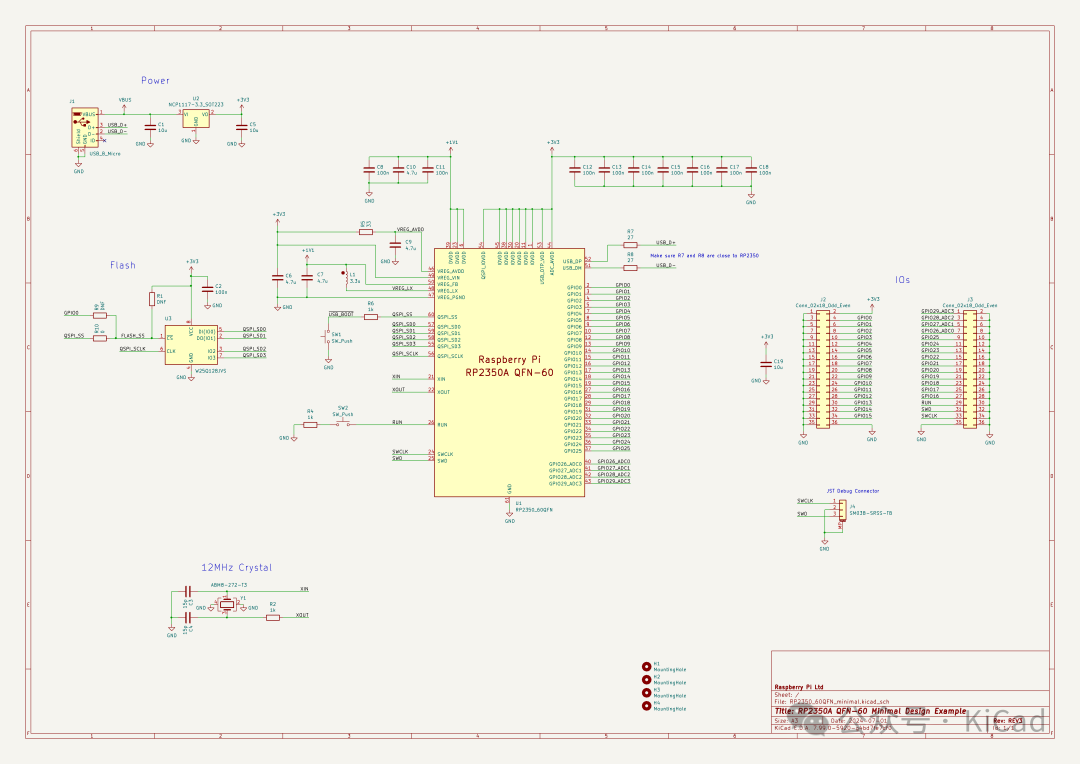

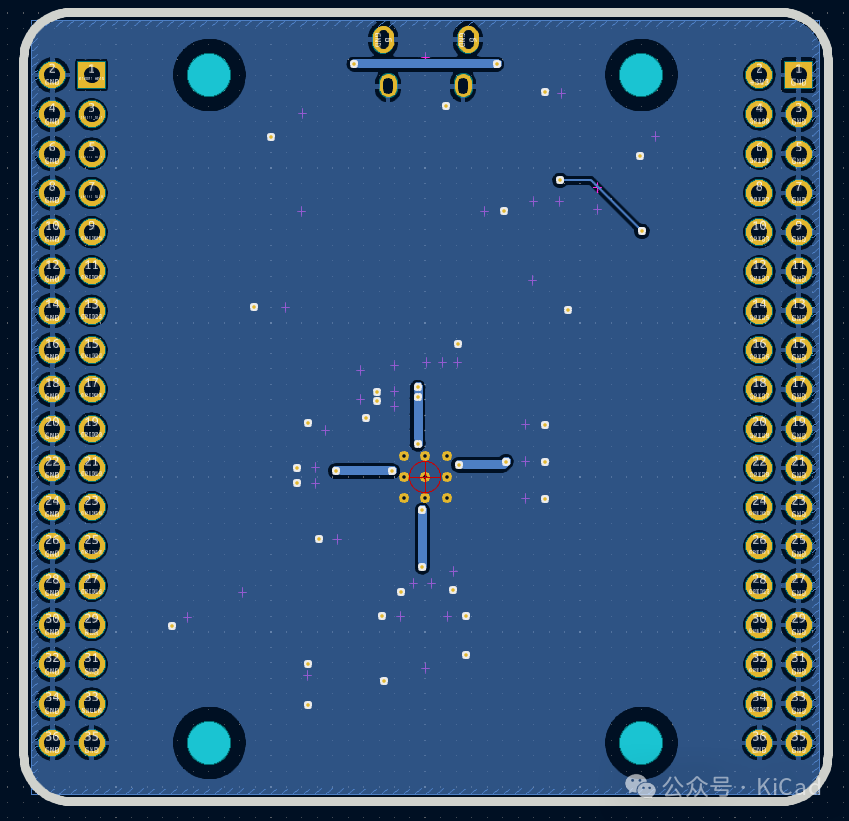

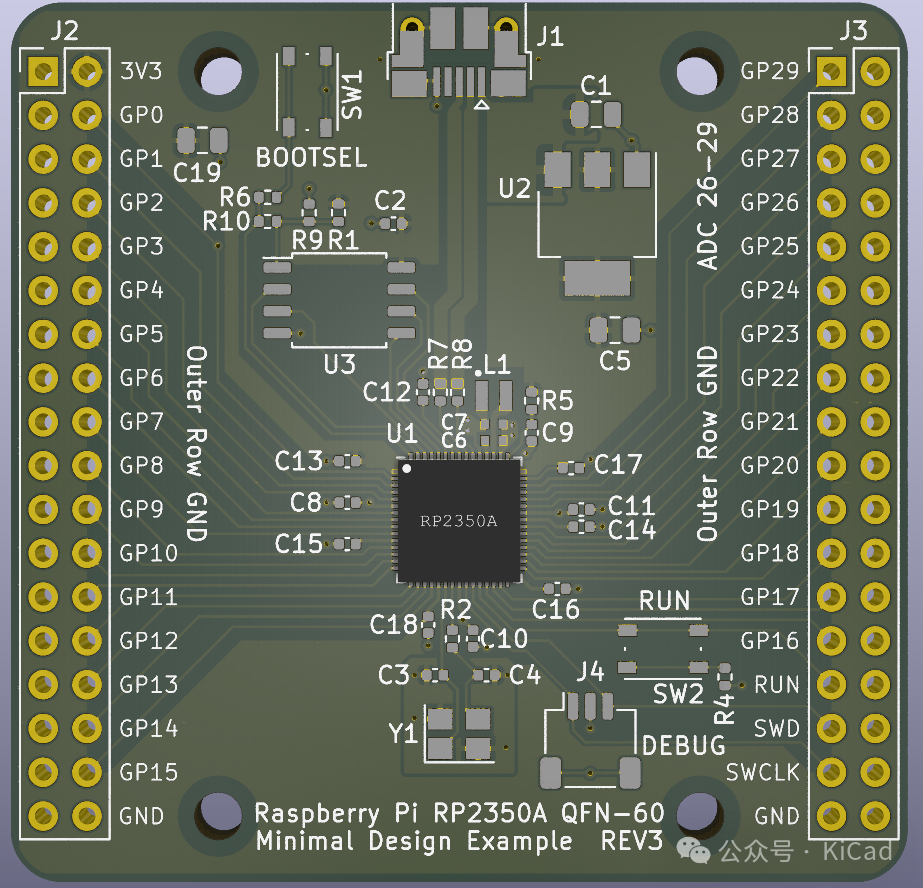

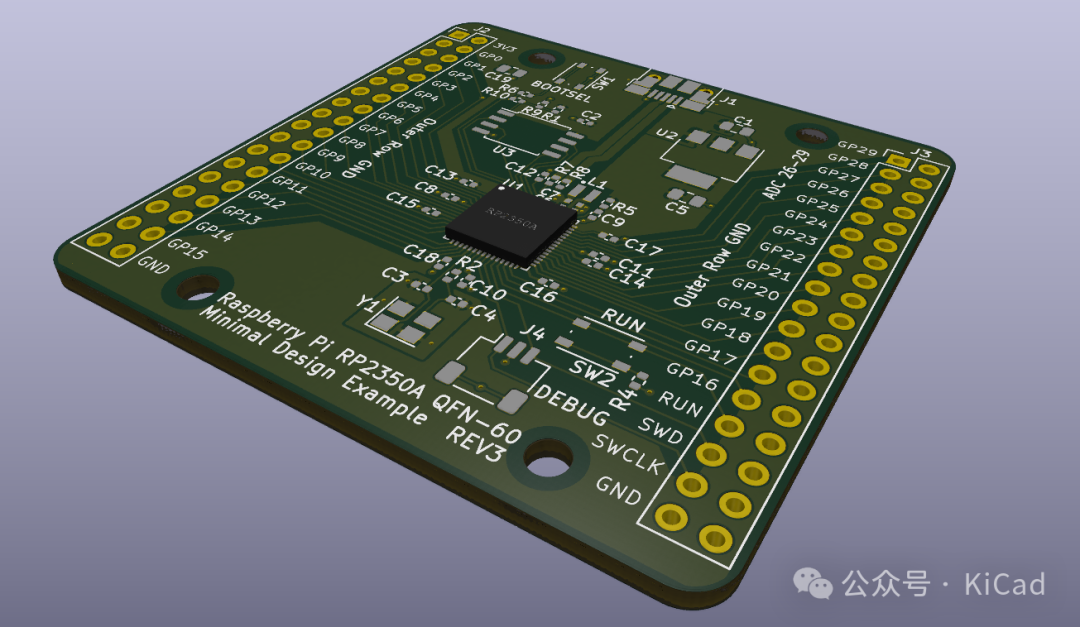

图1. RP2350A 最小系统设计

图1. RP2350A 最小系统设计

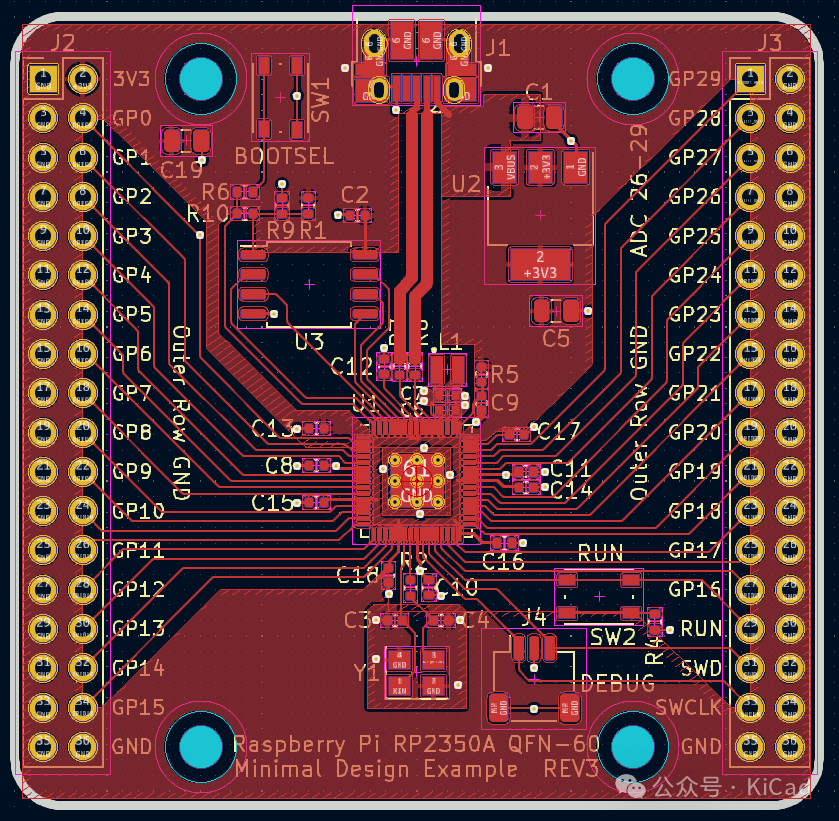

第 1 章 简介 1.1 最小系统设计 最初的最小系统旨在提供一个简单的参考设计,使用运行 RP2040 所需的最少外部器件,同时仍使所有 IO 暴露并可访问。它主要由电源(5V 转 3.3V 线性稳压器)、晶体振荡器、闪存和 IO 连接(Micro USB 接口和 GPIO 接头)组成。新的 RP235x 系列最小系统 PCB 基本相同,但由于是新硬件,需要进行一些更改。除此之外,尽管与设计的极简性质有些背道而驰,我还添加了几个用于启动和运行的按钮,以及一个单独的 SWD 接头,这意味着这次的调试体验将彻底不会那么令人沮丧。严格来说,设计并不需要这些按钮,信号仍然可以通过针座获得,如果你特别注重成本或空间,或者有受虐倾向,也可以省略这些按钮。

1.2. RP2040 与 RP235x 系列对比

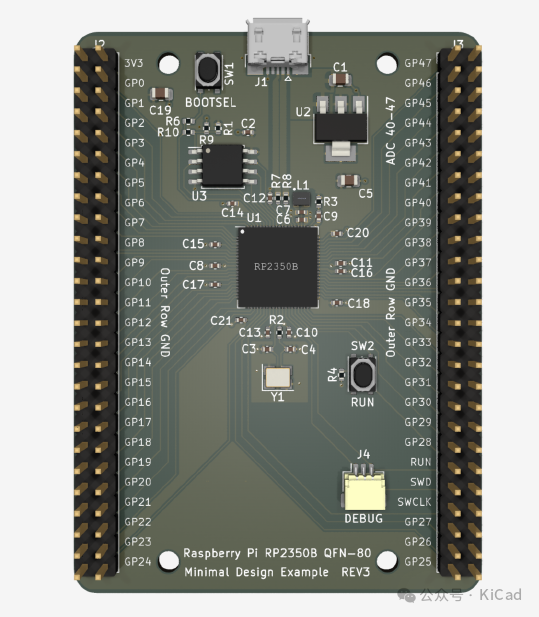

最明显的变化是封装。RP2040 采用 7x7mm QFN-56 封装,而 RP235x 系列目前有四种不同的型号。有两个器件采用相同的 QFN-60 封装:RP2350A 不带内部 Flash,而 RP2354A 自带。同样,QFN-80 也有两种封装:带 Flash 的 RP2354B 和不带 Flash 的 RP2350B。 QFN-60 器件和最初的 RP2040 有着共同的传承,共有 30 个 GPIO,其中四个具有 ADC 功能,尺寸为 7x7mm。尽管如此,RP2350A 并不能直接替代 RP2040,因为两者的引脚数量不同。 相比之下,QFN-80 芯片现在有 48 个 GPIO,其中 8 个具有 ADC 功能。因此,我们现在有两个最小系统板:一个用于 60 引脚器件,另一个用于 80 引脚器件。这些最小系统板主要是为不带内部闪存的器件(RP2350)设计的,但这些设计也可以轻松用于自带内部闪存的器件(RP2354),只需省略板载闪存,或者将其用作辅助闪存(稍后详述)。QFN-80 板有更长的针座来容纳额外的 GPIO,因此电路板更大之外,除此之外两块电路板几乎没有什么区别。

除封装外,RP235x 系列和 RP2040 在电路板上的最大区别在于电源。RP235x 系列采用了一些新的电源引脚和不同的内部稳压器。RP2040 的 100mA 线性稳压器已被 200mA 开关稳压器所取代,因此需要一些非常特殊的电路,而且在布局上也要小心谨慎。强烈建议您严格按照我们的布局和元件选择进行设计;我们已经经历了多次反复设计的痛苦,希望您不必如此。

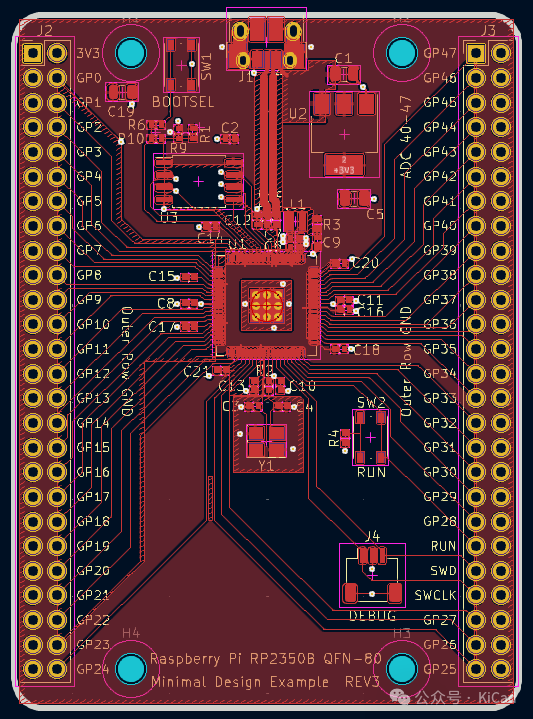

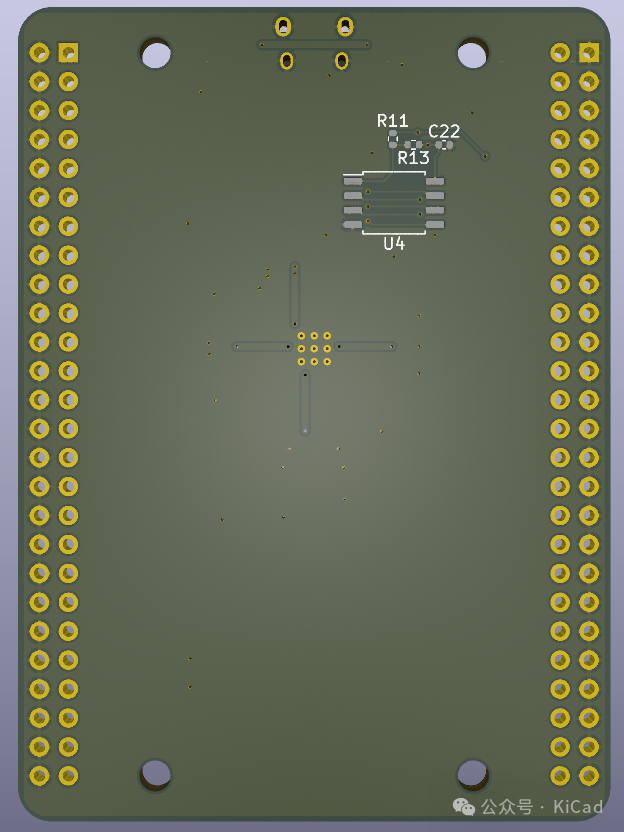

图2:2350B 最小系统设计板

1.3. 设计

最小系统设计的目的是使用 RP235x 系列创建一对简单的电路板,这些电路板应廉价且易于制造,而无需使用不必要的特殊 PCB 工艺。因此,最小系统采用两层设计,使用的元件很常见,并且全部安装在电路板的顶面。虽然使用大型、易于手工焊接的元件是件好事,但由于 QFN 芯片的间距较小(0.4 毫米),如果要使用所有 GPIO,就不可避免地要使用一些 0402(1005 公制)无源元件。虽然使用合适的烙铁手工焊接 0402 元件并不难,但如果没有专业设备,几乎不可能焊接 QFN。

在接下来的几节中,我将尝试解释辅助电路的用途,并希望解释我们是如何做出选择的。由于我实际上将讨论两种不同的设计,每种封装尺寸各一个,因此我尽量做到简单明了。在可能的情况下,两块电路板上的所有元件参考信息都是相同的,因此,如果我提到 U1、R1 等,那么它们对两块电路板都同样适用。一个明显的例外是,当元件只出现在其中一块电路板上时(在所有情况下,这都将出现在较大的 80 引脚版本上),那么相关元件将只出现在 QFN-80 设计中;例如,R13 只出现在这块电路板上。

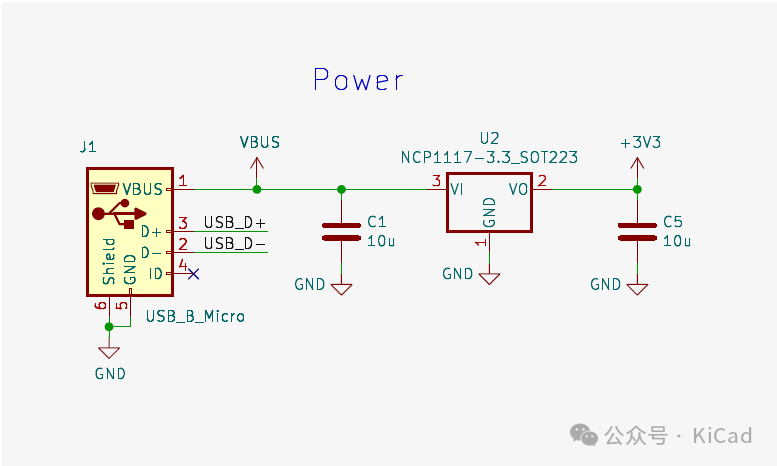

第 2 章电源

这次 RP235x 系列和 RP2040 的电源略有不同,尽管使用最简单的配置,仍然需要 3.3V 和 1.1V 两种电源。由于 RP235x 系列的性能更高,同时功耗也更大,因此 RP2040 上的线性稳压器升级为开关稳压器,这样我们就能在更大电流下实现更高的能效(最高可达 200mA,而以前只有 100mA)。

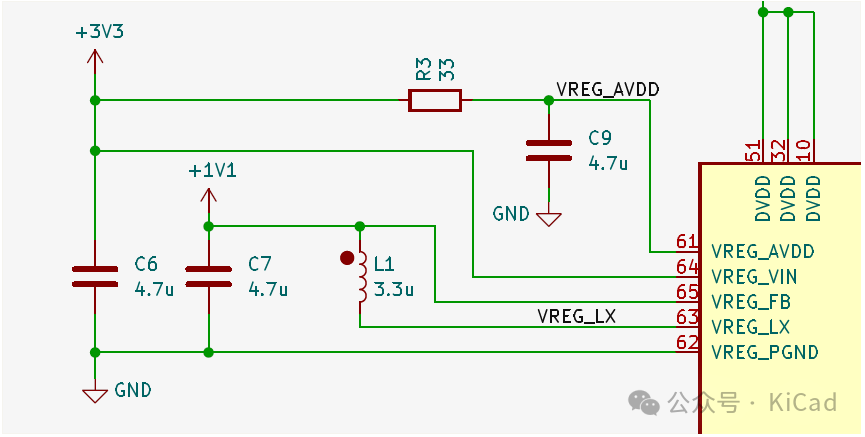

2.1新的片上稳压器

图3. 内部稳压电路

RP2040 的线性稳压器有两个引脚,3.3V 输入和 1.1V 输出,为芯片上的 DVDD 供电。这次,RP235x 系列的稳压器有五个引脚,需要一些外部元件才能工作。虽然这在实用性方面似乎有些落后,但开关稳压器的优点是在更高负载电流时更省电。 顾名思义,稳压器可快速开关连接 3.3V 输入电压(VREG_VIN)和 VREG_LX 引脚的内部晶体管,在电感器(L1)和输出电容器(C7)的帮助下,产生从输入电压降压后的直流输出电压。VREG_FB 引脚监控输出电压,并调整开关周期的开/关比例,以确保维持所需的电压。由于从 VREG_VIN 到 VREG_LX 的开关电流较大,因此需要在输入端附近安装一个大电容 (C6),这样就不会对 3.3V 电源造成太大影响。说到这些大开关电流,稳压器还带有自己的接地返回连接,即 VREG_PGND。与 VREG_VIN 和 VREG_LX 类似,该连接的布局也至关重要,虽然 VREG_PGND 必须连接到主接地端,但必须确保所有大开关电流都直接返回 PGND 引脚,而不会过多干扰其他接地端。

最后一个引脚是 VREG_AVDD,它为稳压器内部的模拟电路供电,对噪声非常敏感。

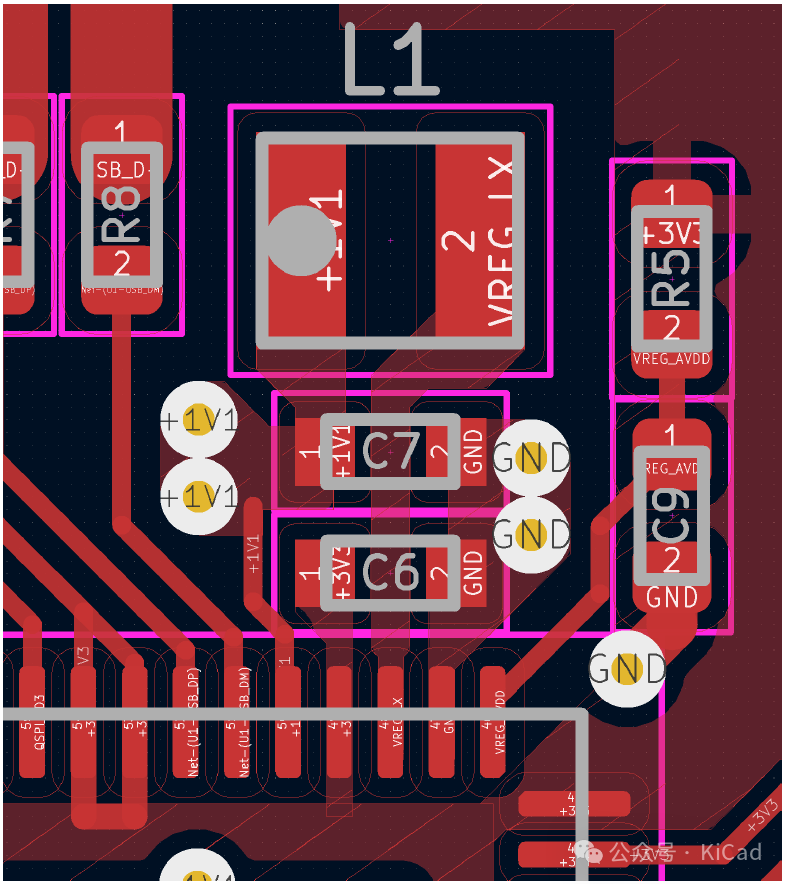

图4. 稳压电路的 PCB Layout 最小系统电路板上稳压器的布局与 Raspberry Pi Pico 2 的布局非常相似。我们在设计该电路时花费了大量心血,需要对 PCB 进行多次迭代,以尽可能使其达到最佳效果。虽然您可以以各种不同的方式放置这些元件,并使稳压器 “工作”(即产生大致合适的输出电压,足以让它运行代码),但我们发现,我们的稳压器需要以完全正确的方式处理,才能让它保持 “快乐”,我所说的 “快乐” 是指在一系列负载电流条件下产生正确的输出电压。 在进行这方面的实验时,我们有些失望地发现,物理世界的不便之处总是不容忽视。作为工程师,我们在很大程度上正是这样做的:简化元件,忽略(通常)无关紧要的物理特性,而专注于我们感兴趣的特性。例如,一个简单的电阻不仅有阻值,还有电感等。在我们的案例中,我们发现电感有磁场,而且重要的是,磁场的辐射方向取决于线圈的缠绕方式和电流的流动方向。我们还发现,“完全” 屏蔽的电感器并不像你想象的那样。磁场在很大程度上会被衰减,但仍会有一些磁场漏出。我们发现,如果电感器的 “方向正确”,稳压器的性能就会大幅提高。 原来,“方向错误” 的电感发出的磁场会干扰稳压器输出电容器 (C7),进而扰乱 RP2350 内部的控制电路。如果电感器的方向正确,并采用精确的布局和元件选择,那么这个问题就不会出现。毫无疑问,还有其他布局、元件等可以与任何方向的电感配合使用,但它们很可能会占用更多的 PCB 空间。我们提供这种推荐布局,是为了节省人们在开发和改进这种结构紧凑、性能良好的解决方案时所花费的大量工程时间。更重要的是,我们甚至可以说,如果您选择不使用我们的示例,那么风险将由您自己承担。就像我们在使用 RP2040 和晶体电路时一样,我们坚持(强烈建议)使用特定的部件(我们将在本文档的晶体部分再次这样做)。

这些小电感的方向几乎被忽视,线圈绕组的方向无法推断,而且沿着元件轴随机分布。较大尺寸的电感器外壳上通常会有极性标记,但在我们选择的 0806(2016 公制)外壳尺寸中却找不到合适的极性标记。为此,我们与 Abracon 合作生产了一种 3.3μH 元件,上面有一个圆点用于指示极性,重要的是,这种元件装在一个卷轴上,所有零件都以相同的方式对齐。分销商已经(或即将)向公众提供这些待定产品。如前所述,VREG_AVDD 电源对噪声非常敏感,因此需要进行过滤。我们发现,由于 VREG_AVDD 的电流仅约为 200μA,因此一个 33Ω 和 4.7μF 的 RC 滤波器就足以滤除噪声。

因此,概括地说,使用的元件将是

C6、C7 和 C9 - 4.7μF (公制 0402、1005)

L1 - Abracon TBD(0806,2016 公制)

R3 - 33Ω(0402,1005 公制)

RP2350 数据手册对稳压器布局建议有更详细的讨论,请参阅外部元件和 PCB 布局要求。

2.2电源输入

图5.电源输入

本设计的输入电源连接通过Micro USB 连接器(图 5 中标注为 J1)的 5V VBUS 引脚。

这是一种常见的电子设备供电方法,在这里也很合理,因为 RP2350 具有 USB 功能,我们将把它连接到该连接器的数据引脚上。由于本设计只需要 3.3V(1.1V 电源来自内部),因此我们需要降低 5V USB 电源的输入电压,在这种情况下,需要使用另一个外部稳压器,即线性稳压器(又称低压差稳压器或 LDO)。之前我曾大肆宣扬过使用高效开关稳压器的好处,因此在这里使用开关稳压器也不失为一种明智的选择,但我还是选择了简单的方式。首先,使用 LDO 几乎总是更简单。不需要计算应该使用多大的电感或多大的输出电容,布局通常也更简单明了。其次,节省每一度电并不是目的;如果是目的,我会认真考虑使用开关稳压器,你可以在 Raspberry Pi Pico 2 上找到这样做的例子。第三,我们可以借用之前在 RP2040 版本的最小系统电路板上使用的电路。这里选用的 NCP1117(U2)具有 3.3V 的固定输出电压,可广泛使用,并能提供高达 1A 的电流,足以满足大多数设计的需要。查看 NCP1117 的数据表可知,该器件的输入端和输出端分别需要一个 10μF 的电容(C1 和 C5)。

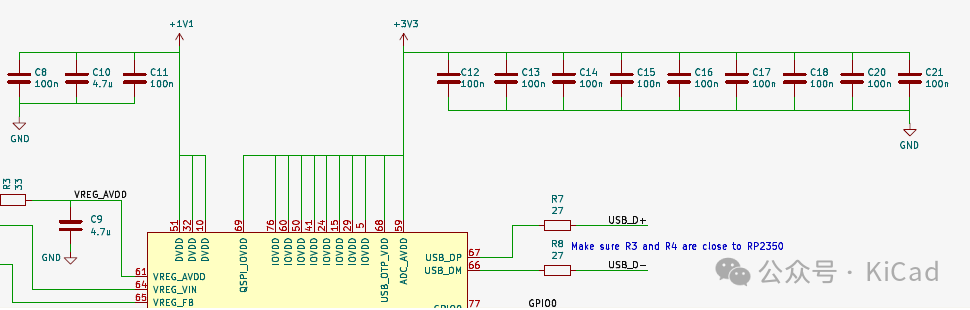

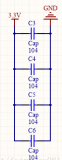

2.2.1 去耦电容

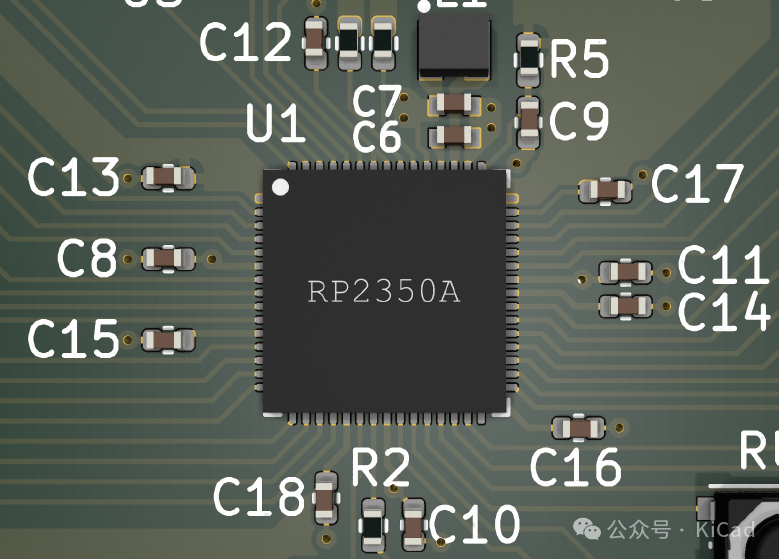

图6. RP2350 电源输入、稳压器及去耦电容

电源设计的另一个方面是 RP2350 所需的去耦电容。这些电容有两个基本功能。首先,它们能滤除电源噪声;其次,它们能提供本地电荷,供 RP2350 内部的电路在短时间内使用。这可以防止电流需求突然增加时,附近的电压下降过多。因此,在电源引脚附近放置去耦元件非常重要。通常,我们建议每个电源引脚使用 100nF 的电容,但在某些情况下,我们会偏离这一规则。

图7. RP2350布线及去耦 首先,为了给所有芯片引脚留出足够的空间,以便将信号引出器件,我们必须在去耦电容的数量上作出让步。在本设计中,RP2350A 的引脚 53 和 54(RP2350B 的引脚 68 和 69)共用一个电容器(图 7 和图 6 中的 C12),因为器件的这一侧没有太多空间,稳压器的元件和布局优先。 如果我们采用更复杂/更昂贵的技术,如更小的元件,或在上下两面都安装元件的四层印刷电路板,就能在一定程度上克服空间不足的问题。这是一种设计权衡;我们降低了复杂性和成本,但代价是去耦电容减少,电容与芯片的距离比最佳距离稍远(这会增加电感)。这可能会限制设计的最高运行速度,因为电压电源可能会因噪声过大而降到允许的最低电压以下;但对于大多数应用而言,这种权衡应该是可以接受的。

另一个偏离 100nF 规则的原因是,我们可以进一步提高稳压器的性能;我们建议 C10 使用 4.7μF 的电感,它位于稳压器芯片的另一侧。

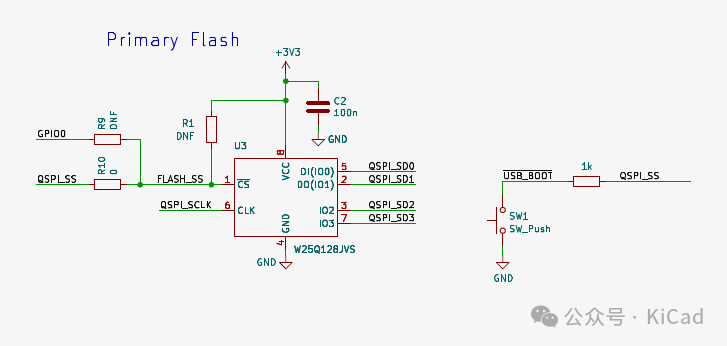

第 3 章 闪存(Flash Memory)

3.1主闪存

图8. 主闪存及 USB_BOOT 电路 为了存储 RP2350 可以启动和运行的程序代码,我们需要使用闪存,特别是四线 SPI 闪存。这里选用的是 W25Q128JVS (图8 中的 U3),一个 128Mbit 芯片(16MB)。这是 RP2350 能够支持的最大存储器容量。如果您的特定应用不需要这么大的存储容量,那么可以使用更小、更便宜的存储器。 由于这种数据总线的频率很高,而且经常使用,RP2350 的 QSPI 引脚应直接连接到闪存,使用短连接以保持信号完整性,并减少周围电路中的串扰。串扰是指一个电路网络上的信号会在相邻走线上引起不必要的电压,从而可能导致错误的发生。 QSPI_SS 信号是一个特例。它直接与闪存相连,但也有两个电阻(四个,稍后再谈)与之相连。第一个电阻(R1)是 3.3V 电源的上拉电阻。闪存要求在设备上电时,芯片选择输入与自身的 3.3V 电源引脚电压相同,否则就无法正常工作。RP2350 上电时,其 QSPI_SS 引脚会自动默认为上拉状态,但在接通电源的短时间内,QSPI_SS 引脚的状态无法得到保证。增加一个上拉电阻可确保始终满足这一要求。R1 在原理图上标注为 DNF(不要安装),因为我们发现使用这种特定的闪存设备时,外部上拉是不必要的。但是,如果使用不同的闪存,在这里插入一个 10kΩ 电阻器可能会变得很重要,因此,为了以防万一,我们将其包括在内。 第二个电阻(R6) 是一个 1kΩ 电阻,连接到标有 “USB_BOOT” 的按钮 (SW1)。这是因为 QSPI_SS 引脚被用作 “boot strap”;RP2350 会在启动序列中检查该 I/O 的值,如果发现它是逻辑 0,RP2350 就会恢复到 BOOTSEL 模式,此时 RP2350 会显示为 USB 大容量存储设备,代码可以直接复制到它上面。如果我们只是按下按钮,将 QSPI_SS 引脚拉至地,然后重置设备(例如通过拨动 RUN 引脚),RP2350 将在 BOOTSEL 模式下重新启动,而不会尝试运行闪存中的内容。这些电阻 R1 和 R6(也包括 R9 和 R10)应放置在靠近闪存芯片的位置,以避免额外的走线长度影响信号。

以上所述特别适用于没有内部闪存的 RP2350。当然,RP2354 器件内部有 2MB 闪存,因此不需要外部 U3 存储器,所以 U3 可以安全地从原理图中移除,或者干脆不装。在这两种情况下,我们仍然需要将 USB_BOOT 开关连接到 QSPI_SS,这样我们仍然可以进入 USB 启动模式。

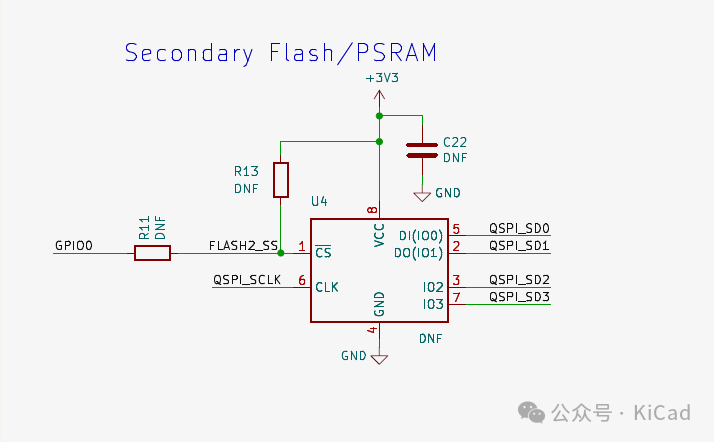

3.2辅助闪存或 PSRAM

RP235x 系列现在支持使用相同 QSPI 引脚的第二个存储设备,GPIO 提供额外的芯片选择。因此,如果我们使用的是 RP2354(具有内部闪存),那么我们可以使用 U3 作为辅助闪存,甚至可以用 PSRAM 设备替换它。为了做到这一点,我们需要断开 QSPI_SS 与 U3 的连接,而是将其连接到合适的 GPIO。最近的能够作为芯片选择的 GPIO(XIP_CS1n)是 GPIO0,因此通过从 R10 中移除 0Ω 并将其安装到 R9,我们现在可以访问 U3 以及片上闪存。为了充分利用此功能,我们有两个外部存储设备,以便无闪存的 RP2350 部件可以受益,两个最小系统板中较大的一个(用于 RP2350B)包括一个可选封装(U4)用于额外的存储芯片。

图9. 辅助闪存器件 要使用该器件,显然必须安装 R11(0Ω)和 R13(10KΩ)。添加 R11 后,GPIO0(XIP_CS1n 信号)与第二个存储器的片选相连。这次芯片选择引脚肯定需要上拉,因为 GPIO0 的默认状态是在上电时被拉低,这会导致我们的闪存设备失效。还需要使用 C22 为 U4 提供本地电源去耦。

3.3支持的闪存芯片

引导程序从闪存中提取第二阶段时使用的初始闪存探测序列是一个具有 24 位寻址的 03h 串行读取命令和一个大约 1MHz 的串行时钟。它在时钟极性和时钟相位的四种组合中反复循环,寻找有效的第二级 CRC32 校验和。 由于第二级可以使用相同的 03h 串行读取命令自由配置就地执行,因此 RP2350 可以使用任何支持 24 位寻址的 03h 串行读取的芯片(包括大多数 25 系列闪存设备)执行缓存闪存就地执行。SDK 提供了 CPOL=0 CPHA=0 的第二阶段示例,网址是: https://github.com/raspberrypi/pico-sdk/blob/develop/src/rp2350/boot_stage2/boot2_generic_03h.S 要支持使用 bootrom 中的例程对闪存编程,设备还必须响应以下命令:

02h 256 字节页面编程

05h 状态寄存器读取

06h 设置写使能锁存器

20h 4kB 扇区擦除

RP2350 还支持多种双 SPI 和 QSPI 访问模式。例如, https://github.com/raspberrypi/pico-sdk/blob/develop/src/rp2350/boot_stage2/boot2_w25q080.S 将 Winbond W25Q 系列设备配置为四线 IO 连续读取模式,其中 RP2350 发送四线 IO 地址(不带命令前缀),闪存则以四线 IO 数据响应。

对于闪存 XIP 模式,需要谨慎处理,因为闪存设备会停止响应标准串行命令,例如上述 Winbond 连续读取模式。当 RP2350 重置但闪存设备未通电循环时,这可能会导致问题,因为闪存将不会响应 bootrom 的闪存探测序列。在发出 03h 串行读取之前,bootrom 始终会发出以下固定序列,这是用于

在一系列闪存设备上停止 XIP 的最佳序列:

• CSn=1,IO[3:0]=4’b0000(通过下拉以避免竞争),×32 个时钟 • CSn=0,IO[3:0]=4’b1111(通过上拉以避免竞争),×32 个时钟 • CSn=1 • CSn=0,MOSI=1’b1(驱动为低 Z,所有其他 I/O 为高 Z),发出 ×16 个时钟

如果您选择的设备在连续读取模式下不响应此序列,则必须将其保持在每次传输都以串行命令为前缀的状态,否则 RP2350 将无法在内部重置后恢复。有关 QSPI 的更多详细信息,请参阅 RP2350 数据表中的 QSPI 内存接口 (QMI)。

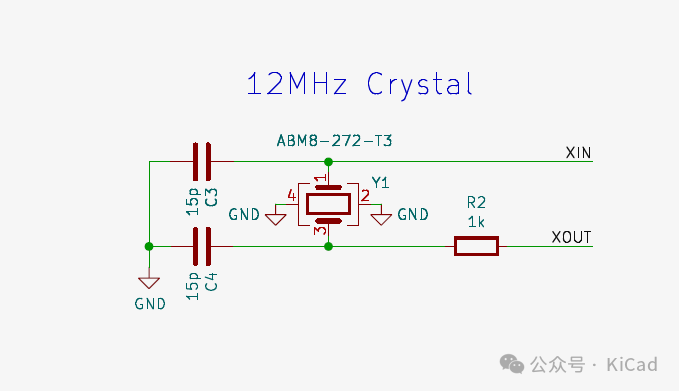

第 4 章 晶振

图10.晶振及负载电容 严格来说,RP2350 实际上不需要外部时钟源,因为它有自己的内部振荡器。但是,由于此内部振荡器的频率定义或控制不明确,因芯片而异,并且电源电压和温度也不同,因此建议使用稳定的外部频率源。如果没有外部频率源,依赖精确频率的应用就无法实现,USB 就是一个典型的例子。 提供外部频率源可以通过两种方式完成:要么通过向 XIN 引脚提供具有 CMOS 输出(IOVDD 电压的方波)的时钟源,要么使用连接在 XIN 和 XOUT 之间的 12MHz 晶振。使用晶体是这里的首选,因为它们都相对便宜且非常准确。 本设计选择的晶振是 ABM8-272-T3(图 10 中的 Y1),与 Raspberry Pi Pico 和 Raspberry Pi Pico 2 上使用的相同的 12MHz 晶振。我们强烈建议将此晶振与配套电路一起使用,以确保时钟在任何条件下都能快速启动,而不会损坏晶振本身。晶振的频率公差为 30ppm,对于大多数应用来说应该足够好了。除了 +/-30ppm 的频率公差外,它的最大 ESR 为 50Ω,负载电容为 10pF,这两者都对配套元件的选择有影响。 为了使晶振以所需的频率振荡,制造商指定了它所需的负载电容,在本例中为 10pF。该负载电容是通过将两个等值的电容器放置在晶振的两侧接地(C3 和 C4)来实现的。从晶振的角度来看,这些电容器在其两个端子之间串联连接。基本电路理论告诉我们,它们结合起来产生的电容为 (C3*C4)/(C3+C4)。由于 C3=C4,所以它就是 C3/2。在这个例子中,我们使用了 15pF 电容器,因此串联组合为 7.5pF。除了这个有意的负载电容外,我们还必须添加一个值,用于表示我们从 PCB 走线和 RP2350 的 XIN 和 XOUT 引脚获得的无意的额外电容或寄生电容。我们假设它的值为 3pF,由于这个电容与 C3 和 C4 并联,我们只需将其相加即可得到总负载电容10.5pF,这足够接近 10pF 的目标。如您所见,PCB 走线的寄生电容是一个因素,因此我们需要将它们保持在较小水平,这样我们就不会扰乱晶振并阻止它按预期振荡。尽量保持布局尽可能短。

第二个考虑因素是晶振的最大 ESR(等效串联电阻)。我们选择了最大电阻为 50Ω 的器件,因为我们发现,当使用 3.3V 的 IOVDD 电平时,这个值与 1kΩ 串联电阻 (R2) 一起,可以防止晶振过度驱动和损坏。但是,如果 IOVDD 小于 3.3V,则 XIN/XOUT 引脚的驱动电流会降低,您会发现晶振的振幅较低,甚至可能根本不振荡。在这种情况下,需要使用较小的串联电阻值。任何偏离此处显示的晶振电路或使用 3.3V 以外的 IOVDD 电平的情况都需要进行大量测试,以确保晶振在所有条件下振荡,并足够快地启动,以免给您的应用程序造成问题。

4.1推荐的晶振

对于使用 RP2350 的原始设计,我们建议使用 Abracon ABM8-272-T3。 为了在典型工作温度范围内获得最佳性能和稳定性,请使用 Abracon ABM8-272-T3。您可以直接从 Abracon 或授权经销商处购买 ABM8-272-T3。Pico 2 已针对 ABM8-272-T3 进行了专门调整。 即使您使用具有类似规格的晶体,您也需要在一定温度范围内测试电路以确保稳定性。 晶体振荡器由 IOVDD 电压供电。因此,Abracon 晶体和该特定阻尼电阻器针对 3.3V 操作进行了调整。如果您使用不同的 IO 电压,则需要重新调整。

晶体参数的任何变化都可能导致与晶体电路连接的任何组件不稳定。

第 5 章 IO

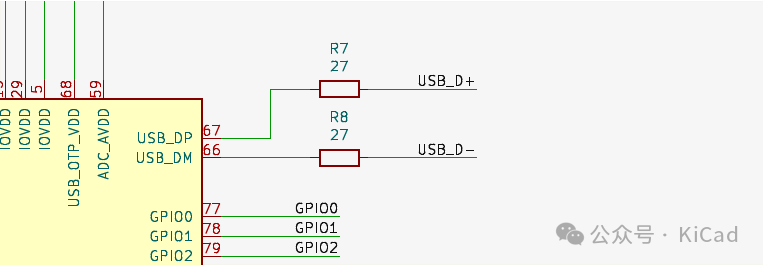

5.1USB

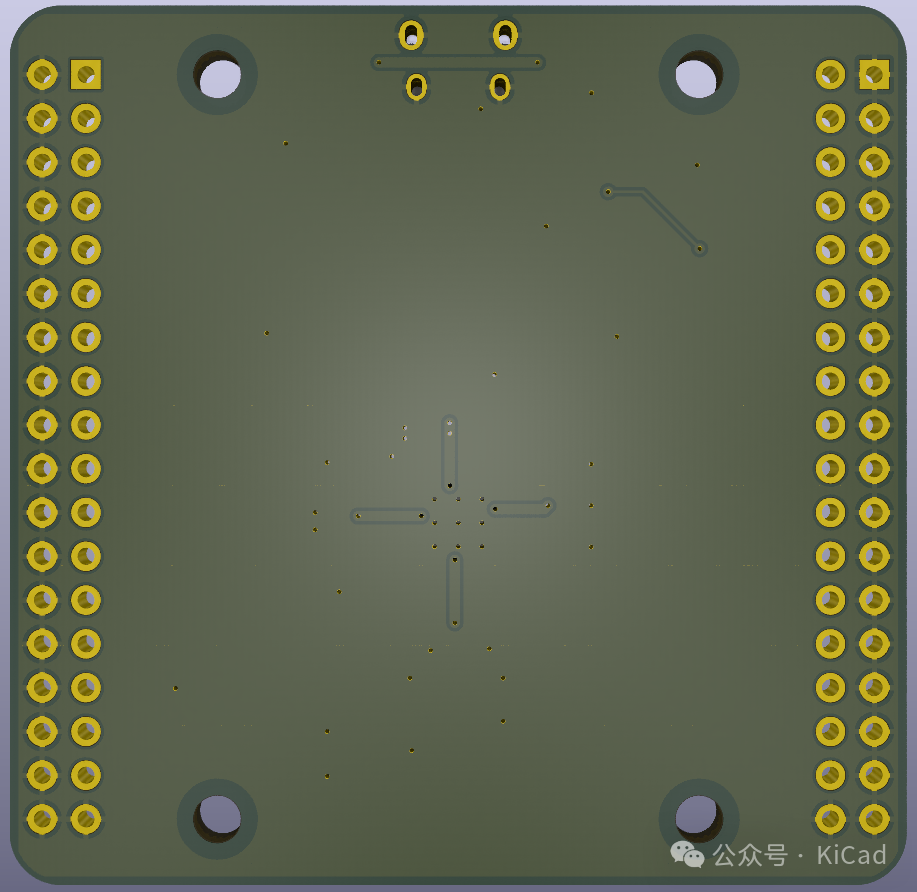

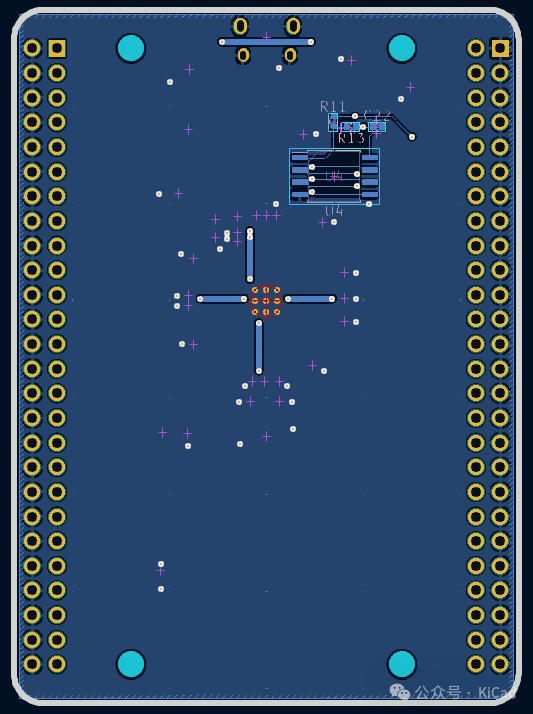

图11. RP2350 的 USB 引脚及端接电阻 RP2350 提供两个引脚,用于全速 (FS) 或低速 (LS) USB,可用作主机或设备,具体取决于所使用的软件。正如我们已经讨论过的,RP2350 也可以作为 USB 大容量存储设备启动,因此将这些引脚连接到 USB 连接器(图 5 中的 J1)是有意义的。RP2350 上的 USB_DP 和 USB_DM 引脚不需要任何额外的上拉或下拉(需要指示速度、FS 或 LS,或者它是主机还是设备),因为这些引脚内置在 I/O 中。但是,这些 I/O 确实需要 27Ω 串联端接电阻(图 11 中的 R7 和 R8),放置在靠近芯片的位置,以满足 USB 阻抗规范。 尽管 RP2350 的数据速率被限制在全速 (12Mbps),我们还是应该尝试确保传输线 (连接芯片和连接器的铜走线) 的特性阻抗接近 USB 规格的 90Ω (差分测量)。在厚度为 1mm 的电路板上,如果我们在 USB_DP 和 USB_DM 上使用 0.8mm 宽的走线,它们之间的间隙为 0.15mm,我们应该得到大约 90Ω 的差分特性阻抗。这是为了确保信号能够尽可能干净地沿着这些传输线传输,最大限度地减少可能降低信号完整性的电压反射。为了使这些传输线正常工作,我们需要确保这些线的正下方是地线。一个完整、不间断的接地敷铜区域,延伸到整个走线的长度。在这个设计中,几乎整个底部铜层都用于接地,并且特别注意确保 USB 走线只经过地平面。如果您选择厚度超过 1mm 的 PCB,那么我们有两个选择。我们可以重新设计 USB 传输线,以补偿走线和地平面之间的距离;或者我们可以忽略它,并希望获得最好的结果。

图11. RP2350 的 USB 引脚及端接电阻 RP2350 提供两个引脚,用于全速 (FS) 或低速 (LS) USB,可用作主机或设备,具体取决于所使用的软件。正如我们已经讨论过的,RP2350 也可以作为 USB 大容量存储设备启动,因此将这些引脚连接到 USB 连接器(图 5 中的 J1)是有意义的。RP2350 上的 USB_DP 和 USB_DM 引脚不需要任何额外的上拉或下拉(需要指示速度、FS 或 LS,或者它是主机还是设备),因为这些引脚内置在 I/O 中。但是,这些 I/O 确实需要 27Ω 串联端接电阻(图 11 中的 R7 和 R8),放置在靠近芯片的位置,以满足 USB 阻抗规范。 尽管 RP2350 的数据速率被限制在全速 (12Mbps),我们还是应该尝试确保传输线 (连接芯片和连接器的铜走线) 的特性阻抗接近 USB 规格的 90Ω (差分测量)。在厚度为 1mm 的电路板上,如果我们在 USB_DP 和 USB_DM 上使用 0.8mm 宽的走线,它们之间的间隙为 0.15mm,我们应该得到大约 90Ω 的差分特性阻抗。这是为了确保信号能够尽可能干净地沿着这些传输线传输,最大限度地减少可能降低信号完整性的电压反射。为了使这些传输线正常工作,我们需要确保这些线的正下方是地线。一个完整、不间断的接地敷铜区域,延伸到整个走线的长度。在这个设计中,几乎整个底部铜层都用于接地,并且特别注意确保 USB 走线只经过地平面。如果您选择厚度超过 1mm 的 PCB,那么我们有两个选择。我们可以重新设计 USB 传输线,以补偿走线和地平面之间的距离;或者我们可以忽略它,并希望获得最好的结果。

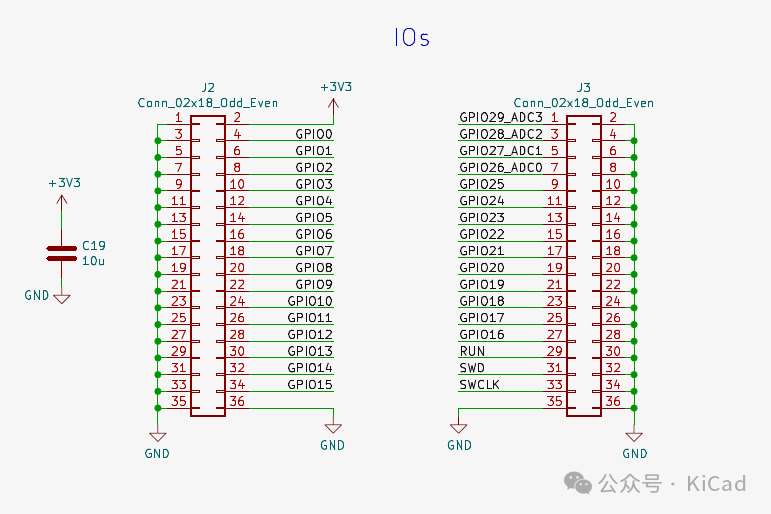

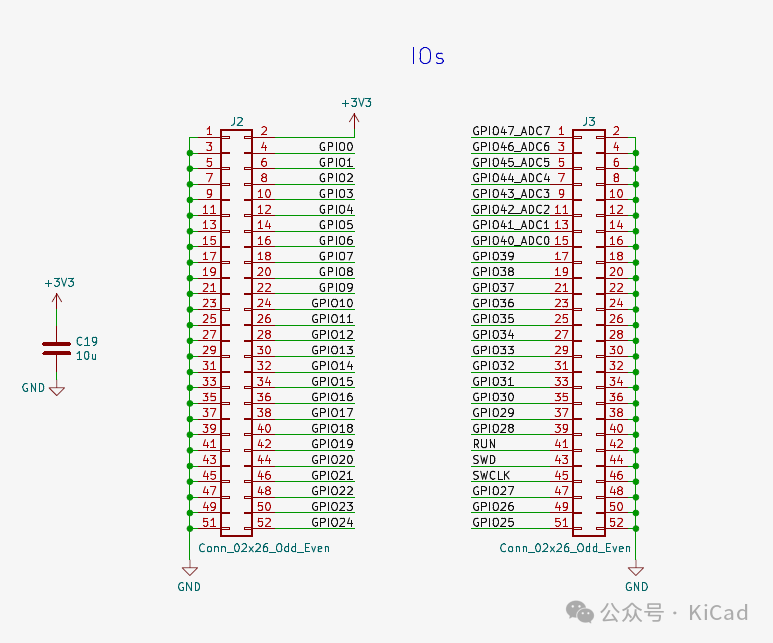

5.2IO 接头

图12. QFN60 版本的 2.54 mm I/O 接头 除了已经提到的 USB 连接器外,还有一对双排 2.54 毫米接头(图 12 中的 J2 和 J3),分别位于电路板的两侧,其余的 I/O 都已连接到这些接头。RP2350A 上有 30 个 GPIO,而 RP2350B 上有 48 个 GPIO,因此此版本的 最小系统电路板上的接头更大,以容纳额外的引脚(参见图 13)。 由于这是一个通用设计,没有考虑特定的应用,因此 I/O 可以根据用户的需要进行连接。每个接头的内排引脚为 I/O,外排引脚全部接地。良好的做法是在 I/O 连接器上包含许多地线。这有助于保持低阻抗接地,并为进出 I/O 连接的电流提供大量潜在的返回路径。这对于最大限度地减少电磁干扰非常重要,因为快速切换信号的回流可能会通过较长的环路路径来完成电路。

两个接头位于同一个 2.54 毫米网格上,这使得将该板连接到其他设备(例如面包板)更加容易。您可能需要考虑只安装单排接头而不是双排接头,省去外排接地连接,使其更方便安装到面包板上。

图13. QFN80 版本的 2.54 mm I/O 接头

图13. QFN80 版本的 2.54 mm I/O 接头

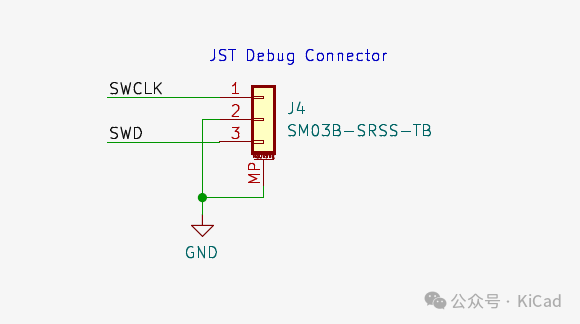

5.3调试接头

图14. 用于 SWD 调试的 JST 连接器 对于片上调试,您可能希望连接到 RP2350 的 SWD 接口。SWD 和 SWCLK 这两个引脚位于 2.54mm 接头 J3 上,方便您选择连接调试探针。除此之外,还提供了一个可选的 JST 接头,可以方便地连接到 Raspberry Pi 调试探针。如果你打算调试软件,你不需要使用这个,2.54 毫米接头就足够了,但我觉得这样做更方便。我选择了水平连接器,主要是因为我喜欢它的外观,即使它不在电路板的边缘,但也有垂直连接器,只是封装略有不同。

图14. 用于 SWD 调试的 JST 连接器 对于片上调试,您可能希望连接到 RP2350 的 SWD 接口。SWD 和 SWCLK 这两个引脚位于 2.54mm 接头 J3 上,方便您选择连接调试探针。除此之外,还提供了一个可选的 JST 接头,可以方便地连接到 Raspberry Pi 调试探针。如果你打算调试软件,你不需要使用这个,2.54 毫米接头就足够了,但我觉得这样做更方便。我选择了水平连接器,主要是因为我喜欢它的外观,即使它不在电路板的边缘,但也有垂直连接器,只是封装略有不同。

5.4按键

最小系统设计包含不止一个按钮,而是两个,而 RP2040 版本则没有。一个按钮用于选择 USB 启动,正如我们之前讨论过的,但第二个按钮是“重置”按钮,连接到 RUN 引脚。这两个按钮都不是必需的(但如果需要 USB 启动模式,则必须用接头或类似物替换 BOOTSEL 按钮),如果担心空间或成本,可以将其移除,但它们无疑使使用 RP2350 的体验更加愉快。

原理图 & PCB

RP2350A

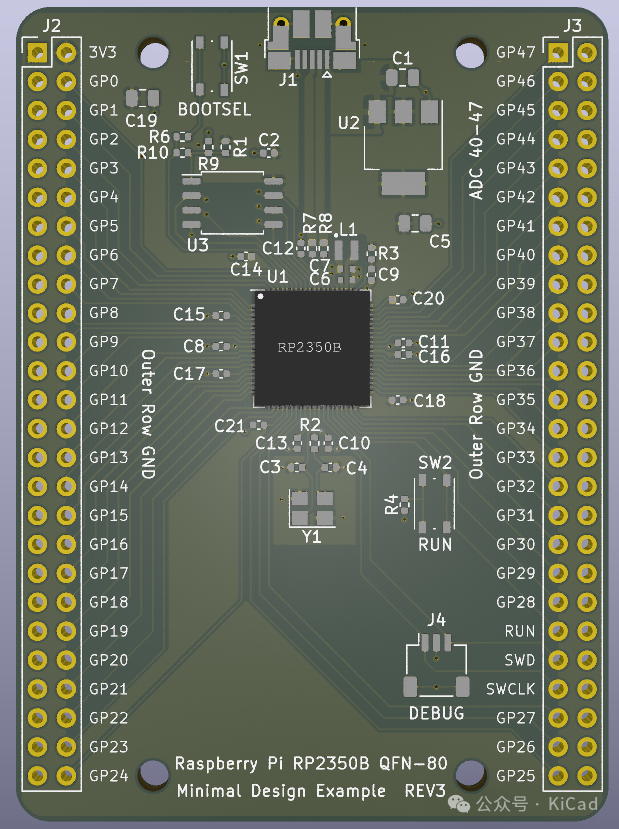

RP2350B

RP2350B

License

N/A 内容引用自 Raspberry官方数据手册

仓库 & 下载

Baidu 下载:

注意:如果想第一时间收到 KiCad 内容推送,请点击下方的名片,按关注,再设为星标。

常用合集汇总:

和 Dr Peter 一起学 KiCad

KiCad 8 探秘合集

KiCad 使用经验分享

KiCad 设计项目(Made with KiCad)

常见问题与解决方法

KiCad 开发笔记

插件应用

发布记录

审核编辑 黄宇

-

系统设计

+关注

关注

0文章

154浏览量

21621 -

KiCAD

+关注

关注

4文章

163浏览量

8788

发布评论请先 登录

相关推荐

树莓派Pico 2发布,搭载RP2350双核RISC-V和Arm Cortex-M33微控制器!

51单片机最小系统是什么?51单片机最小系统的电路介绍

Altium Designer绘制stm32最小系统

RP2350 数据手册及深度了解功能性能特性和开源项目案例

Made with KiCad(九十一):基于 RP2350 的最小系统设计

Made with KiCad(九十一):基于 RP2350 的最小系统设计

评论