硬件架构基础:

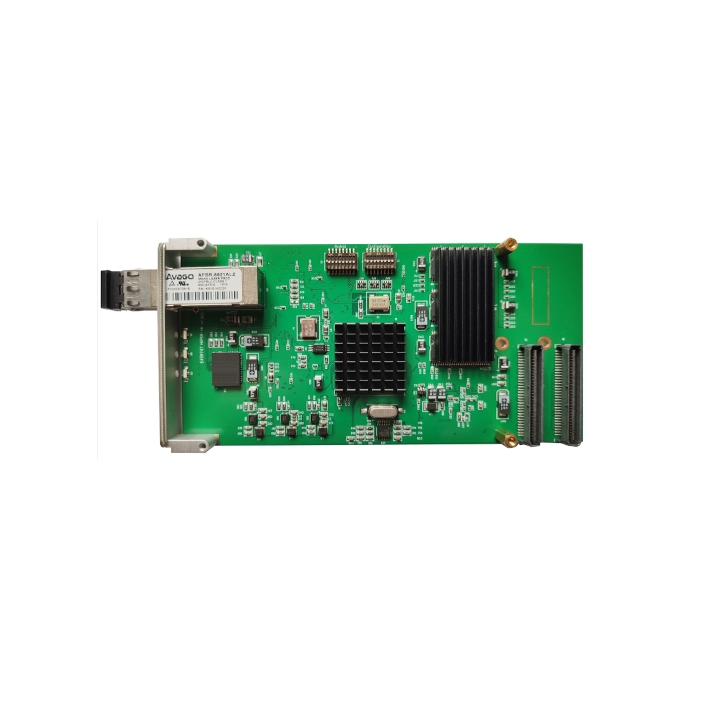

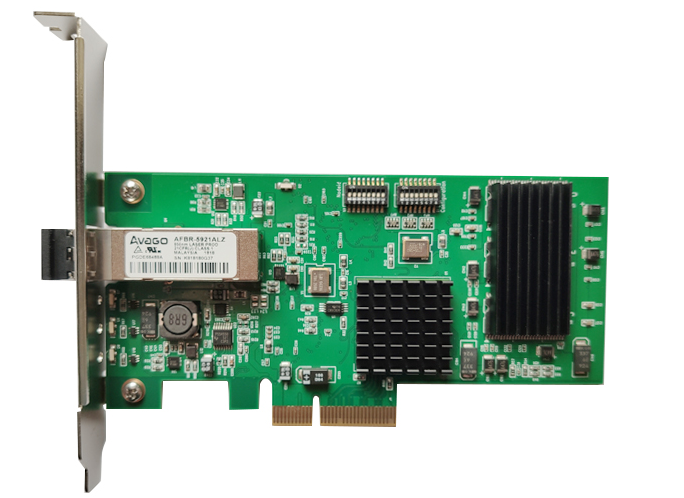

核心组件:反射内存卡通常由 SFF 光模块、FPGA 控制模块、SDRAM 存储模块、电源与时钟模块、串行解串器等组成。

SFF 光模块:用于实现 FPGA 控制模块与网络中其他反射内存卡之间的高速通信互联,提供高速的光纤通道连接,保证数据能够快速传输。

FPGA 控制模块:一般选用高性能的 FPGA 芯片,是整个数据发送与接收的控制核心,负责处理数据传输的逻辑。

SDRAM 存储模块:用于暂存网络中各反射内存卡的共享数据,其容量常见的有 128MB 或 256MB 等,能够快速地存储和读取数据,为数据的临时缓存和传输提供支持。

电源与时钟模块:为系统提供所需的电源和时钟信号,确保各部件能够稳定、同步地工作。

串行解串器:主要负责数据的串行和并行转换,在数据传输过程中起到关键作用,将并行数据转换为适合在光纤等传输介质上传输的串行数据,以及在接收数据时将串行数据转换回并行数据。

数据写入过程:

本地写入触发广播:当网络中的某一台计算机向其本地插入的反射内存卡写入数据时,FPGA 控制模块会立即检测到这一写入操作。然后,该数据和相应的内存地址会被准备进行广播。

数据传输启动:通过串行解串器将待广播的数据进行处理后,经由 SFF 光模块和光纤等传输介质,将数据发送到网络上的其他反射内存节点。

数据接收与更新过程:

接收数据:其他反射内存卡的 SFF 光模块接收到传输过来的数据后,串行解串器将串行数据转换回并行数据,然后传输给 FPGA 控制模块。

数据写入本地内存:FPGA 控制模块将接收到的新数据写入板载的 SDRAM 存储模块中,存储在与发送节点相同的内存位置,从而实现数据的同步更新。这样,每个节点都维护着一个相同的内存映像,确保了数据的一致性。

数据读取操作:当网络中的其他节点需要获取数据时,它们可以直接从本地的反射内存卡的 SDRAM 存储模块中读取最新的数据,就好像数据直接存储在本地一样,极大地提高了数据访问的速度和效率。

总之,反射内存卡基于硬件实现的数据传输和同步机制,不依赖于 CPU 的干预和复杂的软件协议处理,具有高速、低延迟、数据共享、易于使用等特点,适用于对数据传输实时性要求较高的系统。

审核编辑 黄宇

审核编辑 黄宇

-

交换机

+关注

关注

21文章

2662浏览量

100274 -

反射内存卡

+关注

关注

0文章

95浏览量

2089

发布评论请先 登录

相关推荐

反射内存卡驱动的安装介绍

反射内存卡的优势与特点

如何选择反射内存卡

反射内存卡与普通内存卡的区别

反射内存卡的工作原理

反射内存卡的工作原理

评论