在系统级仿真中,与DDR4-3200 相比,更高数据速率下的 DDR5 的有效带宽几乎是其两倍。这种改进是通过提高数据速率和增强架构来实现的。DDR5 包含从 3200 MT/s 到 8800 MT/s 的数据速率。一个值得注意的特性是在DQ接收器中集成了一个多抽头判决反馈均衡器,可在更高的数据速率下抵消码间干扰(ISI)效应。这些发展旨在满足下一代 CPU 对每个内核带宽日益增长的要求。

测试要求也同样发生了变化,以确保满足电气和时序裕量。

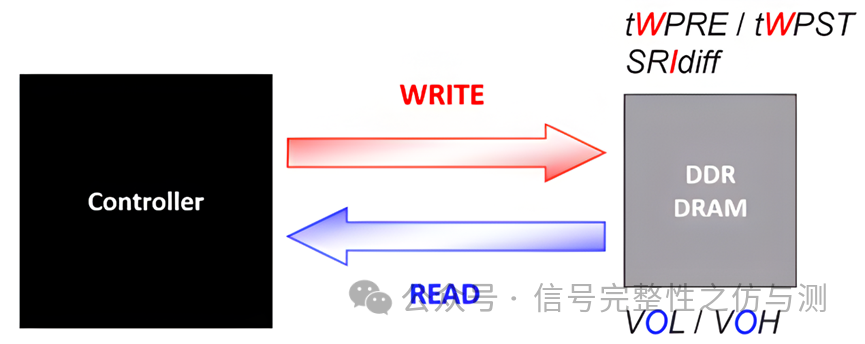

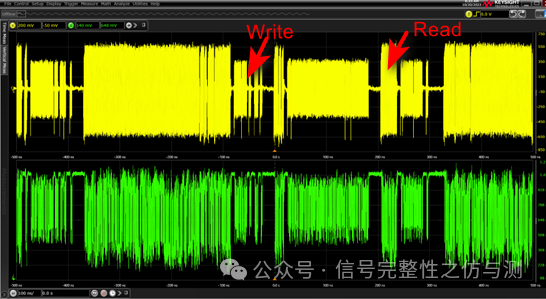

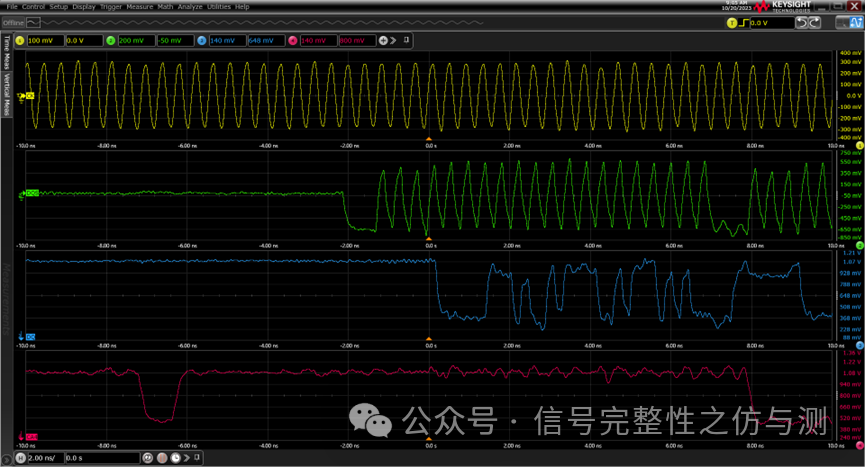

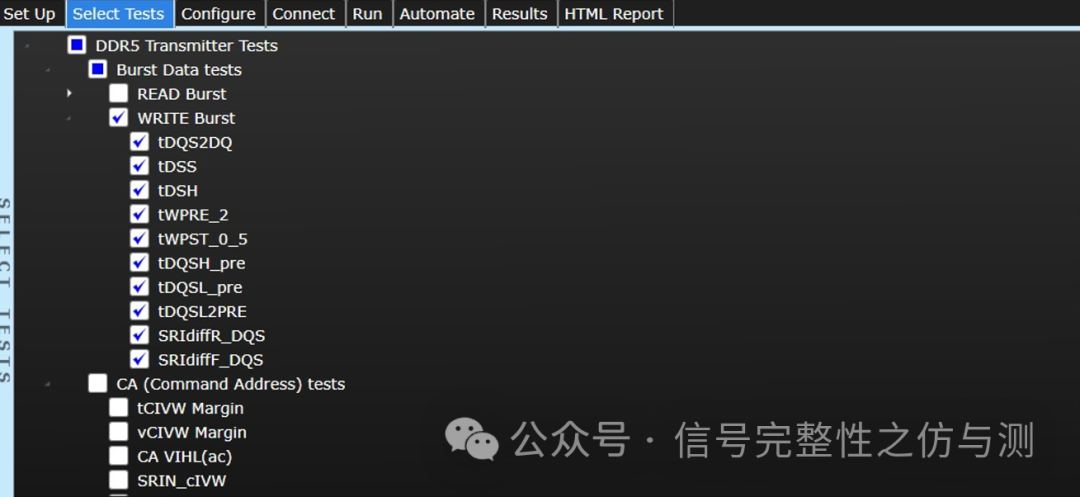

DDR5电气和时序规格会根据信号是读取还是写入数据而变化。这意味着,例如,斜率或电压电平取决于信号的方向和来源。写入数据从内存控制器发送(红色),数据从内存读取(蓝色)。写测试包括“写入前导码时序”和“输入差分斜率”。读测试包括“读取高输出电平和低输出电平”。DDR5的读写数据双向传输意味着测试时必须包括读写分离步骤,以分析双向信号的单个数据。

读写分离一直是 DDR 总线测试的难点。由于 DDR 总线一直采用读写数据共享数据总线,而 JEDEC 规范针对读写操作制定了不同的指标,因此如果需要对被测器件和设备进行准确测试就必须分别对读和写进行分开测试。一种方法是 Memory Controller 可以编程只进行读或写操作以分别进行测试,这种方法不易实现。另外一种方法就是在示波器上根据读和写信号的特点设置恰当的触发进行分离。

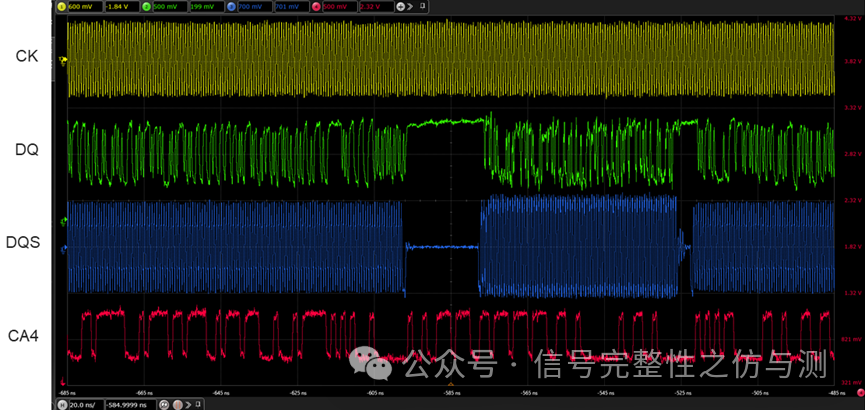

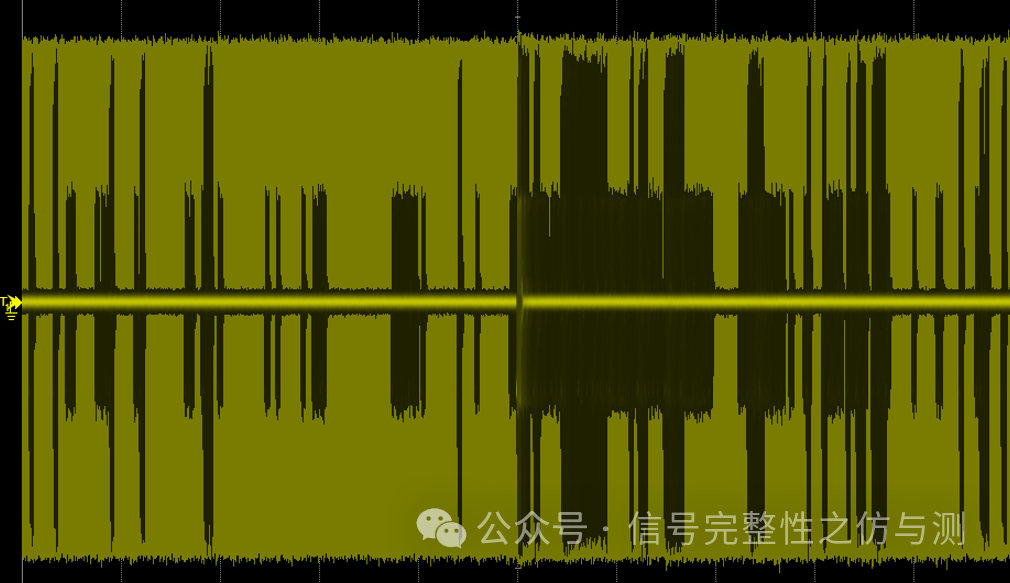

在主板上电的正常操作期间捕获信号后查看信号可能并不容易。如我们主要关注的CLK/DQS/DQ/CA4信号,没有任何后处理,很难判断读取和写入数据何时处于活动状态。

相位关系

对于DDR4及更早版本,读取和写入数据遵循可预测的模式,使测试设备能够轻松检测分离:数据相对于写入选通DQS的中心对齐,读取时边缘对齐。

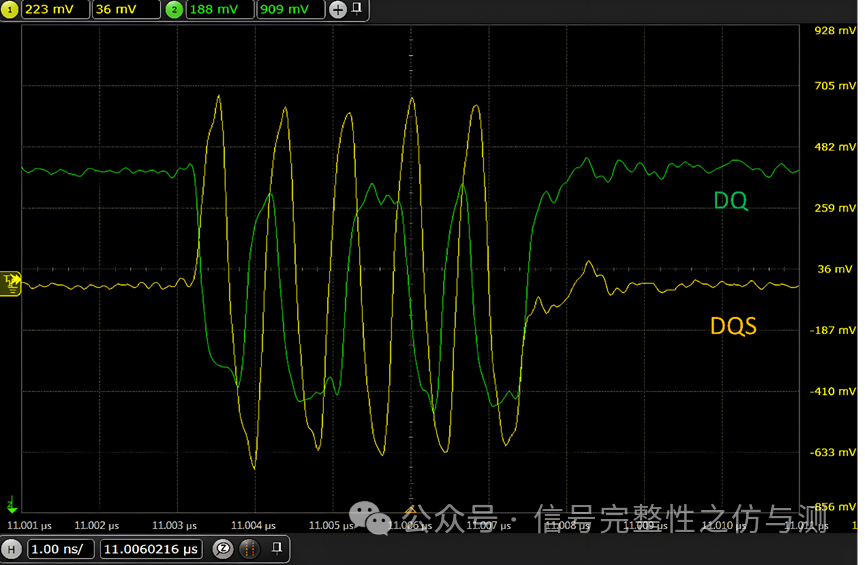

上图显示了中心对齐的 DDR4 写入数据和选通信号示例:大部分时序和偏斜对齐的负担都落在内存控制器上,因此写入数据以最小的偏斜到达 DRAM 接收器(中心对齐),使数据锁存更容易。

在过往DDR3和DDR4总线上,主要采用DQS前导位或者DQS和DQ的相位差进行分离。

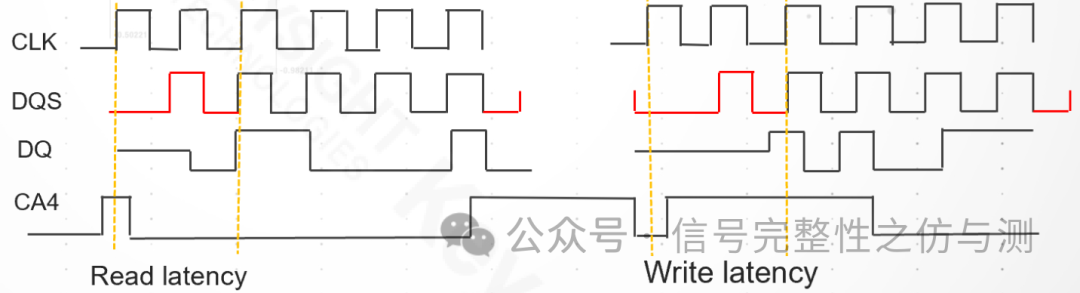

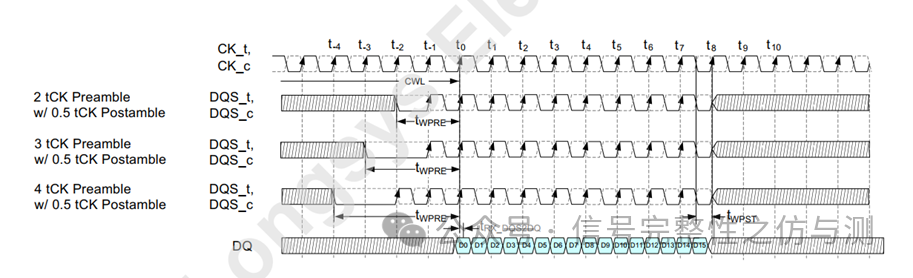

在DDR5总线上,DQS和DQ在读写操作时没有相位差,DQS的读写操作的前导码也是相同的。

因此在DDR5总线上的读写分离是一个难点。

对于DDR5,除了写入之外,这些规则几乎相同。为了降低功耗(DQS 时钟门控)并简化写入训练,DDR5对DRAM输入使用无与伦比的路径。但是,还有其他方法可用于读取和写入信令。

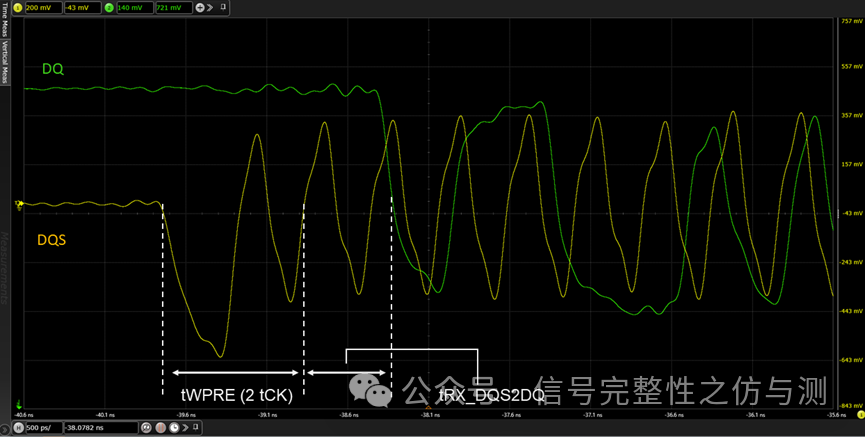

上图显示了写入数据和选通信号之间可能的可变延迟。

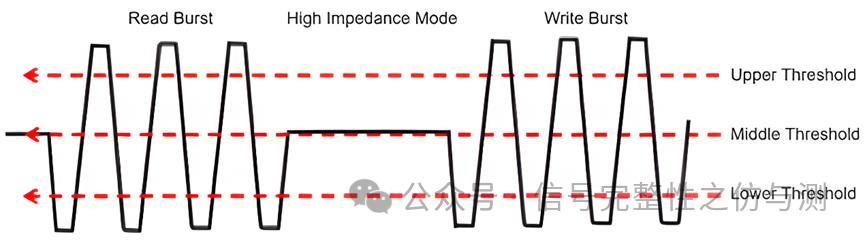

振幅差异

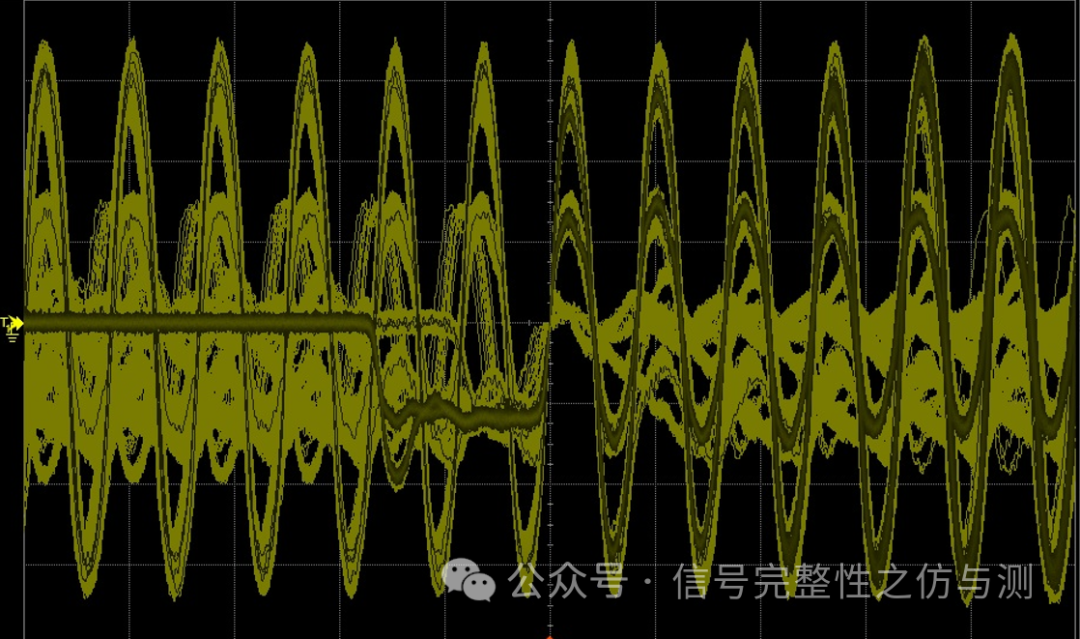

尽管DDR5使用复杂的协议来存储和检索数据,但更高的数据速率为实现读写分离提供了一个有趣的途径。较高的频率相关损耗和信号衰减导致读写之间的幅度差异更明显。由于内存流量是尽可能靠近DRAM捕获的,无论是直接捕获还是使用interposer,因此读取数据的幅度预计会更高。了解这些差异可以简化分离识别过程。一些 DDR5 合规性工具提供此功能,甚至可以使用机器学习算法来更好地区分全摆幅突发和“峰值”边缘。

命令/地址解码(CA4)

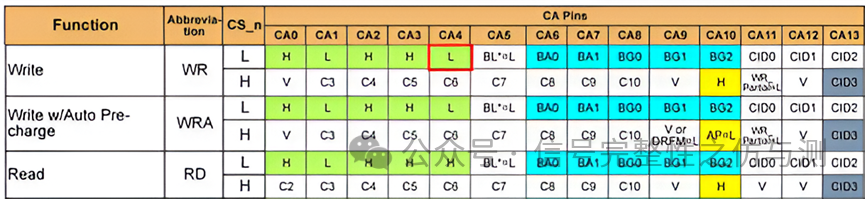

由于DRAM接收读取和写入事务的命令和地址信息,因此很自然地认为测试设备也可以解码命令以更好地识别分离。这是理想的方案,适用于某些配置。完整命令总线解码选项的替代方法是对 CA 总线进行部分解码,并仅关注确定给定命令的突发类型的 CA 位。对于 DDR5,这是 CA4。

在JEDEC协议中,很容易就能找到CA4的特别之处,可以看到,写数据时,CA4呈现的特征是低电平;读数据时,CA4呈现的特征是高电平。

那是不是我只要找到持续的CA4的低电平信号,此时对应的数据就是写信号呢?

你想多了!

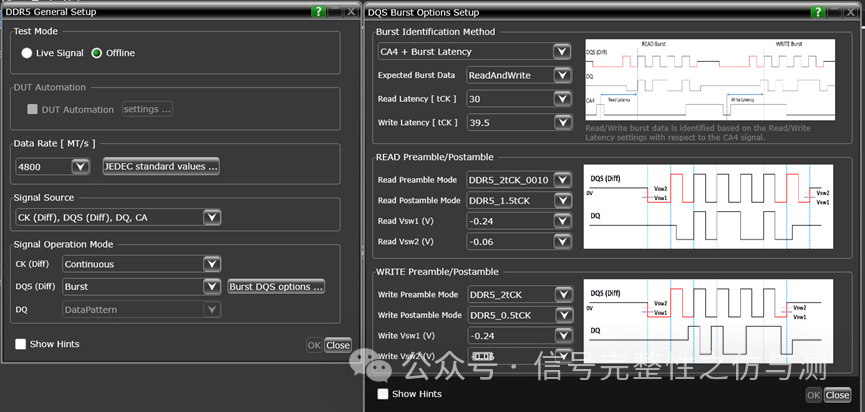

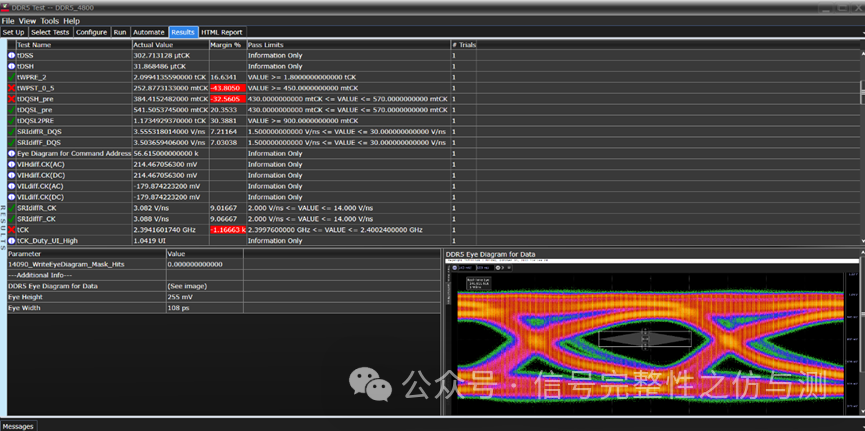

DDR5的一致性测试软件提供了CA4 lantency分离方法,同样还有DQS、DQ的Phase分离方法,通过检测信号的阈值电平来作为一大判断依据。

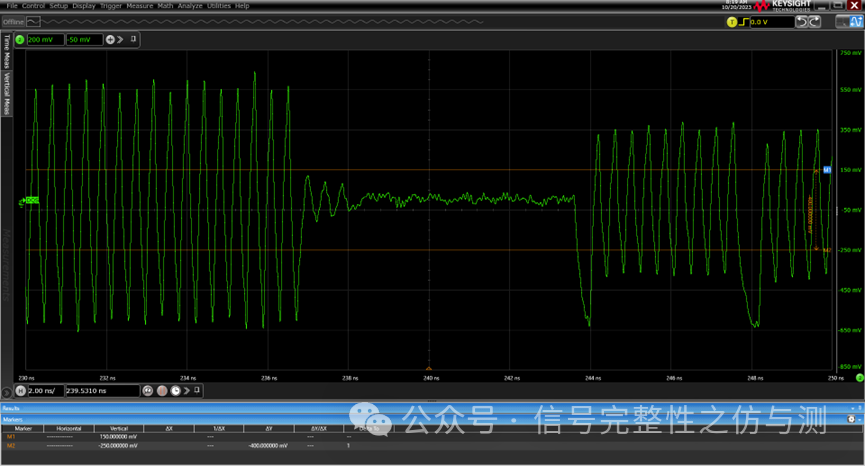

阈值或参考电平用于确定突发开始和结束时以及 DQ 和 DQS 信号之间的有效转换。下面显示了读信号,然后是电气空闲状态,然后是写信号。

再来看看CA4分离

第 1 步:通过使用屏幕上的标记或光标来测量延迟以及前导和后导转换电压,从而确定时序和基准电平。在下图中,CA4在有效写数据(绿色)开始时的延迟(红色)。

第二步,输入相关的数值,很关键。

Preamble参考协议中的要求

第 3 步:选择并运行测试。

看这个步骤是不是觉得很简单,包括开篇的视频也介绍了如何找read和write lantency,理论上是应该行云流水的等着APP跑出结果就行了。

然而,理论就是理论,无论你是用phase分离还是用CA4 lantency分离,都是在考虑你的耐心,这个问题找了原厂FAE现场,找了付费的技术支持远程连线,折腾了两个月也没说出个1234,分离的成功率确实是太低,就算能分,也要跑小时以上。

算了,还是推荐最原始的分离方法,1分钟即可分离。

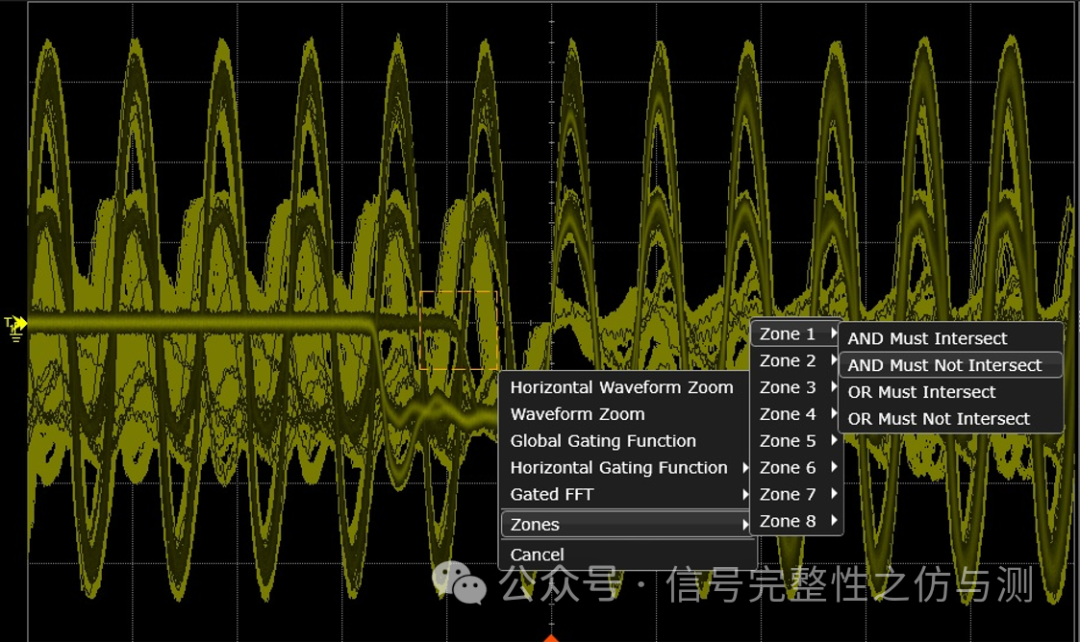

将上述波形展开,读写信号都混在一起。

右键→Zones→AND Must Not Intersect

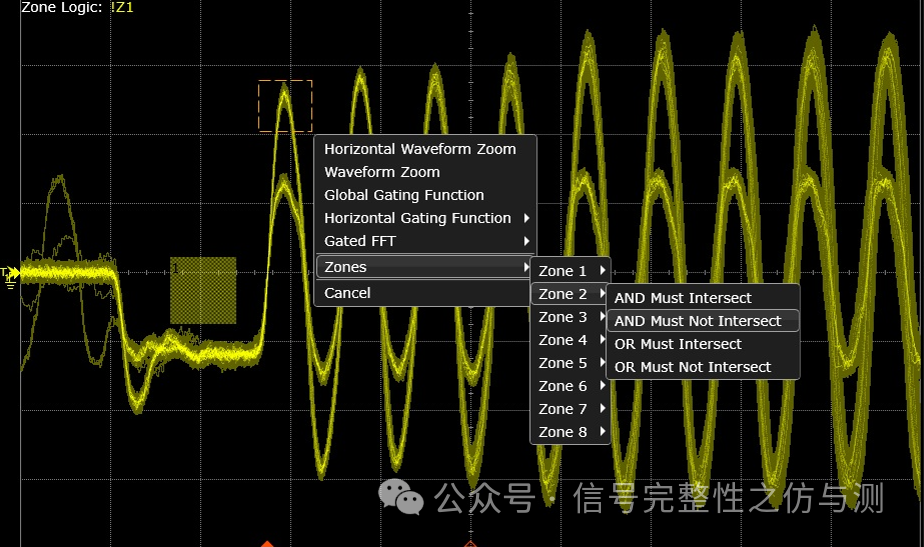

同样的方法,划第二个框

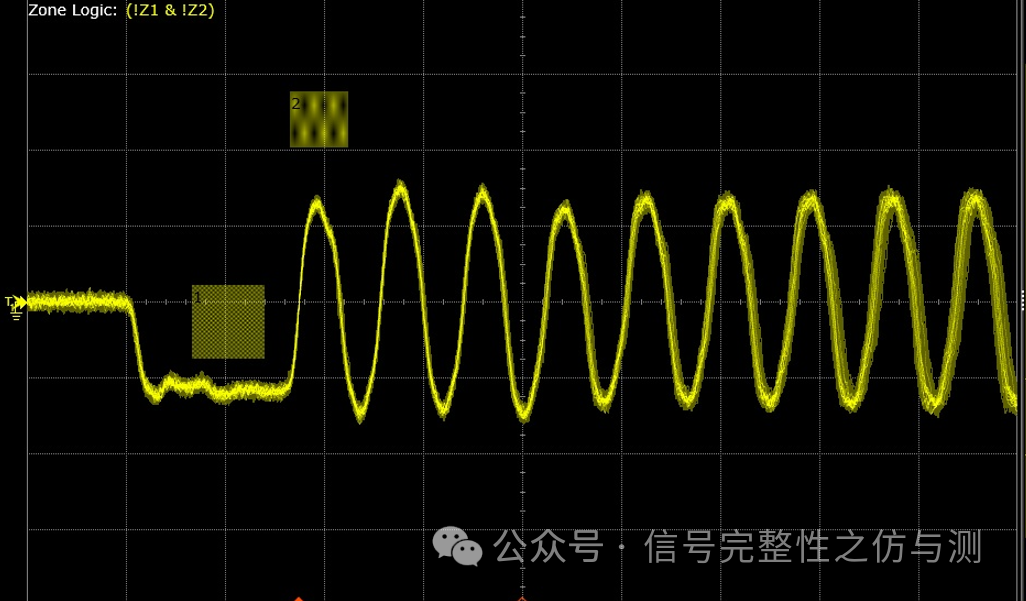

DQS分离成功

DQS分离成功后再看DQ眼图也就眉清目秀了。

总而言之,读写分离采用InfiniiScan要远比APP要高效简单。

-

仿真

+关注

关注

50文章

4155浏览量

134478 -

DDR4

+关注

关注

12文章

323浏览量

41123 -

DDR5

+关注

关注

1文章

433浏览量

24353

原文标题:DDR5:揭秘读写分离技术的奥秘

文章出处:【微信号:si-list,微信公众号:高频高速研究中心】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?

Introspect DDR5/LPDDR5总线协议分析仪

DDR3/4都还没玩够,DDR5已经来啦

DDR5这么快,为啥还能那么稳?

三种主流内存技术(DDR、GDDR、LPDDR)的速度对比与应用和DDR5芯片的设计

Cadence公司发布了关于即将发布的DDR5市场版本以及技术的进展

DDR5内存将在明年实现量产

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR5

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

揭秘DDR5的读写分离技术奥秘

揭秘DDR5的读写分离技术奥秘

评论