- ALINX NVMeIP -

在当下数据驱动的时代,企业对高性能存储解决方案的需求不断增加。NVMe AXI IP 凭借其支持大数据量、高速传输、低延迟等存储性能优势,成为众多开发者和企业的理想选择。

NVMe专为 SSD 而生,通过直接利用 PCIe 通道,避免 SATA 协议和外置控制器(PCH)的额外延迟,使性能大幅提升,尤其在随机 I/O 操作中表现突出。

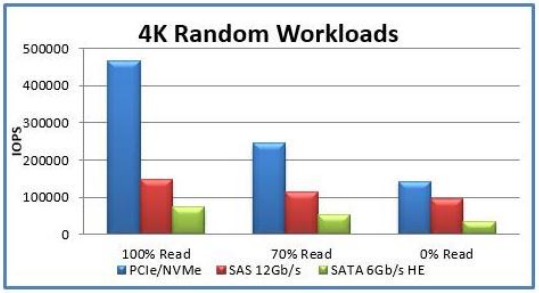

NVMe PCIe SSD的 IOPs 性能可达高端企业级 SATA SSD 的十倍(具体场景为高队列深度的随机读写),同时支持自动功耗状态切换和动态能耗管理功能,显著降低功耗。

( NVMe/SAS/SATA 存储设备单读性能对比)

NVMe 协议凭借其高速传输、低延迟、高效能存储和高可靠性的特点,在数据中心、边缘计算、企业存储、AI 服务器和云计算等领域有着广泛应用。

ALINX NVMe IP 详情

ALINX NVMe IP 针对当前数据密集型应用进行了深度优化,显著缩短了延迟时间,提升数据吞吐量,满足云计算、大数据分析、人工智能、虚拟现实/增强现实( VR/AR )等前沿领域的迫切需求。

兼容性方面,NVMe IP 不依赖 CPU,全部由 FPGA 完成处理,需要 FPGA 具有足够的资源和适当的硬件支持。ALINX NVMe IP 目前支持AMD Virtex 7/ AMD UltraScale/AMD UltraScale+系列器件。

技术支持方面,ALINX 提供完善的技术支持和高效的定制化服务,由经验丰富的 IP 研发团队专人对接,全程协助客户完成 IP 集成和性能优化,确保客户需求快速实现。

考虑到每个应用场景都有其独特需求,ALINX NVMe AXI IP 为开发者提供了丰富的定制选项,允许根据特定的应用需求对其性能进行精准调整,包括不限于优化特定工作负载下的数据传输速率,根据不同的存储容量需求进行配置等。

以下是 ALINX NVMe IP 的详细介绍:

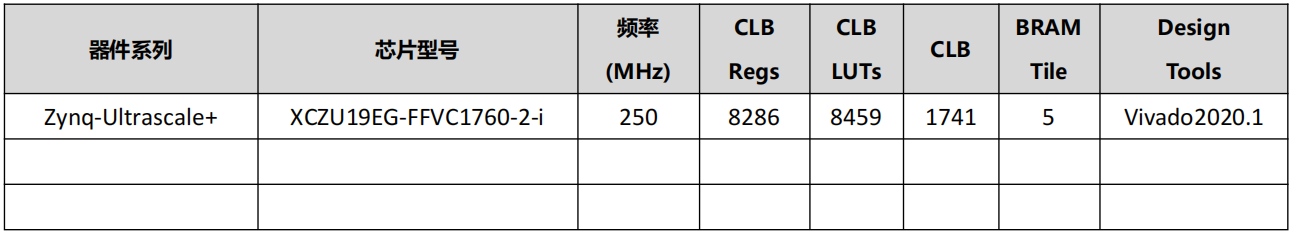

IP 资源消耗表

注:IP 实际逻辑资源消耗受实例化中其他逻辑资源消耗影响

产品特性

功能支持:命令支持(Identify、Write、Read、Flush),兼容 NVMe 1.4 协议,支持 PCIe Gen 1.0-4.0;

性能参数:

(1)最大队列深度:每个队列支持 65535 个 I/O 命令;

(2)传输速率:基于 PCIe 3.0 X4,读写速率均可达 3000MB/s;

灵活性:支持多种存储单元(512 字节 / 4096 字节);

支持定制化服务:包括数据传输速率优化和存储容量配置;

版本支持:支持两个版本(AXI FULL 版本 / AXI Stream 版本);

参考设计:XCZU19EG + FMC子板(FH1402)+SAMSUNG 980 M.2 SSD。

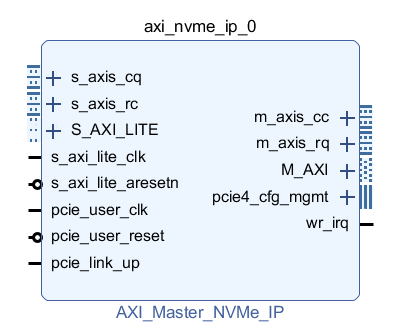

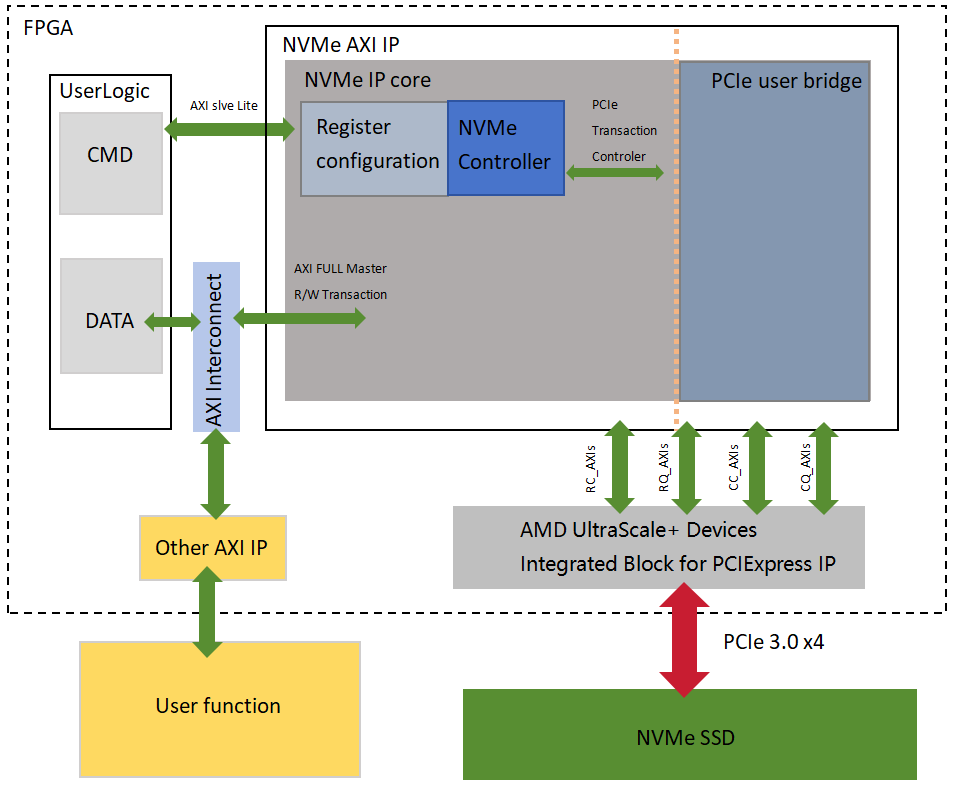

AXI-Master-FULL 版本

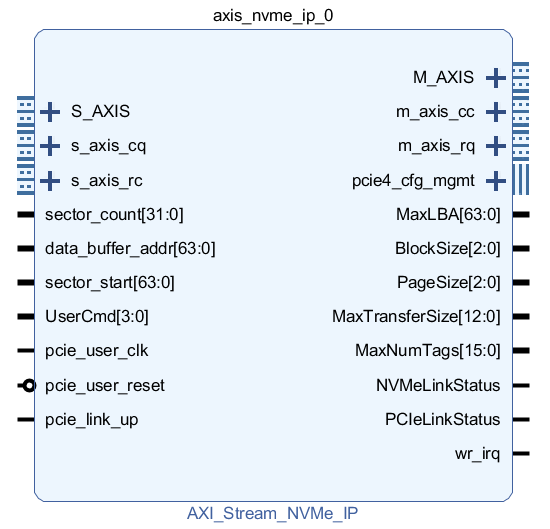

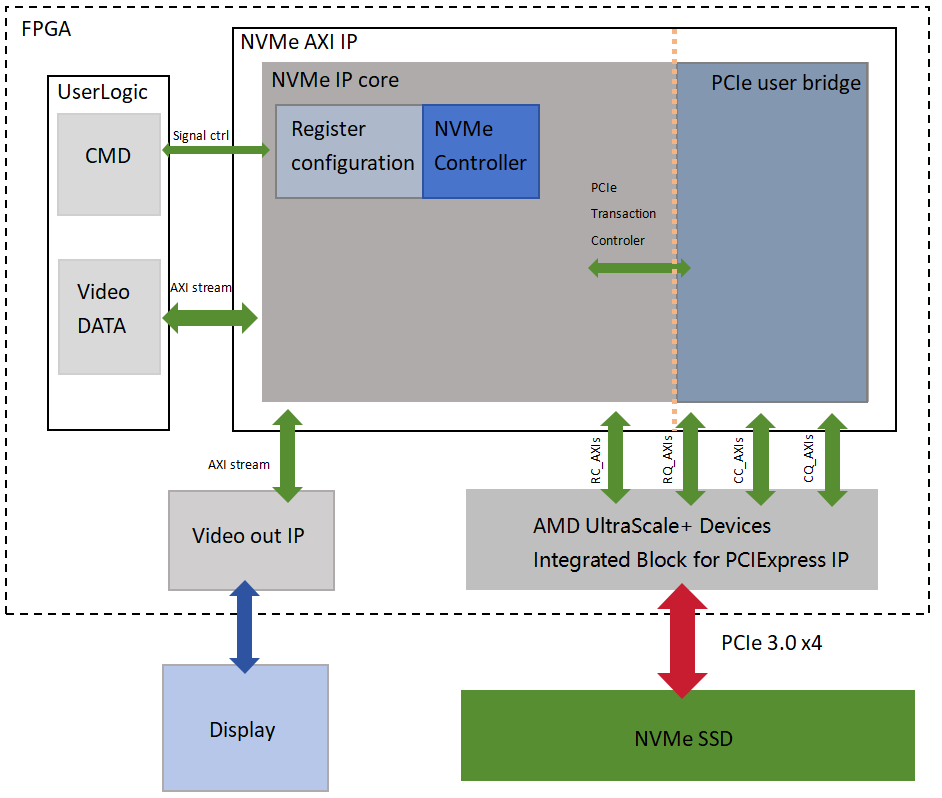

AXI-Stream 版本

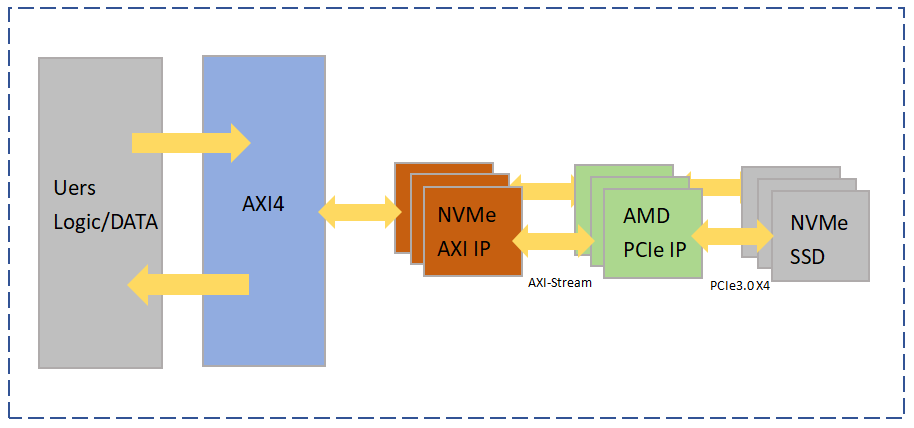

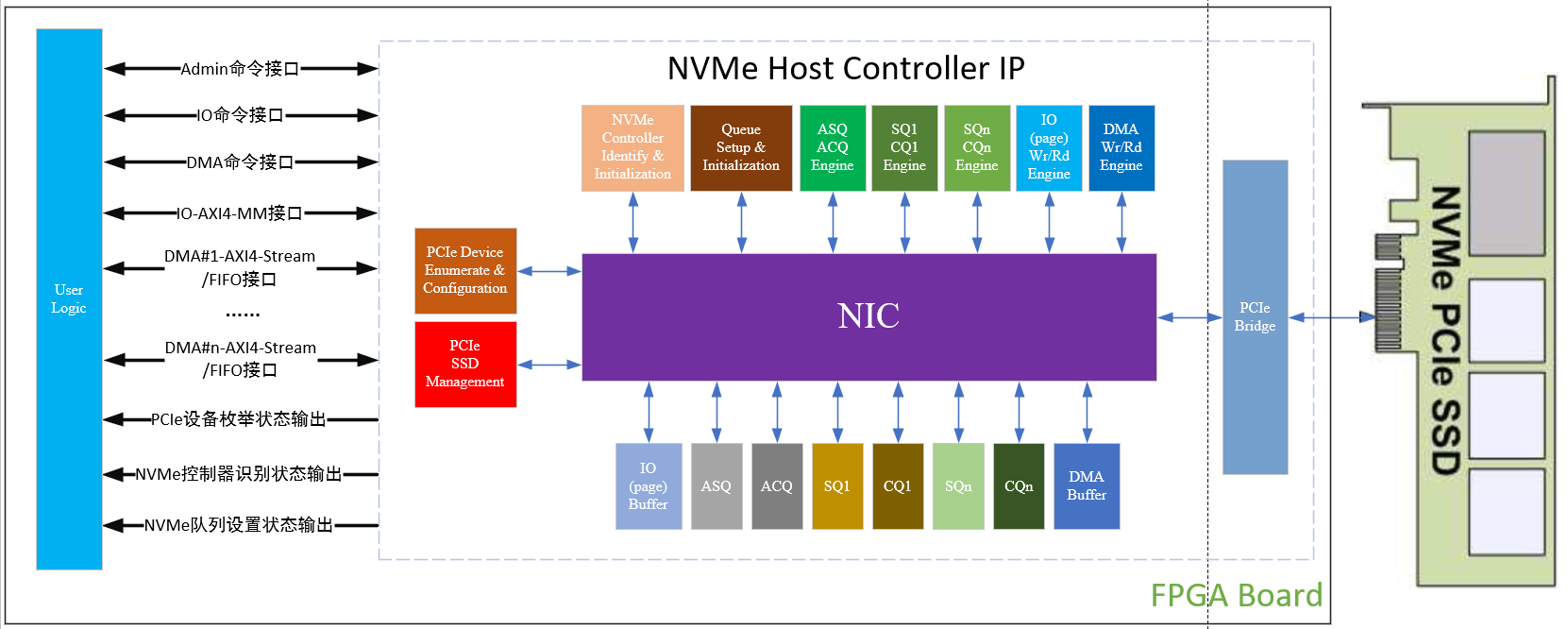

NVMe AXI IP 应用交互

NVMe AXI IP 通过 PCIe Bridge 实现 PCIe 协议交互,支持 AXI FULL 和 AXI Stream 两种接口模式。用户数据通过 AXI Interconnect 接入后,经过 NVMe AXI IP 的协议逻辑处理,被打包为 PCIe TLP 包并写入 NVMe SSD 存储;同样,数据从 NVMe SSD 提取后,通过协议解析和 AXI 接口传递到上层逻辑。

Example 举例

AXI-Master-FULL 版本

AXI 读写:在系统正常启动后,NVMe AXI IP 自动初始化并建立 PCIe 链路连接。初始化完成后,用户的数据流通过 AXI Interconnect IP 传送到 NVMe AXI IP 的 AXI Master FULL 接口,进行 NVMe 协议的处理。数据被打包为 TLP 层 PCIe 包,并通过 RC/RQ/CC/CQ AXI Stream 接口与 AMD UltraScale+ 设备的 PCIe 集成模块(Integrated Block for PCIExpress)连接,最终写入 NVMe SSD 存储。当需要读取数据时,NVMe AXI IP 从 NVMe SSD 通过 RC/RQ/CC/CQ AXI Stream 接口提取数据,再通过 AXI Master FULL 接口与 AXI Interconnect IP 连接,将数据传输到其他 AXI 总线接口供用户逻辑使用。

AXI-Stream 版本

AXI Stream 读写:在系统正常启动后,NVMe AXI IP 自动进行初始化并建立连接。初始化完成后,用户的数据流通过 AXI Stream 接口输入到 NVMe AXI IP,执行 NVMe 协议的交互处理。数据被打包为 TLP 层 PCIe 包,通过 RC/RQ/CC/CQ AXI Stream 接口与 AMD UltraScale+ 设备的 PCIe 集成模块连接,最终存储到 NVMe SSD。当从 NVMe SSD 读取数据时,NVMe AXI IP 使用 RC/RQ/CC/CQ AXI Stream 接口提取数据,并通过 AXI Stream 接口传输给连接的视频输出 IP,进而通过视频接口进行数据展示。

审核编辑 黄宇

-

FPGA

+关注

关注

1625文章

21640浏览量

601385 -

存储

+关注

关注

13文章

4237浏览量

85603 -

IP

+关注

关注

5文章

1626浏览量

149287 -

SSD

+关注

关注

20文章

2847浏览量

117148 -

nvme

+关注

关注

0文章

216浏览量

22569

发布评论请先 登录

相关推荐

浅谈ALINX NVMe IP产品特性

芯驿电子 ALINX 推出全新 IP 核产品线,覆盖 TCP/UDP/NVMe AXI IP 核

芯驿电子ALINX推出全新IP核产品线

高性能NVMe主机控制器,Xilinx FPGA PCIe 3

高性能NVMe主机控制器,Xilinx FPGA NVMe Host Accelerator IP

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

NVMe Host Controller IP实现高性能存储解决方案

Xilinx FPGA NVMe Host Controller IP,NVMe主机控制器

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

一文详解 ALINX NVMe IP 特性

一文详解 ALINX NVMe IP 特性

评论