1.开机和开软件

开机启动后是这个画面

账号:

密码:

右键屏幕左击open terminal

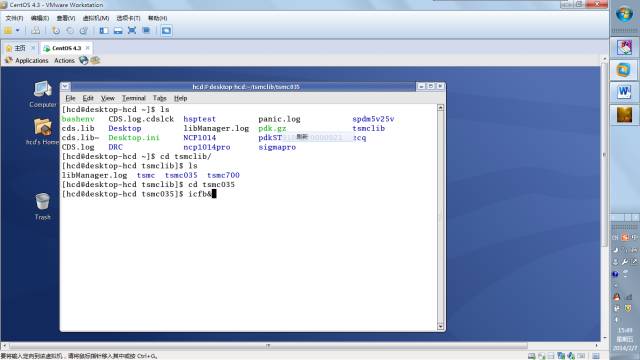

命令行里面打入如下图的命令

ls 和 cd 是linux里面的命令。作用你就去网上查一下。

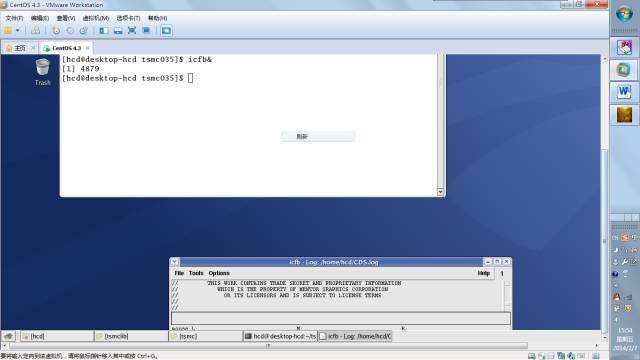

icfb&是打开cadence的命令。屏幕的底部会出现这么一个图像界面。

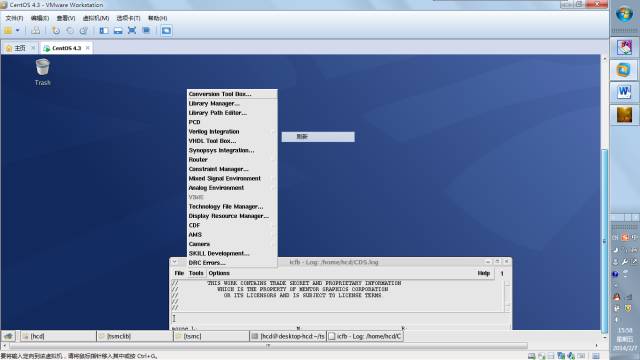

点击图形界面的Tools,会弹出下面这东西,点击Library Manager

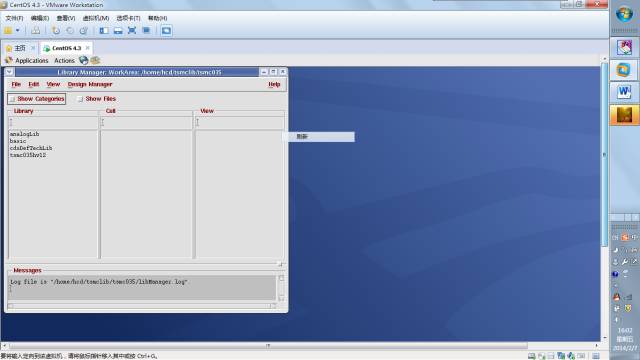

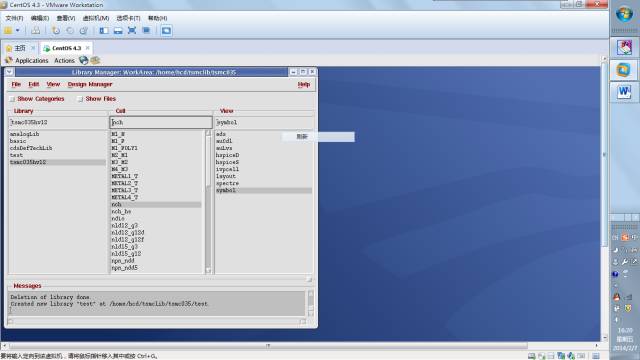

点击后弹出如下图所示的框图

Library manager里面管理的时候分三个栏目。

Library,一般取自己的名字,拼音都可以

Cell,一般是你要设计的电路的名字

View,一个cell对应着不同的view,有版图Layout,有原理图schematics,等等。

2.软件的library manager使用

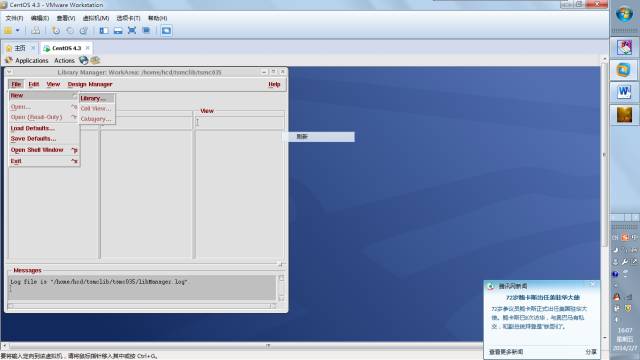

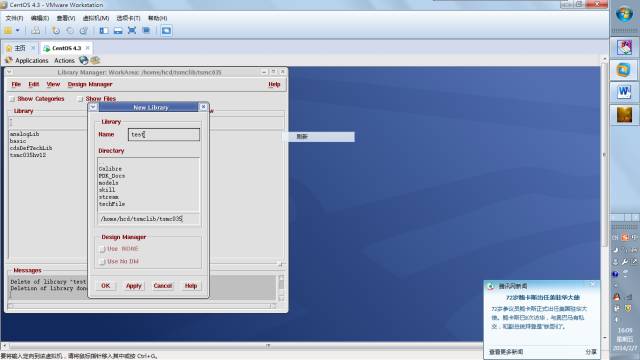

下一步首先创建自己的库

OK后库里面就有相应自己的库了,自己做的电路可以放到里面管理,不要和其他的库混着用。

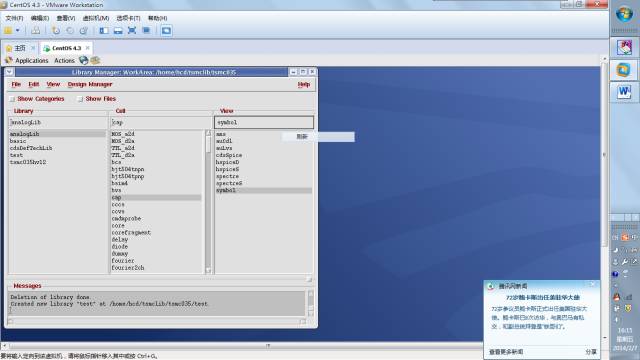

来看下软件自带的analogLib里都有哪些cell。

图上选中的是cap,就是理想电容,对应的view有很多了,画原理图的时候,调用选用的view是symbol。

analogLib库里面还有其他常用的元件:地gnd,直流电源vdc,直流电源idc,电流控制电压源ccvs,理想电阻res等。这个自己去网上查到底有哪些。

库tsmc035hv12是台积电的.35的工艺库(库涉密,不鼓励外传)。这个库里面我们用到的就是nch和pch,分别是nmos和pmos的模型名字。画原理图的时候,调用该cell的symbol。

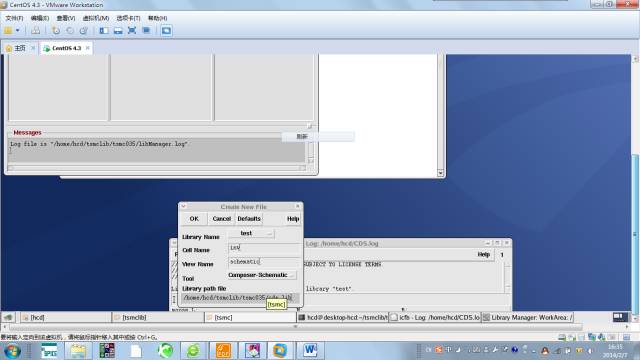

好了,下一步要创建自己的cell了。先选到自己新建的库test。之后再点file->new->cellview

在屏幕下方会产生这样的对话框,填入cell的名字,当画原理图时tool选图中的这个。画layout就选virtuoso,可以尝试变一下。当然我们这选composer-schematic。

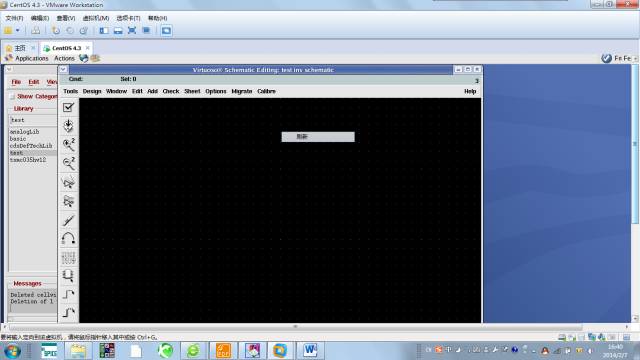

OK后会弹出这个窗口,用来画原理图。

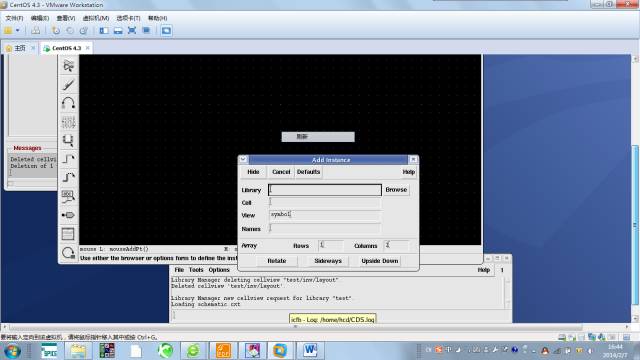

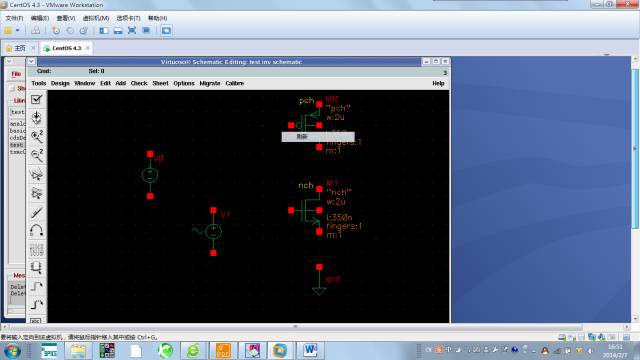

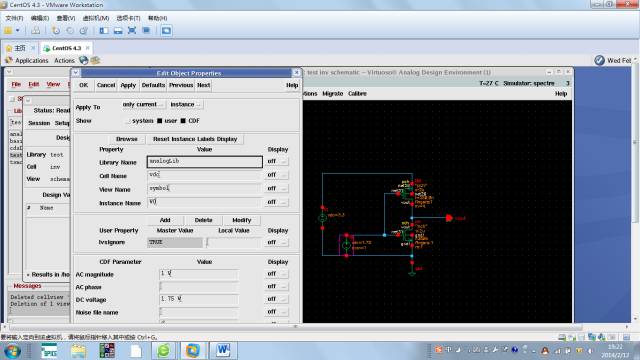

切换到英文输入法,快捷键i是放置元件的意思 instance。我们需要nch,pch,gnd,电源vdc,还有信号源vsin。

屏幕下面会弹出这个框框

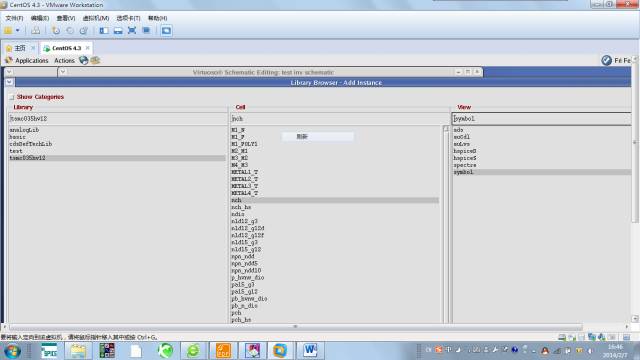

按browse选择如下图所示,这样也就选中了nch,选其他元件也是这样的方法。

只不过gnd,vdc,vsin是在analoglib里面找。

最小化该窗口,鼠标移动到schematic窗口,点击就可以放下元件。

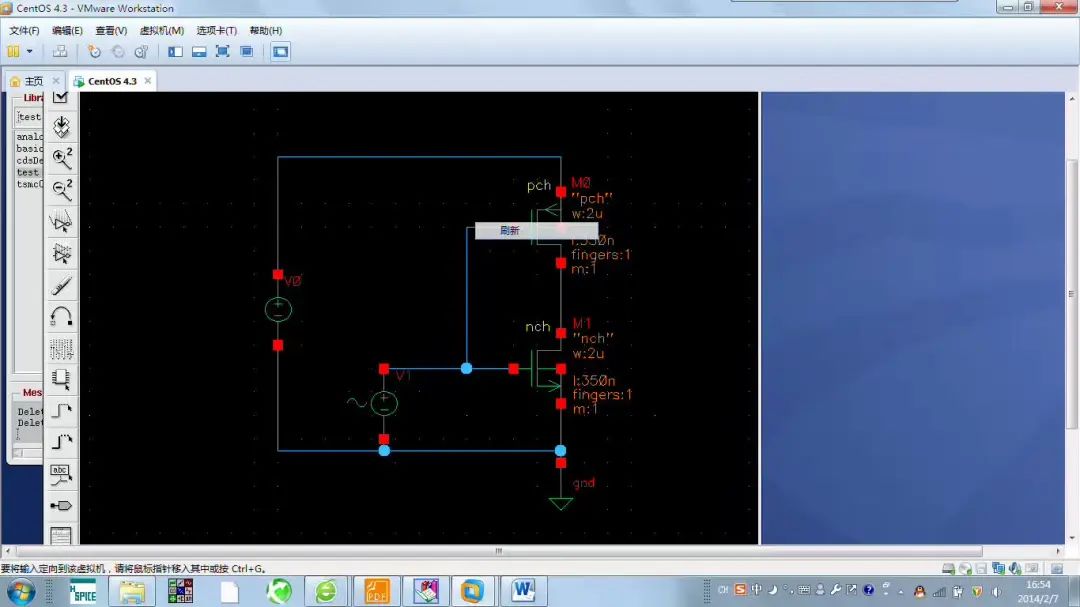

这样就放置好元件了,按下快捷键w可以连线。

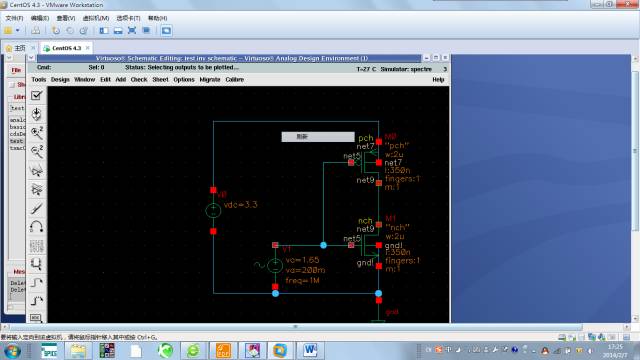

接着就是设置信号源和电压源的信号幅度。

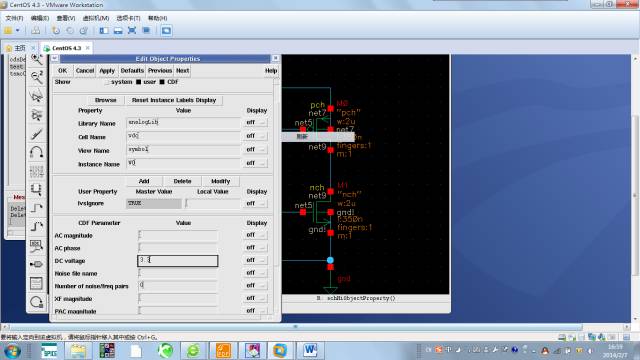

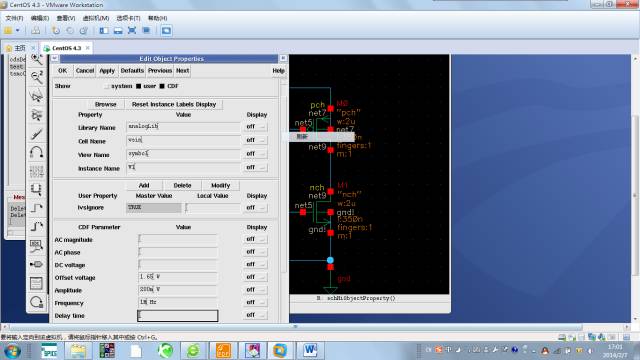

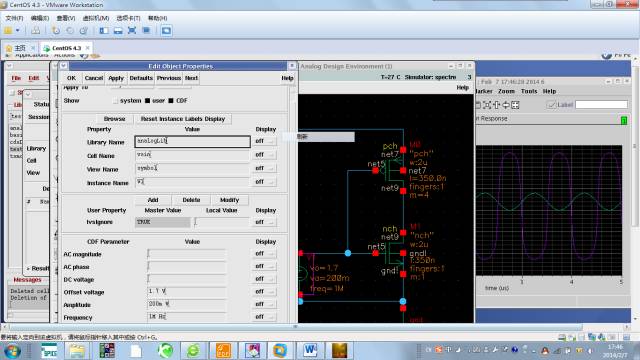

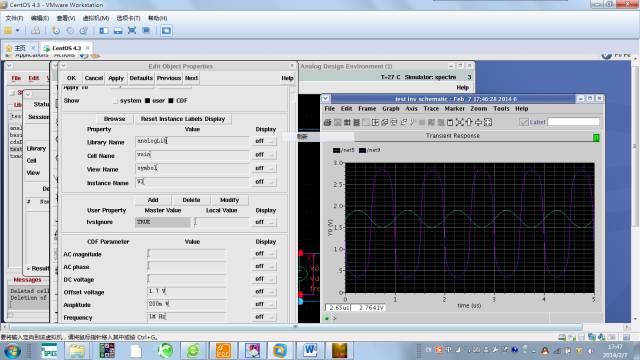

先选中元件v0,快捷键q可以查看和设置其参数。

V0设置直流电压3.3V

V1设置offset电压1.65V,正弦信号幅度200m,频率1Mhz。注意:输入这些值的时候,不需要输入单位。200mV只需要输入200m就可以了。1Mhz同理。

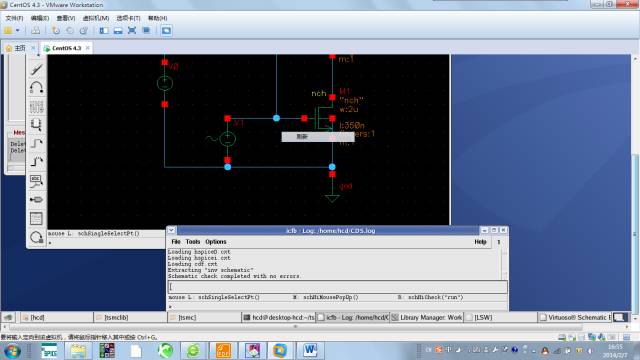

OK,这样就连好了,按下快捷键x检查电路是否连接完整和设置正确。如果无误,在我们一开始的对话框里会有这么一句几个字No errors。

这样就可以仿真了。

3.仿真工具使用

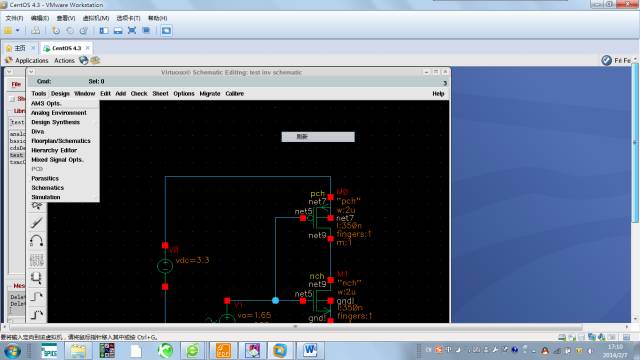

Analog environment就可以进入仿真了。

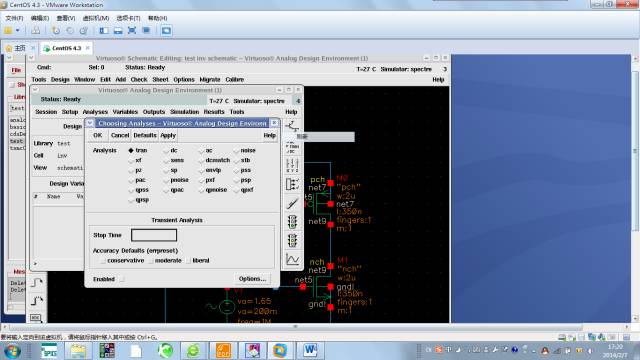

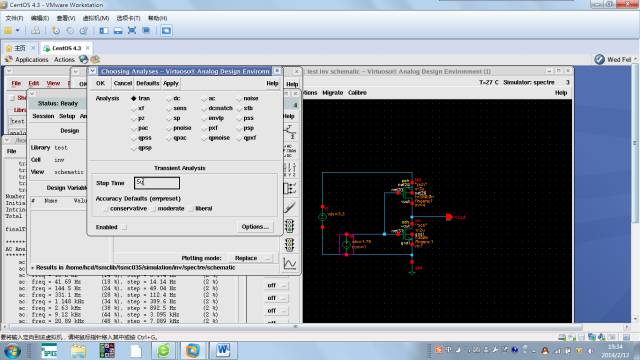

Analyses->choose弹出如下的画面。

选择瞬态仿真tran,Stop time 选5us,accuracy 可以不用选 enable选上。

其他常用的仿真如dc,ac自己可以查资料研究下。

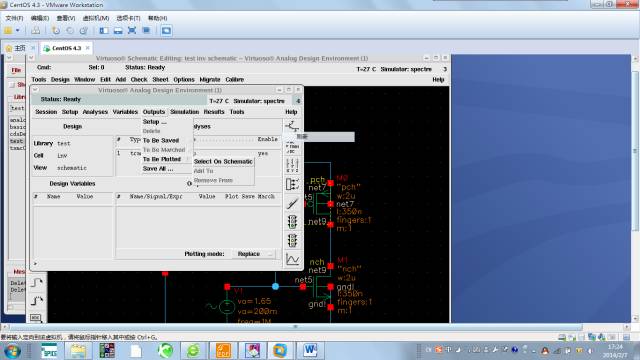

输出信号这样选择outputs->tobe plotted->select on schematic

点击上面的按钮后窗口会自动弹到原理图的窗口。点击到连线上是查看该点的电位,点击节点(红色的地方)是查看改点的电流。选择完之后会显示出和其他不一样的框框。按esc键退出选择。我们选择输入和输出节点。

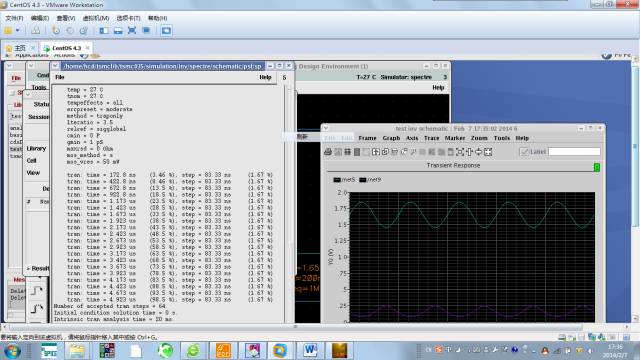

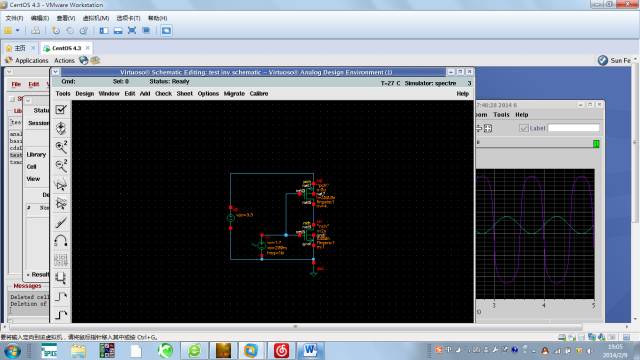

TRAN仿真

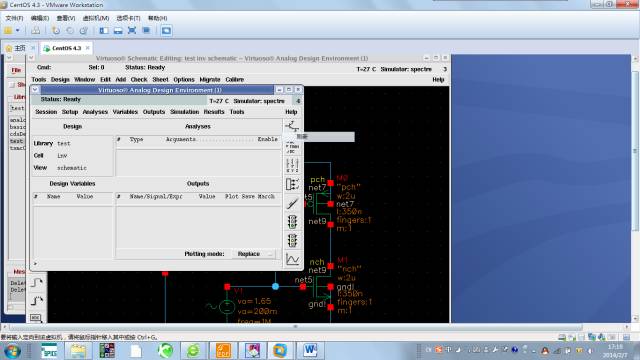

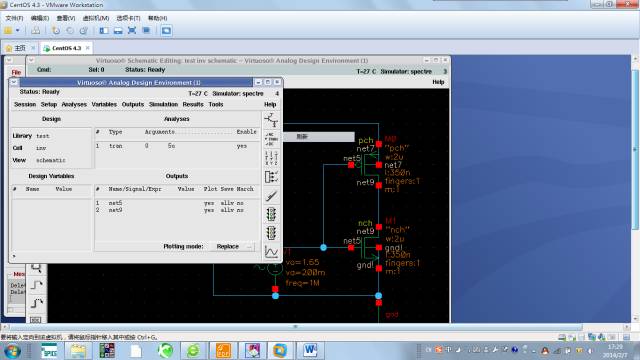

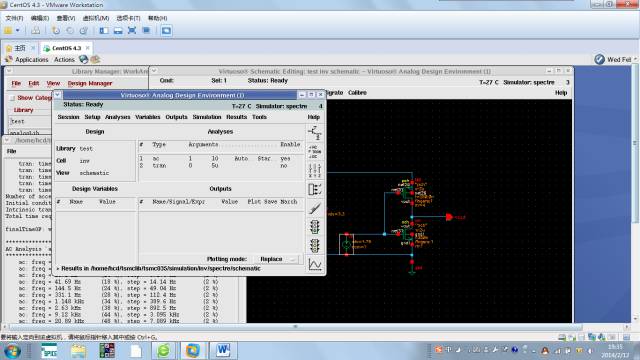

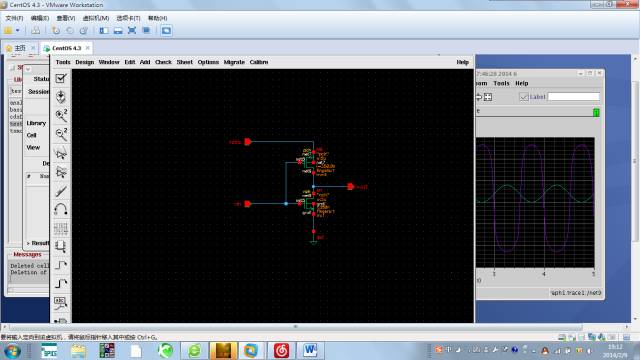

现在仿真窗口就变成这样了

一个是仿真方案是tran仿真,输出有两个节点。按下右下脚最后第三个按钮,有绿灯的那个按钮就可以仿真了。

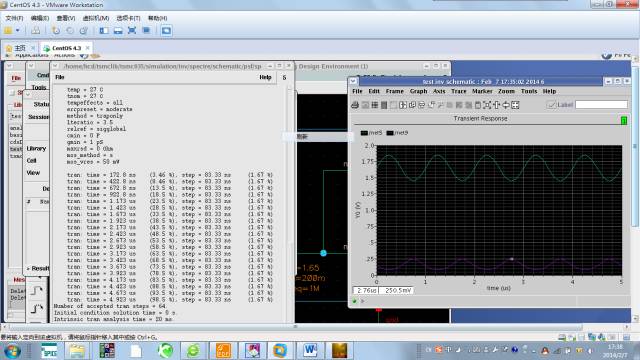

仿真出来有两个图,前一个类似hspice仿真后的lis文件。后面这个图是输出的结果图。

显然我们希望的反向器可定不可以这样。所以要再原来的电路改进下。

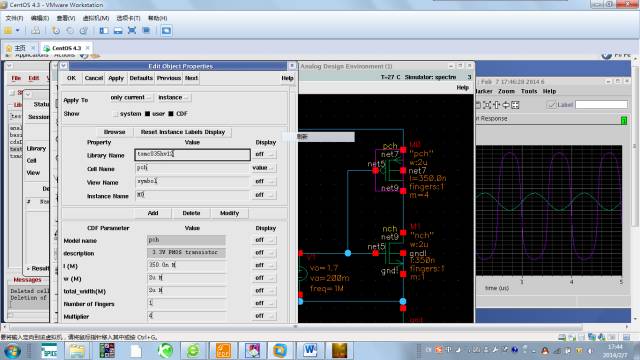

调整:M0管子要变动,Multiplier=4,这个就是并联的个数的意思。

V1的offset电压变成1.7.

再仿真,得出结果

这个是我们希望的反向器的结果。

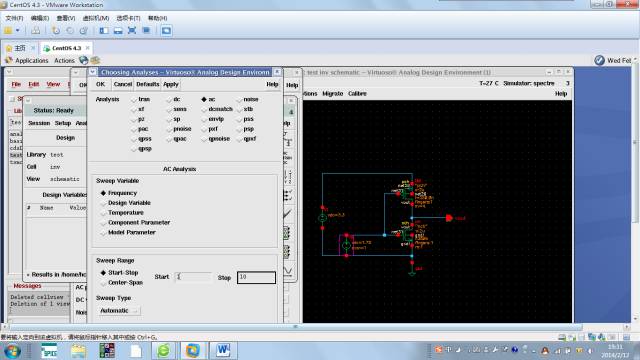

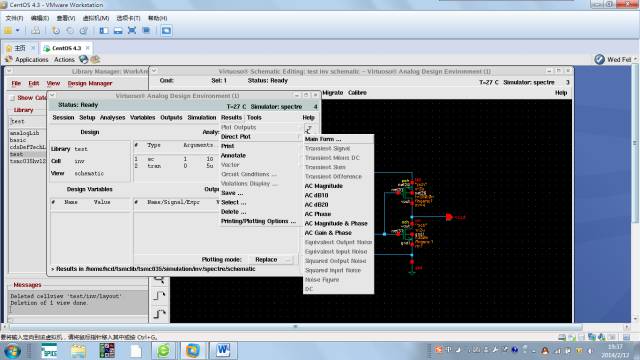

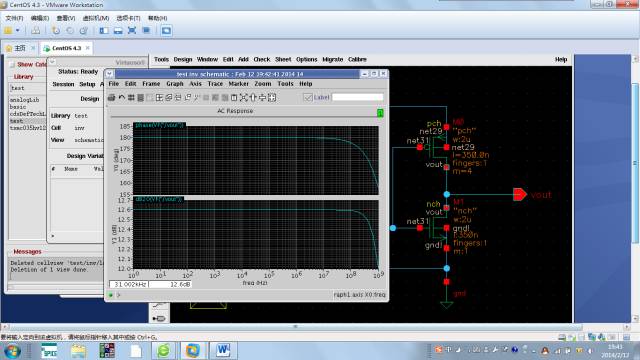

Ac仿真

仿真界面设置成如下图所示的 analyses->choose

仿真选ac,start =1hz,stop=1Ghz,hz可以不用写的

Tran仿真的enable选项不选择

最后整个界面成下图所示:

Ac 的enable 是yes的。Tran的enable是no。

点有绿色灯的按键进行仿真。

选择ac magnitude&phase,窗口自动弹到原理图界面,选择输出端口。

选择了就有了边框的颜色。

按esc键就可以看输出结果。

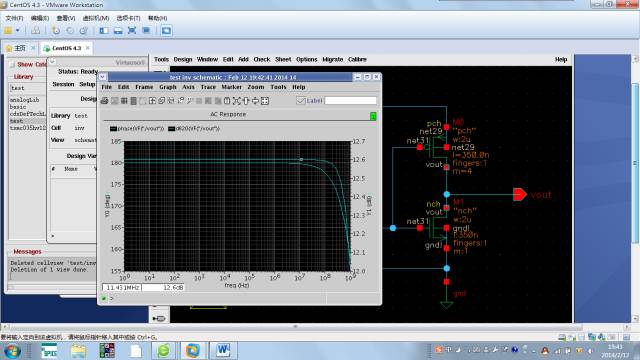

按图片上从左到右第4个按键是将相位和增益曲线分开。分开后如下图所示。

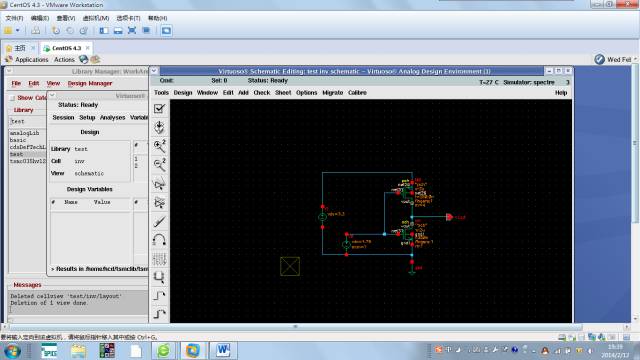

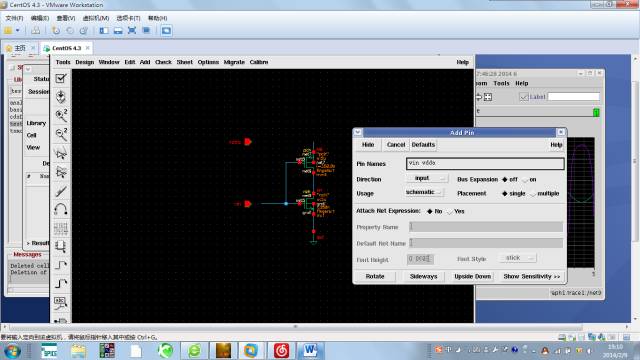

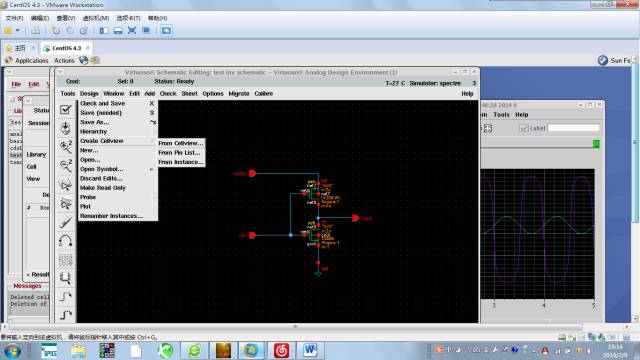

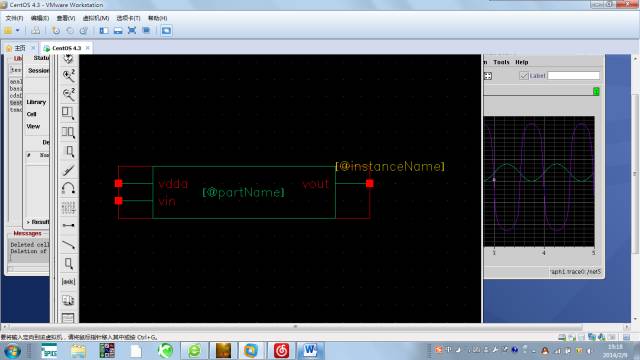

4.端口的添加和symbol的生成

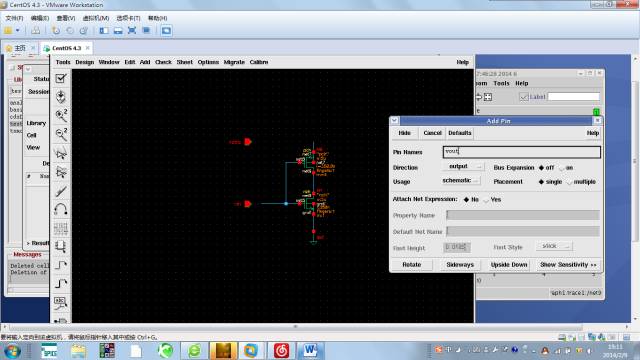

删掉信号源,按快捷键p添加端口(port)。需要三个端口,输入端口:vin,vdda;

输出端口:vout(电源端口)。

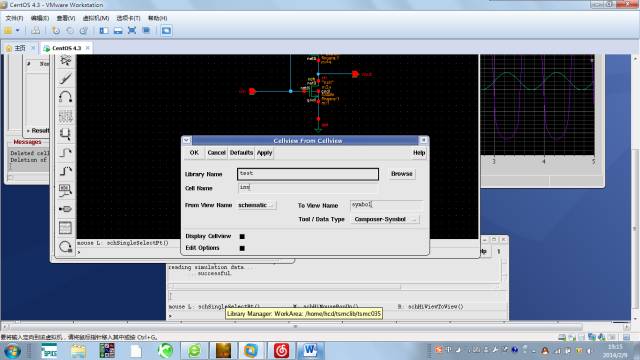

这样就完成了添加端口。之后是创建cellview。Design->create cellview->from pin list

选OK就可以了

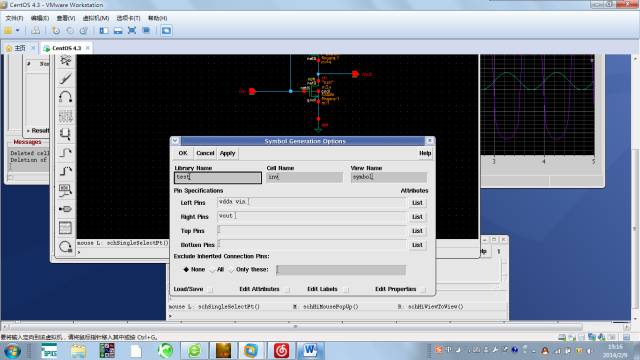

这里的端口可以随便放置,但一般的原则是输入在左边,输出在右边。点OK,得下图。

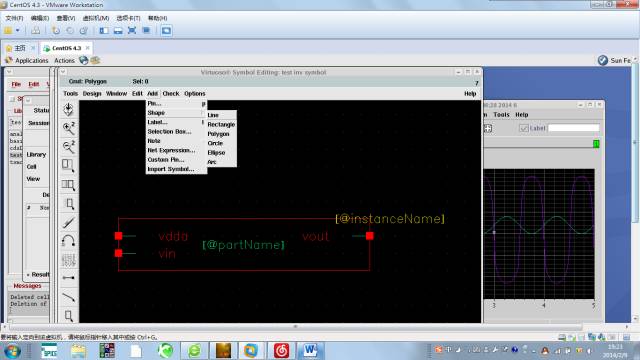

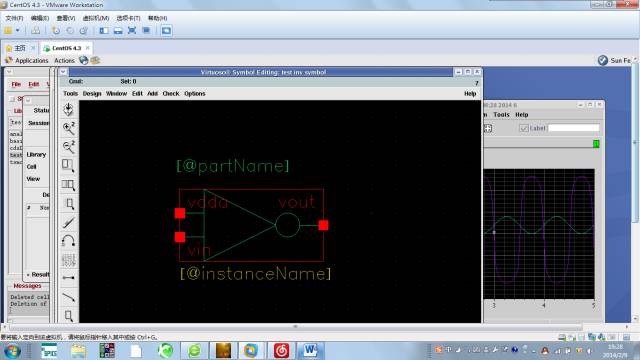

红色的框不可以删除的,绿色的框可以任意修改。

Add->shape->polygon可以画多边形,Add->shape->circle可以画圆

还有经常用的:选中一个图案后,按M键可以移动它。最后的样子

Partname和instancename可以随便放吧,尽量离图形近一点。

5.总结

电路设计也就是如何调节元件参数使得信号得到处理。

-

电路设计

+关注

关注

6678文章

2457浏览量

204828 -

Cadence

+关注

关注

65文章

926浏览量

142268

原文标题:cadence的简单操作流程

文章出处:【微信号:feifeijiehaha,微信公众号:电路和微电子考研】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

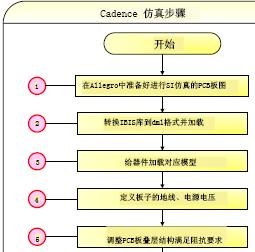

电源直流压降的的仿真操作流程

Cadence仿真流程

Giantec采用Cadence技术统一数字流程生产其混合信号芯片

Cadence提供新一代Encounter RTL-to-GDSII流程

华力微电子与Cadence共同宣布交付55纳米平台的参考设计流程

中芯国际采用Cadence数字流程 提升40纳米芯片设计能力

Cadence PCB封装制作流程

Cadence 数字、定制/模拟设计流程通过认证,Design IP 现已支持 Intel 16 FinFET 制程

cadence的操作流程

cadence的操作流程

评论